MPS | Driver IC 热阻模型

电子说

描述

一、热阻的定义及热阻网络模型

热量传递有三种形式,热传导,热对流和热辐射,芯片在Package内的热量传递主要是以热传导为主。

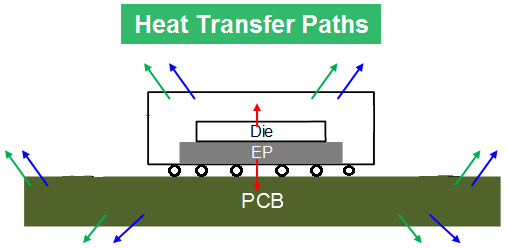

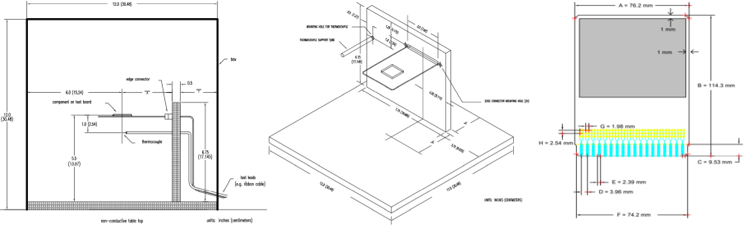

图1

以图1的QFN模型为例,IC中的die作为热源,上面有芯片最高温度结温TJ, 产生的热量传导至直接和die接触的case top 和PCB board,之后再从case top, PCB board 以热交换,热辐射形式传播至空气;

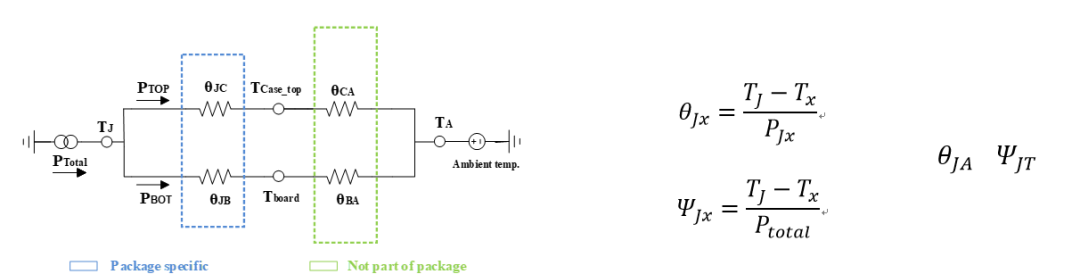

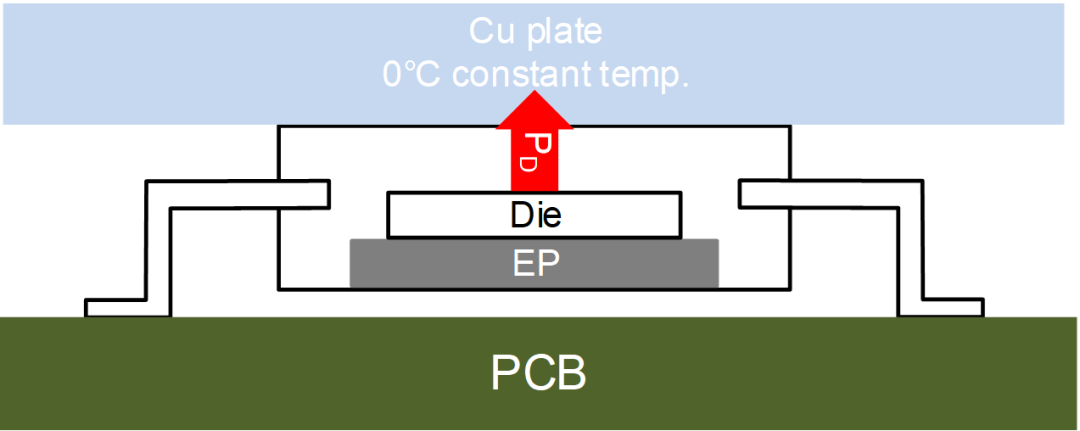

因此QFN对应的热阻模型可以简化成一个2R网络,四个热阻值,分别是θJC, θCA, θJB, θBA. 如图2;

图2

这里有两个细节:

1. 热阻θ的定义是两点之间的温度差除以对应流经这两点的功率,是一个有实际意义的物理量,θJC,θJB, 通常是由芯片封装决定的,无法改变;θCA, θBA通常是由芯片外围空间大小,空气对流情况,有无散热器,以及PCB layout 决定;

2. 在正常应用中,即芯片在PCB上自然对流情况下,芯片95%以上的热量都是通过PCB板走,即向下传导的功率占总功率的95%以上;

二、热阻的应用

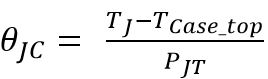

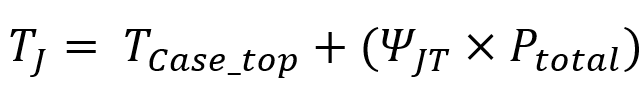

如图2,根据公式

因此

其中case的温度往往可以通过热电偶或者红外方便测出来,那么知道了结到壳的热阻θJC是否就能直接算出芯片Junction的温度呢?

答案是no,这里有个问题,根据热阻的定义,应用θJC算结温,乘的功率必须是流经case top 方向的功率,但是我们实际应用中无法定量得测出有多少功率从case top 走,又有多少的功率从PCB board走,我们只是定性得知道有95%的功率都是往PCB走;因此我们引入一个概念热特征参数ψ,热特征参数ψ的定义是两点之间的温度差除以总功率;

根据公式

得出

因此我们可以很方便地通过ψJT估算芯片的结温。

总结一下:

1.热阻θ是两点之间的温度差除以对应流经这两点的功率;

热阻θJA, θJC是用来评估不同芯片的thermal performance,而不是计算结温。不同芯片热阻的是通过统一的JESD51标准测得,方便一些系统级的工程师,在做系统级设计时,进行芯片之间的横向比较;

2.热特征参数ψ是两点之间的温度差除以总功率;

热特征参数ψJT的计算更接近于实际应用条件,因此计算芯片结温往往是通过数ψJT;

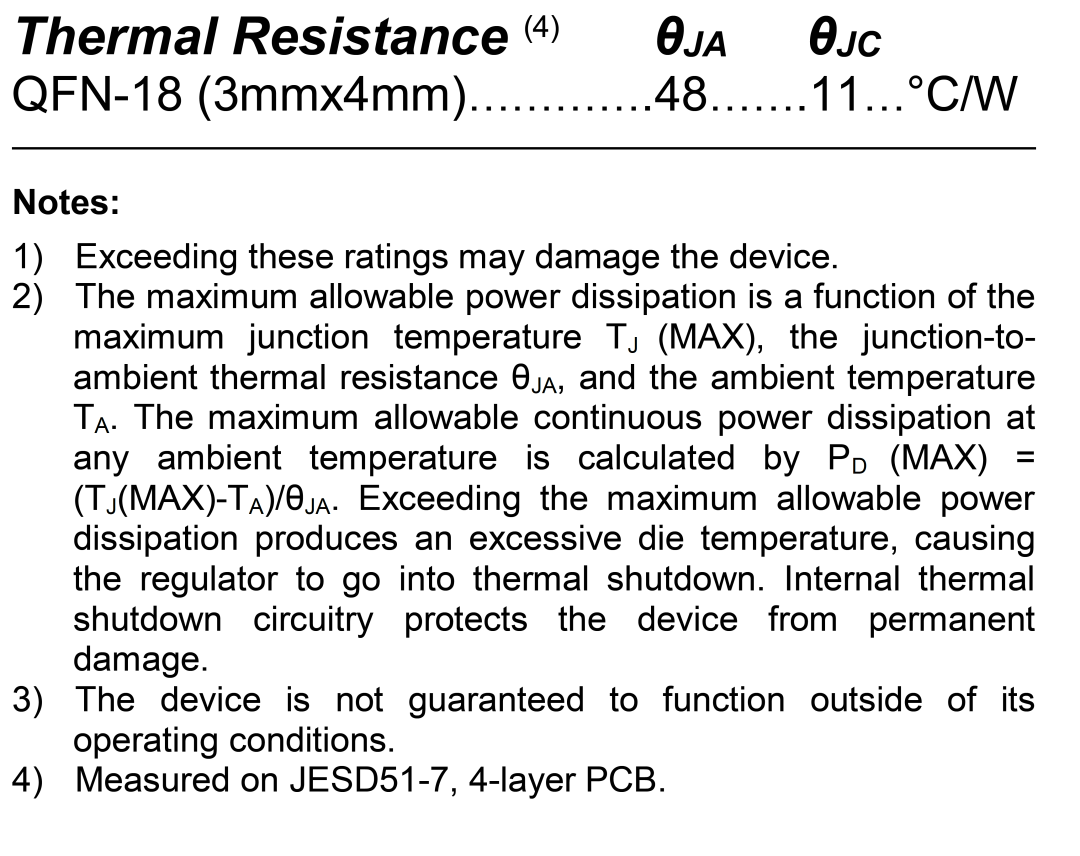

三、热阻的测试与计算

图3

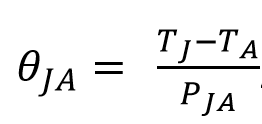

根据热阻计算公式:

计算热阻需要三个值,TJ,TA,PJA; 如图3芯片数据手册中提供的热阻值往往是通过JESD51标准下进行测量,下面简单介绍一下TJ,TA,PJA在JESD51热测试标准下的测试方法。

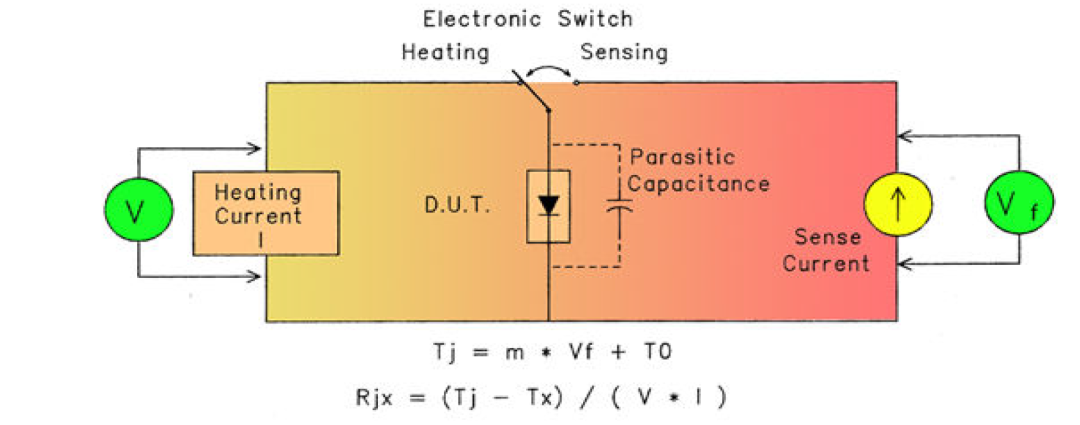

(1). 芯片结温TJ

图4

图5

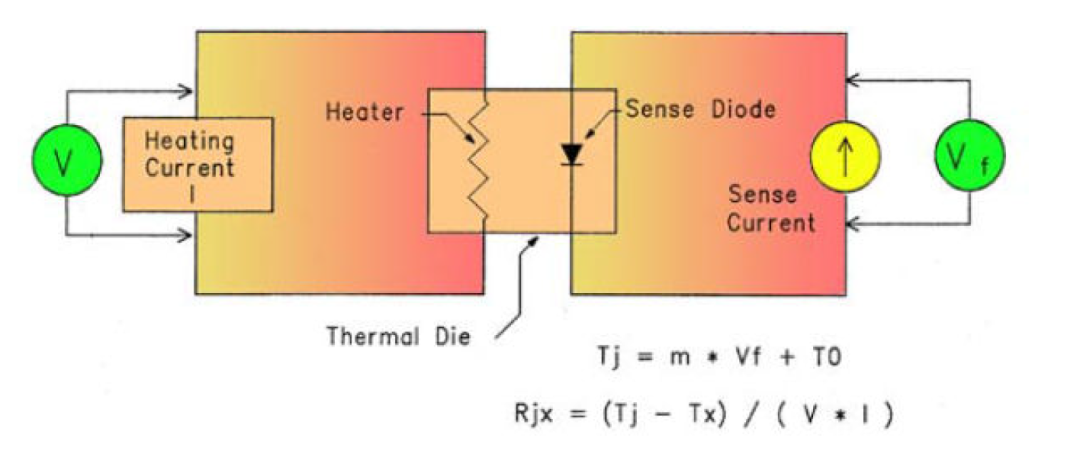

JESD51-1规定芯片结温的测试方法—用电压测温度,如图4,图5;

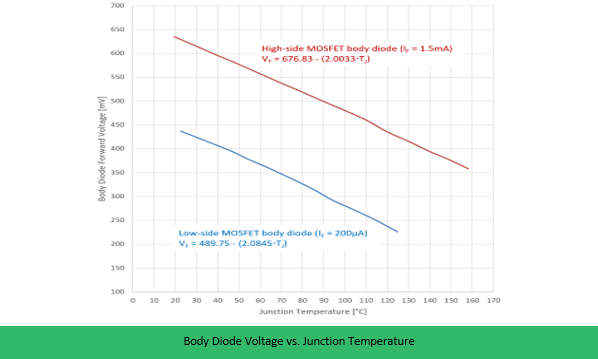

①测K系数:芯片中的MOSFET有寄生的体二极管body diode, 其压降和温度是强相关的。我们先选一个bode diode,通一个很小的bias 电流,大概200uA~10mA,把芯片放置恒温箱内,不断改变温度,记录不同温度对应的电压值。几组数据下来,能够绘制出一条电压vs.温度的曲线,曲线几乎是线性,其斜率即为K系数,也叫K因子。如下图6.

图6

②灌功率算结温;给芯片灌大电流,让其发热,对应body diode电压值也会随之变化,带入①曲线公式中,即可算出对应的结温;

图4,图5是两种测试方法,他们区别在于:图4测温度和灌功率,即bias小电流和功率大电流用的是同一个diode;

图5,测温度和灌功率分别用不同的diode。我们实际应用中,芯片在发热时,die上会有很大温度梯度,如果用不同位置的diode, 不管测温度的diode离灌功率的diode有多近,都会存在一定的温度分布差,造成测试结果偏小。

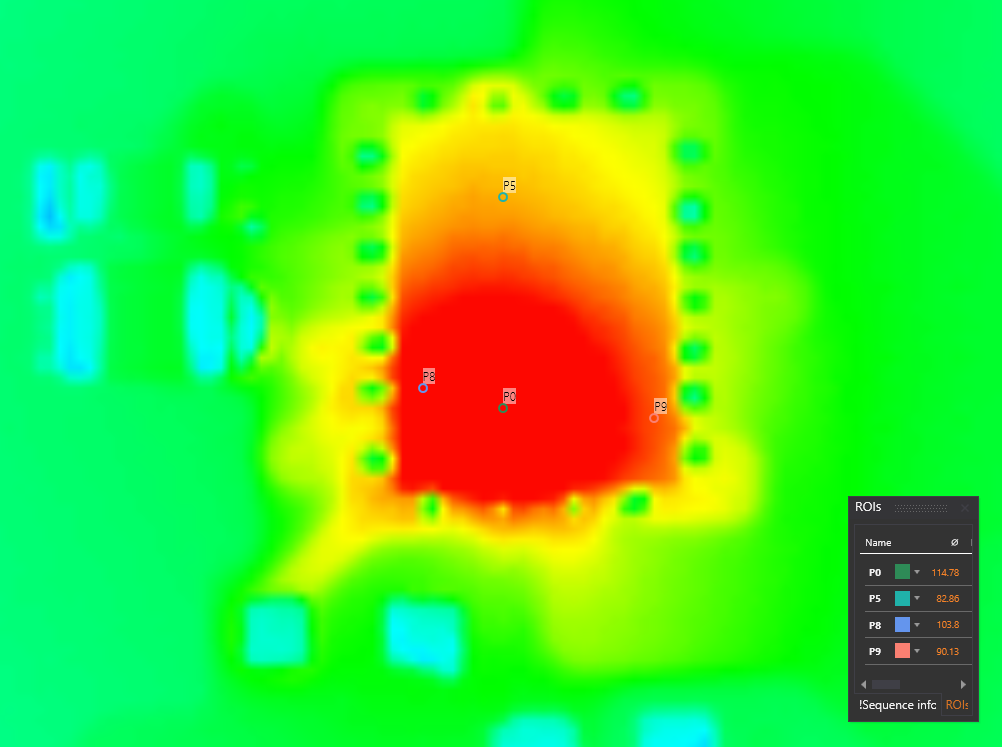

以MPQ6612A为例,(MPQ6612是一颗QFN3*4的全桥驱动)下图7是持续给MPQ6612AOUT1 LS 灌3.3W的功率,1000s后芯片的热成像图。P0是OUT1 LS diode的位置,即芯片最高结温的位置,如果另外选取其他位置如P5-OUT2 LS diode测温度作为结温,就会存在高达~30°C的测试误差。

图7

图4是目前的主流方法,也是精度最高的,即用同一个管子完成测温度和灌功率。

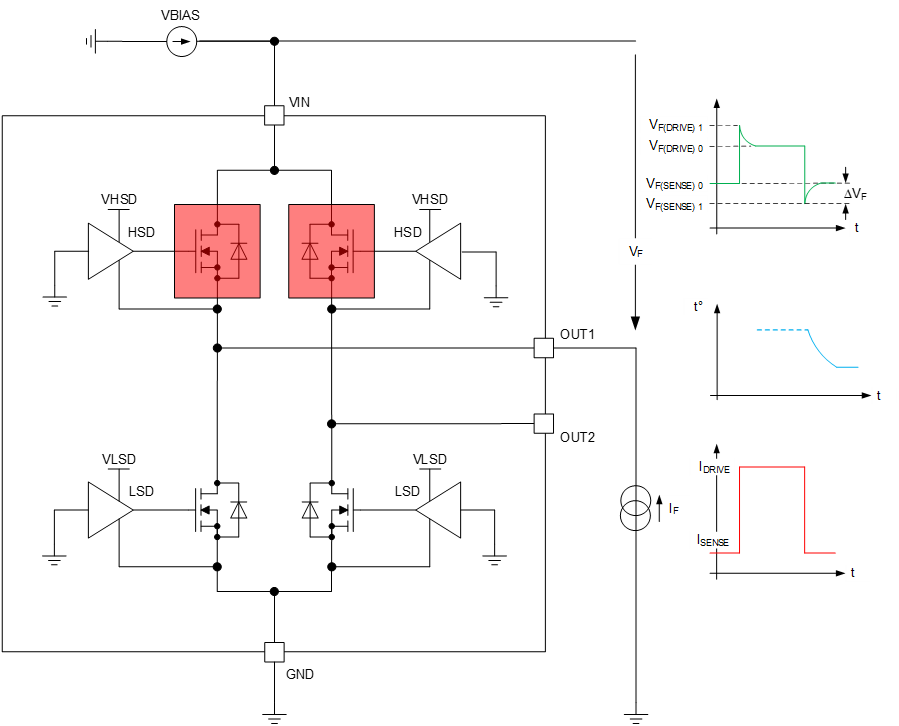

以MPQ6612A为例,图8:

图8

选取任意一个diode,先通bias小电流即Isense,测出K系数。之后通大电流灌功率即Idrive, 灌完功率后,迅速把电流切回Isense, 测出diode电压,根据K系数和diode电压可以测出一条降温曲线,在软件上对降温曲线进行反向拟合,校正切换瞬间噪声,可以得出灌完功率那一刻的温度值,即芯片最高结温。

选取同一个管子的测试结果精度虽高,但是对实验要求也很高。必须要让电流切换瞬间非常快,所以热阻测试有专门的测试仪器T3ster,它的量测时间短至1us,即灌完功率后1us的时间,传感器就能读到小电流下的电压值。

除了这两种方法测结温,还有比较常规的OTP法,很多芯片都有thermal sensor的单元,我们可以通过触发OTP的threshold来作为结温测试热阻,但是这个方法和用不同管子电压值测温度一样,在die里面thermal sensor 和灌功率单位的位置也是有温度分布差的,因此会有很大的误差。

(2). 芯片环境温度TA

JESD51同时也规定了芯片测试环境等一系列要求,如图9,空气是自然对流还是强制对流,测试板的layout,2s2p还是1s0p等等。大致了解下即可。

图9

(3). 芯片功率方向的唯一性

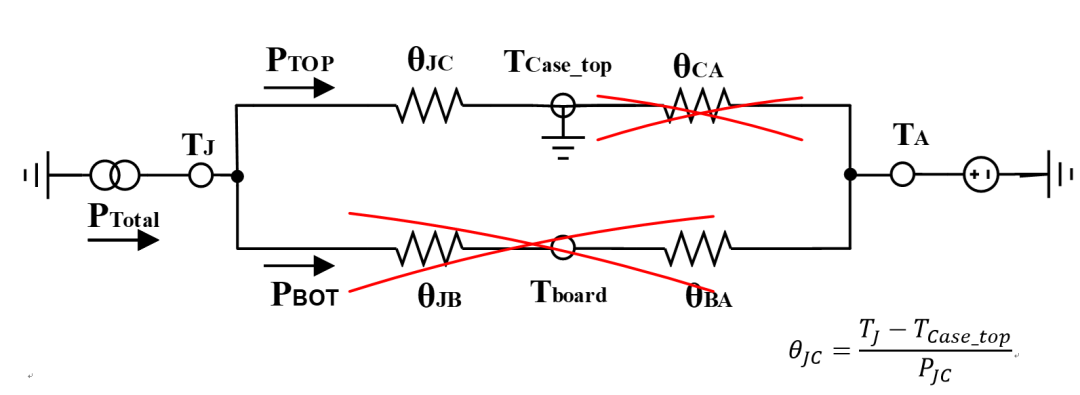

上面讲到,两点之间的热阻是对应两点之间的功率,因此我们在测试不同热阻时,需要保证芯片功率方向唯一性,以下图10 θJC为例。

图10

芯片正常应用中是有上下两个散热方向即junction to case(top), junction to board。如果要测试θJC,需要保证芯片全部功耗往case top方向走,可以通过对其他散热方向进行绝热处理。(找元器件现货上唯样商城)实验中可以让芯片四周和底部用绝热泡沫夹住,顶部用冷水板保持恒温。仿真可以直接在case top 设置一个温度点,譬如接地。

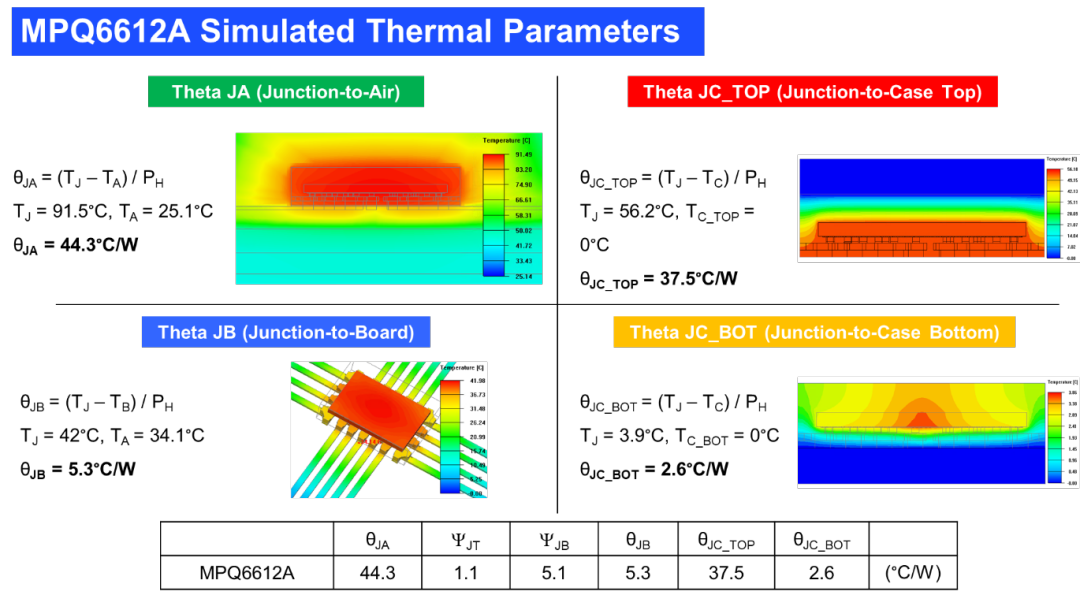

解决了JESD51标准下TJ,TA,功率方向唯一性的测试方法后,我们来看一下MPQ6612A热仿真测试结果。

图11

上图11是MPQ6612A基于JESD51标准的热阻仿真结果。其中值得一提的是,θJB测试中,能看到芯片pin走线是非常宽的,远大于正常应用,这是因为热阻测试的标准是JESD51,它往往模拟的是PCB layout 很差的情况。因此我们在正常应用中,标准EVB上测试的热阻值或者是热特征参数要比JESD51标准下好很多。

四、瞬态热阻-热阻抗

现在很多芯片在启停的时候,会有比较大的电流冲击,瞬态的功率可能是稳态功率的几十倍,因此瞬态结温的高低是越来越多客户关心的问题。前面提到的热阻模型都是基于稳态下,那么研究瞬态,该构建怎么样的散热模型呢?

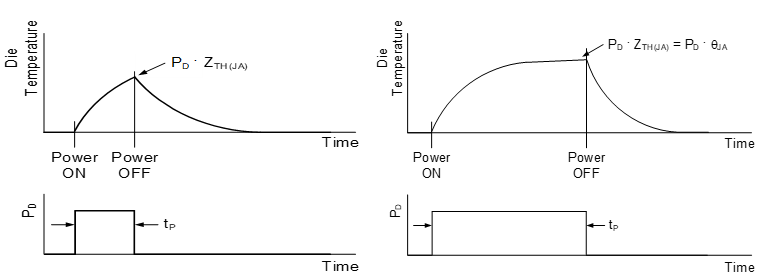

瞬态热阻,即热阻抗Zth。如图12,热阻抗是热阻值随功率pulse脉宽变化的函数,当时间足够长时,系统达到稳态,这时候的热阻抗就等于热阻。

图12

那么如何测试瞬态热阻抗?即瞬态功率下对应的结温呢?

我们来看一下基于MPQ6612A的瞬态热阻抗测试方法和结果。

思路和前面测稳态时一样,选取一个管子测温度和灌功率,但是我们可以通过改变power pulse 的脉宽,测出一个不同power pulse 脉宽下对应的结温,进而得出对应的热阻,绘制曲线即为热阻抗。

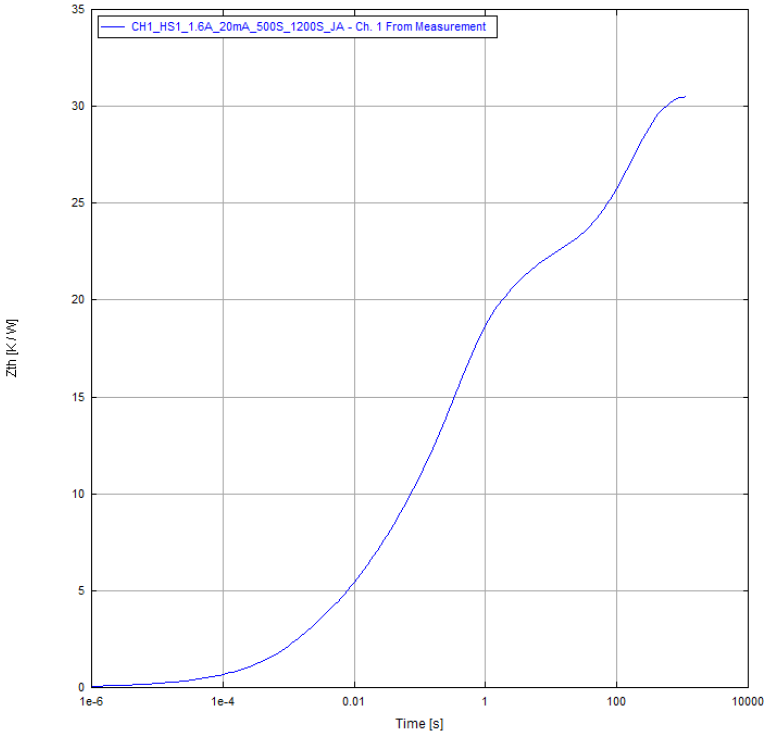

图13

图13是MPQ6612在标准EVB上用T3ster的热阻抗测试结果。横坐标是power pulse的脉宽,纵坐标是对应的瞬态结到环境温度的热阻Zth。

从图中,不难发现这里有两个有趣的现象:

1. 脉宽达到1000s以后,热阻抗几乎不变,即系统达到稳态,这时候热阻抗等于稳态热阻, 即~30°C/W ,比前面热仿真RθJA热阻值44°C/W 要小很多,这是因为30°C/W 是基于标准EVB的测试结果,而44°C/W 是基于JESD51标准的测试结果,JESD51 测试板往往模拟的是PCB布局很差的情况。

2. 热阻抗曲线,有明显两个拐点,分别是1s,100s。这是因为1s以前芯片热量还没有传递至package表面,热量还在内部,所以对应1s以前的热阻抗就非常低。而100s大概是芯片热量均匀传递至PCB的时间点。0-1s是Package level, 1s-100s是PCB level, 100s-1000s 是system level即稳态。

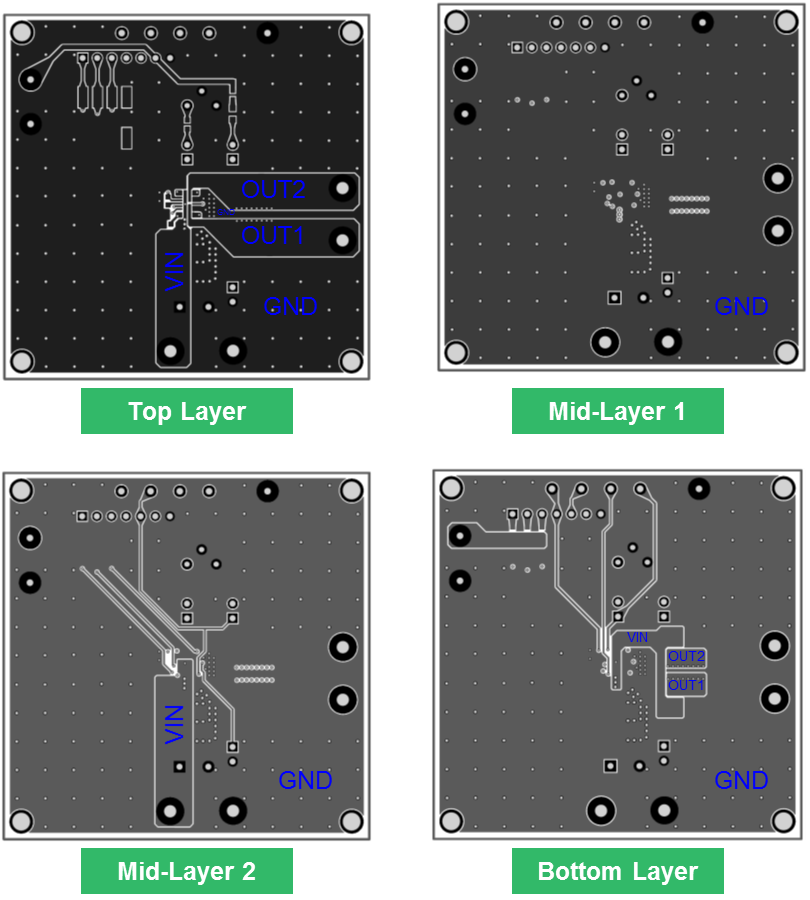

五、PCB Layout Tips

前面提到正常应用中,芯片95%的热都是通过PCB散热,因此PCB合理的layout能够更好地提高芯片的thermal performance。下面是几个tips。

图14 MPQ6612A: 4-Layer Evaluation Board

1. 走大功率的环路布铜面积要大,布铜率要高。

2. 对散热有更高要求可以用四层板。

3. 选PCB基板的时候,尽可能多用铜箔,少用FR4

4. 靠近IC或者是功率走线,多打过孔,一个常规尺寸的过孔热阻值也有100°C/W。

审核编辑 黄宇

-

有什么方法可以降低IC封装的热阻吗?求解2021-06-23 1956

-

电机中的热阻网络模型该怎么建立2021-08-30 2173

-

IC封装热阻的定义与量测技术2010-07-04 850

-

基于双热阻模型芯片封装的强制对流换热仿真案例2017-12-19 55322

-

如何用T3Ster测试IC的热特性2023-04-03 10478

-

【工程师笔记】Driver IC 热阻模型概述与计算2023-09-13 3134

-

MPS | Driver IC 热阻模型概述与计算2023-10-10 1894

-

基于RC热阻SPICE模型的GaNPX®和PDFN封装的热特性建模2025-03-11 1907

全部0条评论

快来发表一下你的评论吧 !