恩智浦MCU解析 MCX A系列微处理器之系统架构

控制/MCU

描述

全新的MCX A系列融合了恩智浦通用MCU的特点,适用更为广泛的通用应用,实现了低成本,低功耗,高安全性和高可靠性。

MCXA153是MCX A系列的第一款产品,已于2024年1月份上市,为低成本入门MCU应用提供了丰富的功能和特性。后续MCX A系列还会继续推出新产品,为客户提供持续的硬件和软件的可扩展升级路径。

今天,我们一起来了解一下MCX A最新产品的系统架构。

MCX A153的系统架构:

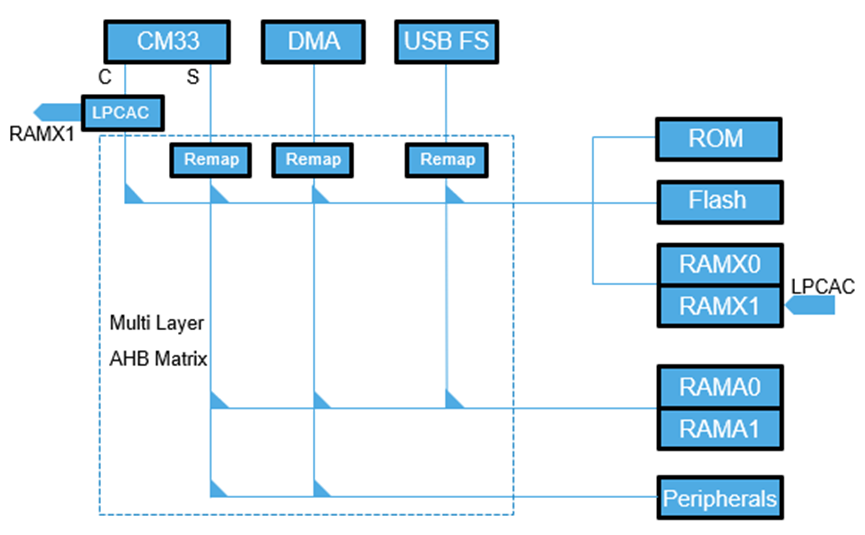

可以从上图看到,MCXA的总线架构是相对简单。主要有三个总线的发起者,分别是CM33, DMA和USB full speed。对应的总线target 分别是ROM, Flash, RAMX, 它们共享code bus接口,而RAM A0和A1共享systembus的接口,另外还有一个专门的总线接口,去访问外设。

对于CM33来说,它主要使用codebus来取指令,system bus取数据,code bus能够访问的地址空间是有限的,在MCXA产品中,CM33从codebus只能访问到ROM,Flash,RAM X0和X1,具体的地址分配可以参考芯片手册中的memory map表格。System bus是不能访问ROM,Flash和RAM X0/X1,它可以访问RAM A0, A1和外设。对于DMA,它可以访问所有的外设空间。对于USB FS,它只可以访问系统的内存空间,不能访问外设。

在MCXA的总线架构图中,可以看到Remap的结构,其作用主要是将RAM X0的地址空间重新映射到RAM A1的后面,这样可以形成多达32KB的连续RAM空间,满足一些应用对连续RAM空间的要求。

对于CM33,在code bus上配置了一个4 KB Cache,用于加速对Flash的访问。因为Flash本身的访问速度是有限制的,对于MCXA 96MHz的core clock,在没有打开Cache的情况下, 需要2个等待周期,即32MHz的Flash访问速度。在打开Cache后,一旦要访问的内容被Cache命中,CM3可以0等待周期访问,大大增加系统性能。同时通过Cache来访问指令,可以减少系统的功耗。

今天给大家介绍了MCX A153的系统架构,后续会有更多的特性介绍助力大家对MCX A系列有个快速而全面的了解, 敬请期待!

-

恩智浦MCX A系列微处理器之供电系统2024-06-13 2490

-

恩智浦MCU解读 MCX A系列微处理器之时钟架构2024-06-20 1326

-

为何恩智浦MCX C系列MCU值得青睐?2024-08-02 6106

-

恩智浦eIQ® Neutron神经处理单元2023-02-17 1000

-

恩智浦推出MCX A14x和MCX A15x系列MCU2024-02-01 2989

-

恩智浦发布新一代MCX A系列MCU2024-02-02 2621

-

恩智浦推出新一代MCX A系列MCU2024-02-03 2543

-

富昌电子推荐两款恩智浦的MCX A和MCX N系列微控制器2024-05-09 2389

-

恩智浦MCX W系列无线MCU的独特魅力2024-08-27 3657

-

基于恩智浦MCX N系列MCU的应用示例2024-10-25 3631

-

恩智浦MCX L系列超低功耗MCU概述2025-01-17 3209

-

恩智浦MCX L系列MCU的低功耗设计2025-02-14 4882

-

恩智浦MCX E系列5V MCU发布2025-08-16 5274

-

恩智浦推出基于MCX A34系列MCU的电感式编码器方案2026-02-10 1769

-

恩智浦MCX E31系列微控制器深度解析2026-02-27 1667

全部0条评论

快来发表一下你的评论吧 !