确保USB3.0电路可靠性 选对PTC/ESD方案是关键

接口/时钟/PLL

描述

USB 3.0传输速率高达5Gbit/s,且电源汇流排也有高达900毫安培的最大输出电流,因此电路电气瞬变和过流故障的预防极为重要,设计人员必须慎选适当的热敏电阻(PTC)和静电放电(ESD)方案,才能确保讯号完整性,并降低系统故障风险。

通用序列汇流排(USB)规范自1996年发布以来,截至2012年为止已累积超过三十五亿个电脑周边设备的USB连接装置出货量。2010年,当第一批支援USB 3.0规格的装置上市,销售量就达到约一百万个,2012年更一举增长至五百万个左右,足见其市场成长相当迅速。

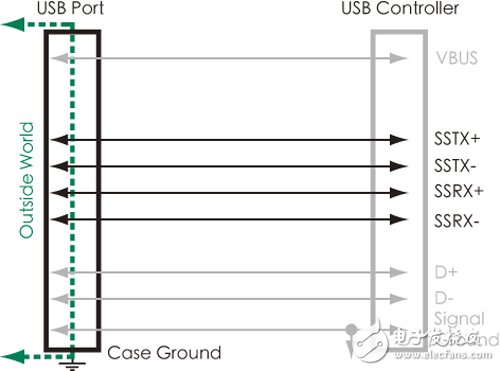

相较于USB 2.0,USB 3.0拥有四个额外数据通道,传输速率高达5Gbit/s(图1),而且电源汇流排也有高达900毫安培(mA)的最大输出电流,这些新规格加上晶片尺寸不断缩小,使得预防电路电气瞬变和过流故障的问题变得更加重要且复杂,因为高速传输下,即使只是很小的静电放电(ESD)和短路事故,都将为系统带来严重危害。

图1 USB 3.0增加双差分数据对,藉以达成5Gbit/s高速传输速率。

由于晶片灵敏度、讯号完整性和系统可靠性都是系统设计人员非常关注的事情,因此USB 3.0系统上的寄生电容、低箝位电压和低电阻都成为电路保护元件选择的关键指标。由于USB 3.0电源线可允许更大电流通过,电流保护器可有较低的电阻,在确保低压降方面也变得至关重要。一项成功设计的关键是要掌握保护技术,如热敏电阻 (PTC)、压敏电阻和ESD方案等,本文将详细解释须考虑的设计因素。

USB 3.0飙高速 电路保护挑战更艰钜

USB 2.0到USB 3.0最重要的物理变化是引进SSRX+/SSRX和SSTx+/SSTx两个差分数据,并维持和现有D-/D+资料汇流排并列运行的模式,这允许资料全双工同时传输,改进USB 2.0汇流排只能单个双工传输的问题。此外,USB 3.0还将电源汇流排上的电流从500毫安培增加到900毫安培,扩增外部设备供电的选择,不再需要额外电源配套方案。

由于USB 3.0引进额外的差分数据,引发更多ESD防护需求,过去以分离元件保护每个单独资料线的方式已不足以保护其电路,工程师面临的挑战是要找到更好的ESD 和电压瞬态保护方案,使敏感性资料线在没有增加讯号畸变电容的情况下也能得以保护。现阶段,业界大多采直接放在资料对中的新半导体阵列ESD保护装置,同时保护传统USB 2.0资料线,以及USB 3.0额外的资料线。

与此同时,USB 3.0规范第11.4.1.1.1中规定,为安全起见,主机和所有自供电集线器须实现过电流保护,该集线器须检测过电流情况,并将其报告至USB控制软体。过电流限制机制须在毋须用户干预的前提下自行复位,聚合物PTC和固态开关就可用于过电流限制的方法之一。

根据UL60950-1标准要求,USB 3.0可能还需要其他过电流保护功能,USB汇流排收发器晶片或电源管理晶片虽已提供部分电流限制功能,但是当晶片不包含电流限制或附加保护功能时,电路设计人员须为电源汇流排设计电流限制PTC。

在电源汇流排上安装聚合物PTC可在短路的情况下限制电流,并防止由突然的短路引起的过电流损坏,还可帮助实现UL60950-1标准中第2.5节(有限电源,表2B)的规定,限制短路电流在5秒内小于8安培。

相关的USB集线器应用程式和USB 3.0的过电流保护规范如11.4.1.1.1条中陈述,如果下行埠的总电流超过预定值时,过电流保护电路可消除或减少所受影响的下行埠功率。预设值不能超过5安培,且须足够大于所允许的最大埠电流或时间延迟的瞬态电流(例如开机、动态连接或重新配置时),达成过电流保护。

肩负USB 3.0埠保护重任 PTC选用规格大有学问

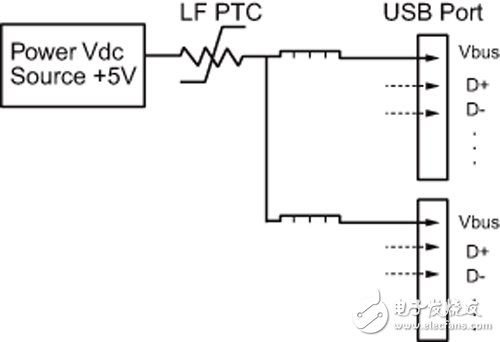

图2所示为用于多埠集线器配置的PTC解决方案,表1则显示推荐的单一埠和两个埠中联动的PTC元件,并针对新的USB电池充电规范1.2版列出所需的PTC方案。

图2 USB 3.0多埠集线器配置架构图

在选择PTC做为USB埠保护时,还须考虑几个关键参数,包括最大电流须支援900毫安培、PTC位置的工作温度、触发速度和直流电阻等。表1中所有PTC都能保护最大电流为900毫安培的USB 3.0埠,就算最高工作温达60℃也不会跳闸。

由于温度变化急剧可能使PTC的触发速率下降,所以这也是PTC选择过程中的一个重要方面,设计师选择PTC时应考虑不相容的USB 3.0设备,且负载900毫安培电流的情况,使PTC在最高工作温度下有超过900毫安培的最大可用电流,否则,PTC可能会错误触发。

每个PTC也要在电流8安培的时候,以小于5秒的速度进行短路故障触发,因此符合UL60950-1有限电源规范以及把USB 3.0规范中电流限制在5安培是很重要的。

选择最合适的PTC最后的关键参数是直流电阻。由于USB 3.0现在提供最大电流为900毫安培,所以电路中的功耗须进一步降低,此外,电源汇流排两端元件的电压降也须缩小,特别当是该电路电阻预算很吃紧的时候。

整体而言,选择PTC的主要目标是确保电流设备在最高温度下能承受至少900毫安培电流。以设定60℃为最糟糕的设计温度情况为例,单埠应用应选择最小尺寸且可支持最大所需电流0.95安培的方案,如表1中的第一个方案。若使用一个PTC保护两个USB 3.0埠,表1中第三个方案是一个不错的选择,因为它在60℃时可保持2.19安培电流,满足各方面的安全考虑。

增强USB 3.0电路保护 外挂ESD元件势在必行

USB 3.0增加的资料线因提供更多电气瞬变的可能入口通道,也将承受更大的ESD威胁。尽管现代晶片往往都有受到一定程度的ESD自我保护功能(通常在500~2kV的范围内),但对USB 3.0电路而言仍是不足的,因此须导入额外的ESD保护元件。

静电防护水准的等级系根据有1,500欧姆(Ω)放电电阻的MIL-STD HBM模型分级。MIL-STD模型中,以一个2kV的脉冲相当于有着330欧姆放电电阻,且电压为500伏特的IEC 61000-4-2模型为基础(图3),目前人体放电模式(HBM)可用脉冲在相同的瞬态电压是IEC模型可用的四分之一。发生静电放电事故时,电压往往高达15kV甚至更高,将导致软体故障、电路潜在损害或灾难性故障,因此,额外的ESD保护是提高现代介面埠生存能力的必要条件。

图3 IEC 61000-4-2 ESD电流波形

为确定外部ESD事故预防系统,业界已开发出几个测试标准,其中,IEC 61000-4-2条款受到最广泛的认可;该标准定义ESD在不同的环境和安装条件中的测试规范,如今的USB 3.0埠在此规范下,须承受至少8kV接触放电,达到IEC 61000-4-2条款第四级的要求。

USB 3.0拥有更高的资料速率,就特别须要注意元件的电流容量以保护电路,且系统设计人员在选择ESD保护元件时也须留意许多重要参数,包括动态电阻、箝位元电压、击穿电压、寄生电容、最大ESD能力、多脉冲能力、封装形状、关断状态的阻抗或泄漏电流、设备电路配置和布局的灵活性等。

现阶段,市场上有几种不同的防静电抑制技术,例如多层陶瓷压敏电阻(MLV),聚合物ESD抑制器和半导体的ESD抑制技术,是否选择正确的元件将决定USB 3.0埠的设计可靠度。由于ESD保护元件的电容、箝位元电压和动态电阻最为重要,一些保护元件制造商已实现以最小寄生电容提高讯号完整性的产品,同时有些产品的箝位元性能也达到最大化,但代价是电容很高。

举例来说,瞬态电压抑制(TVS)二极体和二极体阵列有较低的动态电阻,提供卓越的箝位元性能,并能保持非常低寄生封装电容。图4显示矽方案的箝位元性能与MLV ESD保护技术的比较,以矽为基础的解决方案的箝位元电压更低。

图4 矽电阻与压敏电阻的箝位元性能比较

TVS二极体阵列提供多通道ESD保护解决方案(图5),成为目前USB 3.0保护的最佳选择。该类元件能吸收瞬态电流,并泻放电流,同时透过雪崩或齐纳二极体箝制电压位准。如图6所示为USB 3.0静电保护方案架构图。

图5 保护USB 3.0电路的TVS二极体阵列示意图

图6 上为USB 3.0静电保护方案架构图;

USB 3.0电路保护元件对维护资料完整性也非常重要,任何附加电容都可导致讯号失真,并降低讯号的可靠性。测试静电抑制器的寄生电容对讯号完整性影响的主要方法是进行眼图测试,此测试须重复采样数位讯号,并在示波器上显示出眼图,用来定义可接受的讯号品质和依从性。

-

面向USB3.0的新型ESD防护设计2023-10-08 624

-

USB3.0接口保护ESD应用2021-09-03 5074

-

USB3.0接口ESD静电防护方案的特点是什么2020-12-02 1866

-

USB3.0接口的ESD防护设计2020-10-27 1263

-

关于USB3.0的电路保护方案2020-01-16 6547

-

USB3.0系统的ESD防护设计方案2019-11-25 4502

-

克服USB 3.0挑战:智能设计确保高速信号的完整性2018-12-12 5871

-

适用于USB3.0接口的新电路保护方法2017-05-17 3535

-

USB3.0静电放电防护解决方案2015-04-28 7769

-

USB3.0中ESD应用的五大要素2014-01-06 2905

-

适用于USB3.0接口的新电路保护方案2013-11-05 2753

-

自恢复保险丝在USB3.0接口的保护应用2013-10-29 3182

-

USB3.0接口的新电路保护方案2012-10-24 3300

-

USB3.0接口电路实现方案2012-08-20 13038

全部0条评论

快来发表一下你的评论吧 !