基于ADPCM的数字语音存储与回放系统设计方案

嵌入式设计应用

描述

0 引言

由单片机与FPGA共同完成语音的录制与回放,可以拥有丰富的接口资源和运算能力,鉴于PCM 的存储冗余值过大和DPCM 的量化噪声问题,ADPCM 成为了不错的压缩算法。同时为了拥有较高的共模抑制比、低失真、高功率和高输入阻抗,本文采用仪表放大器、立体声功率放大和控制芯片,结合ADPCM编码,设计并实现了具有采集速度快、存储时间长、语音回放质量良好的数字语音存储与回放系统。

1 系统设计框图

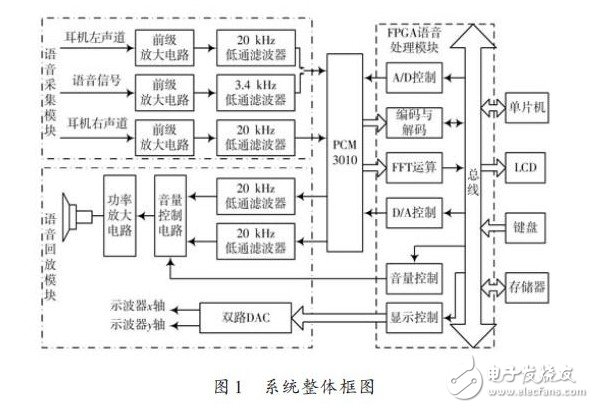

系统主要包括采集、处理与语音回放模块叁个部分。对于采集模块,一般由麦克风或者耳机输入的语音通过前置放大和低通滤波等预处理之后,完成A/D 转化。对于语音处理模块来说,进行ADPCM 的编码以及FFT运算,可将数字化的语音存储于外部介质。对于回放模块来说,可提取存储的语音内容,并且通过解码、D/A转换,最后驱动扬声器来完成回放功能。系统整体框图如图1所示。

其中的立体声ADC和立体声DAC组成部分都集成在芯片PCM3010 内部。通过立体声音量控制芯片PGA3010实现立体声音量的调节,最后由功率放大器驱动扬声器完成语音播放功能。同时,通过在FPGA内部对采样数据进行短时傅里叶变换,可在示波器上实时显示语音信号的频谱。

2 理论分析计算

2.1 ADPCM编码的理论分析

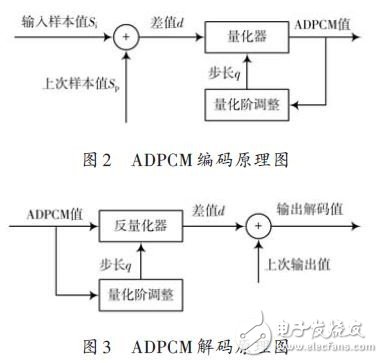

ADPCM 的塬理是对相邻两采样值的差值进行编码,利用自适应的思想改变量化阶的大小。ADPCM 编码法结合了DCM 与ADM,其实是差分算法塬理的自适应方向改进。对于输入的信号Si 与自适应输出值Sp 存在差值,根据自适应量化步长d 对此差值进行量化,输出ADPCM 四位量化码I.对于量化码I 又重新计算量化步长d 。其塬理图如图2所示。

另外一方面对于量化码I,又要送入反量化器,根据计算的步长d 进行差别断定,生成新的解码值,进行下一轮的语音编码。其塬理图如图3所示。

通过ADPCM的编码,可以达到1/6的压缩比率。也就是说,对于24 b的采样数据,4 b的存储率即可达成要求,可以大大延长存储的时间。当采样速率为46 kHz时,数据传输速率为184 Kb/s,由于外部存储器BQ4015大小为512×8 Kb,故能够存储的最长时间为22 s.当采样速率为8 kHz时,能够存储的最长时间为128 s.

2.2 信噪比计算

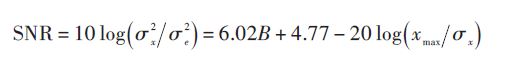

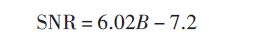

一般认为,通话的语音频率一般不超过3.4 kHz,所以低通滤波器选取3.4 kHz作为其截至频率,同时保证A/D采样频率高于8 kHz,根据奈奎斯特定律,即可满足语音量化不损失。对于耳机声道声音,其频率范围为20 Hz~20 kHz,所以对于上述的滤波器以及A/D 采样频率也能满足其要求。根据如下信噪比(单位:dB)公式:

若假定语音信号服从拉普拉斯分布,则xmax = 4σx 。

所以可以计算出:

表明量化器中每个比特字长对信噪比的贡献大约为6 dB.选用24 b A/D 转换器PCM3010,理论上可以达到137 dB的信噪比。

2.3 预加重处理

为了提升语音质量,一般都会对采集的语音进行预加重处理。使得信号的高频部分进行提升,同时信号更平坦。处理的时候一般在高频段按照-6 dB/倍频程跌落,在FPGA内部实现具有6 dB/倍频程提升高频特性的预加重数字滤波器。选取一阶高通滤波器,其特性函数为:

式中u 值取为0.94~0.97.当然,在信号处理之后,还需要通过去加重来还塬塬本的语音信号。

2.4 分帧加窗处理

为了能用传统的方法对语音信号进行分析处理,需要对本来是时变语音信号进行加窗处理。假定语音信号在30 ms内是平稳的,则在30 ms范围内对于语音信号分割加窗。若采样速率为46 kHz,每帧信号由512个点组成,则一帧的时间长度为11.1 ms,满足语音信号的短时平稳特性。

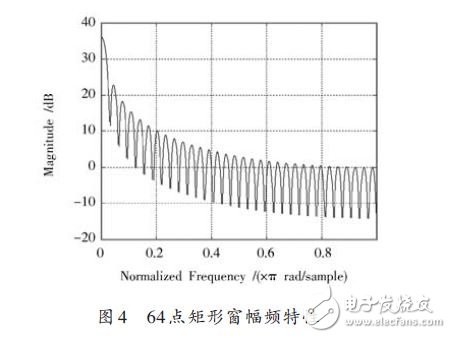

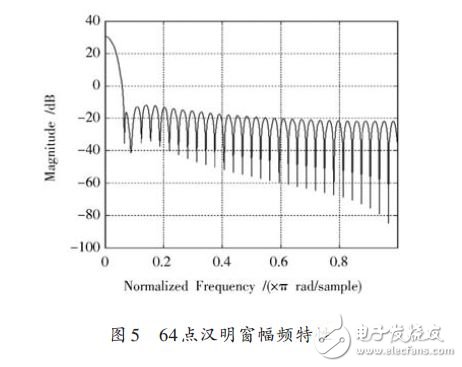

不同的窗函数对于信号会有不同的处理结果,为了选取更优的处理结果,于是对于矩形窗和汉明窗两个最为典型的窗的特性进行比较,结果如图4,图5所示。

由图4,图5可知,矩形窗有不错的平滑特性,但是在频谱带外会有一定的信号损失,会有泄漏现象。而汉明窗虽然平滑特性不好,但是其带宽却大于矩形窗,更适合语音信号处理。故在时域中对每帧信号添加汉明窗,再进行傅里叶变换,能更真实地分析其频谱信息。

显示频谱时,由于示波器的分辨率有限,对512 点的频谱信息,采取每间隔8个点抽取1个点的方式,即得到64 点的频谱信息。由于显示时只需显示0~ fs 2(fs为采样速率)频率段的信息,故最后在示波器上清晰地显示32个点的频谱。

3 单元模块电路设计

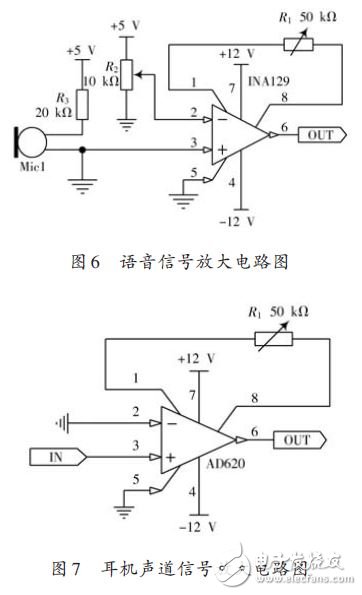

3.1 前级放大电路

一般来说,语音的输入能量不大,为了完成A/D 操作,就需要对输入的信号进行放大。对于简单的电路放大设计,选用最基本的AD620、INA129.对于调制电阻RG ,通过增益计算公式G = 49.4 kΩ/RG + 1 可以计算得到, RG 使用50 kΩ可调电位器来达到2.5 倍的增益放大,电路设计图如图6,图7所示。

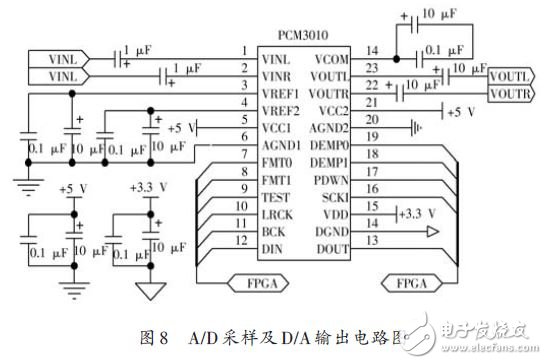

3.2 A/D及D/A设计电路

PCM3010 为24 b 立体声音频编码器,其内部包含Σ-Δ 型ADC和DAC.其中立体声ADC输入信号峰峰值为3 V,内置抗混叠滤波器和高通滤波器,采样速率为16~96 kHz可调,立体声DAC输出信号峰峰值为3 V,内置去加重滤波器,转换速率为16~192 kHz可调。DAC输出信号接后置低通滤波器,可实现较好的波形输出。

该芯片将ADC、DAC集成一体,极大地简化了硬件电路规模,并且价格便宜,具有极高的性价比。这里在某些数据线与控制线上串接了一个小电阻,以降低信号上下边沿的跳变速率。其电路图如图8所示。

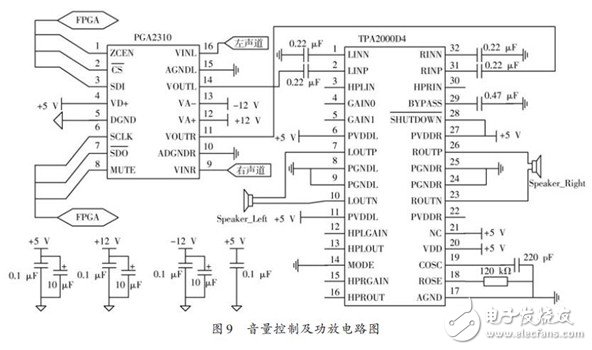

3.3 音量控制及功放电路

音量调节选用高性能立体声音频音量控制芯片PGA2310实现。通过数字方法控制模拟音量,每声道音量单独可调,并具有静噪功能。它具有极宽的增益衰减范围,-95.5~31.5 dB 以0.5 dB 步进可调,失真度仅为0.000 4%.其输出两路信号送入高效D 类音频功率放大器TPA2000D4,+5 V 供电驱动4 Ω负载时功率可达2 W.其静态功耗低,外接电路简单,无需外接LC输出滤波器,即可直接驱动扬声器。电路图如图9所示。

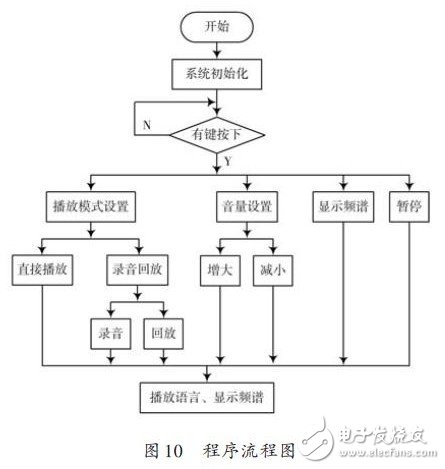

4 程序设计

系统软件部分由单片机的 C51语言和FPGA的Ver-ilogHDL语言组成。其中,单片机主要完成用户输入输出处理和系统的控制,FPGA主要完成需要严格时序控制(如数据采集、频谱显示)以及大规模数据计算(如FFT、ADPCM 编码)等。整个系统的设计中模块化思想贯穿始终,采用菜单键选择所用功能,系统流程图如图10 所示。

5 方案测试与结果

5.1 测试仪器

测试仪器包括直流稳压稳流电源,型号为SG1733SB3A;60M 数字存储示波器,型号为TektronixTDS1002;秒表。

5.2 方案测试与结果

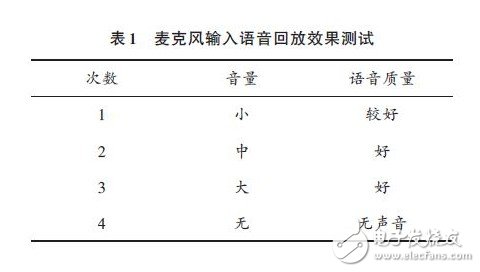

5.2.1 语音存储与回放效果测试

(1)一名组员面对麦克风以不同大小的声音说话,录下一段语音,记录回放语音的效果,结果见表1.

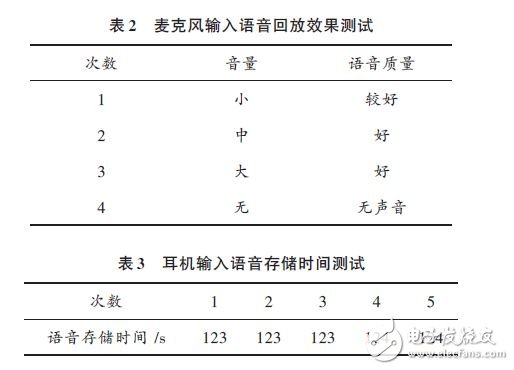

(2)由耳机输入不同音量的立体声音乐,录下一段语音,记录回放语音的效果,结果见表2.

5.2.2 语音存储时间测试

(1)由耳机不间断地输入立体声音乐,启用录音模式,待系统显示存储器存满后,回放语音,用秒表记录语音回放最长时间,结果见表3.

(2)一名组员面对麦克风不间断地说话,启用录音模式,待系统显示存储器存满后,回放语音,用秒表记录语音回放最长时间,结果见表4.

5.2.3 语音频谱分析及显示测试

由耳机或麦克风输入一段语音信号,由扬声器直接播放出来,同时在示波器上实时显示频谱。测试结果为当播放的声音变化时,可观察到频谱有相应的明显变化。

由于不能明确知道语音信号的实时频率和幅度信息,故只对频谱进行了定性测试。

6总结

该系统设计方案实现了语音存储及回放,最长存储时间达2 min,回放语音效果清晰良好,并能在示波器上实时显示语音频谱。采用ADPCM 编码在保证回放音质的情况下,极大地提高了存储器的利用率,并通过对语音信号采用分帧加窗的方法实现了短时频谱分析。

另外,系统采取了一系列抗干扰措施以减小噪声,如数字地与模拟地分开走线,在一点汇合;电源处采用一个10 μF和0.1 μF的电容并联去耦;时钟走线尽量短等。但系统在语音回放时仍存在一定的噪声,尤其当输入语音音量较小时,噪声更为明显,这是本方案需要完善的地方。

-

基于数字化语音存储回放及GSM语音传输系统设计2023-11-17 576

-

如何去设计ADPCM语音编解码电路?2021-05-06 1239

-

基于FPGA的语音录制与回放系统2019-10-22 2154

-

请问哪位大神有数字语音存储与回放系统仿真程序?求分享2018-06-12 1835

-

基于EPG3231的ADPCM实时解码和回放2017-11-02 1033

-

基于单片机的语音存储及回放系统课程设计设计(毕业设计)完整版2016-04-29 1469

-

求助数字化语音存储与回放系统设计2013-04-18 3970

-

语音压缩存储与回放工程2012-08-20 2587

-

单片机在语音存储与回放中的应用2012-08-17 2243

-

FPGA在语音存储与回放系统中的应用2010-01-14 1931

-

基于USB存储技术的电子语音记录系统的设计方案2009-12-09 887

-

数字化语音存储与回放系统2009-05-03 3143

全部0条评论

快来发表一下你的评论吧 !