透过设计实例揭秘FPGA电源的N个考虑事项

FPGA/ASIC技术

描述

引言

FPGA是一种提供许多逻辑单元和其他功能(如收发器、PLL和用于复杂处理任务的MAC单元)的器件。FPGA现在变得非常强大,有效地为它们供电是设计的一个重要方面,这一点常常被低估。

本文分析了针对FPGA的电源要求,提供了关于如何将其放在PCB上和放在什么位置的指导,并通过一个设计示例让读者熟悉设计步骤,设计当中FPGA所在的系统由12 V总线供电,这是来自市电供电SMPS的主输出。

功耗估算器和电压要求

FPGA设计的一个重要方面是确定所需电压要求和每个电压轨的电流要求。各大FPGA厂商都提供了综合性计算器来帮助确定这些要求,考虑因素包括器件工作频率、所用门电路数量以及门电路的切换率。例如,Altera提供了PowerPlay Early Power Estimator,Xilinx提供了XPower Analyzer。

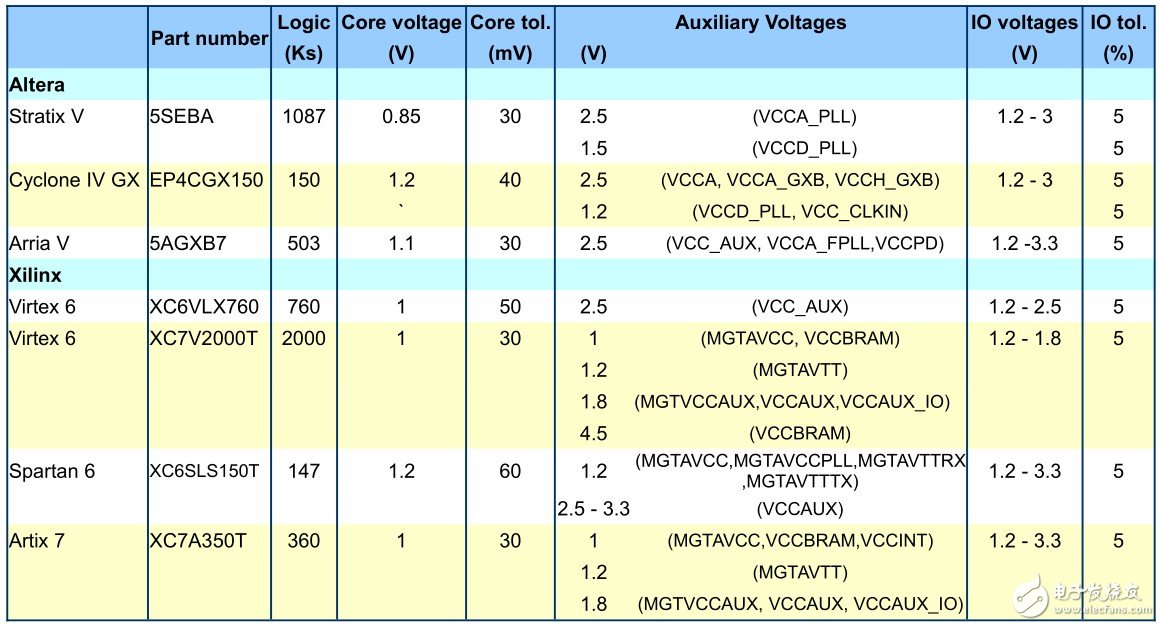

表1包含Altera和Xilinx器件需要的一些典型电压轨,分为三个核心电压:I/O电压、收发器电压和辅助电压。

POL和配电系统

核心电压较低的FPGA需要高电流、高精度和最小纹波。为实现这一目标,去耦电容器的位置应当尽量邻近FPGA,使去耦通路中的ESR和ESL最小。

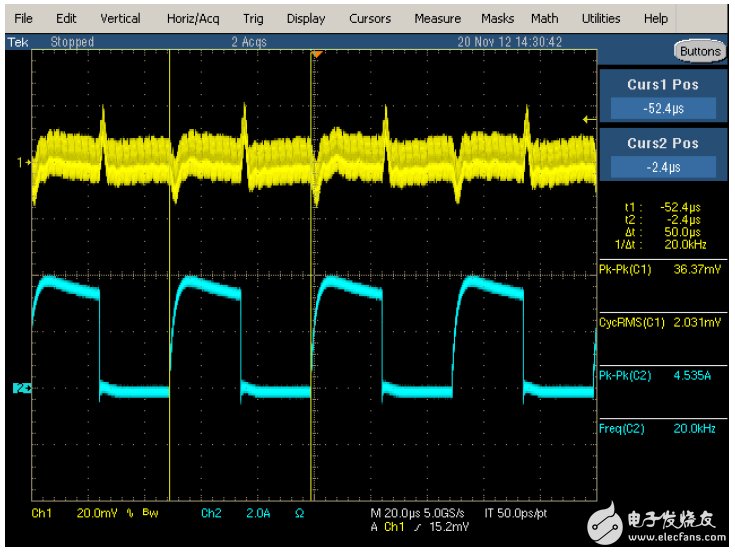

另一种合适做法是将POL稳压器放在尽量邻近器件的位置,但不影响FPGA的输入和输出路径。更高的工作频率和控制、驱动器与MOSFET和集成度有助于实现紧凑的布局。小解决方案占位面积允许将稳压器放在FPGA的近旁,从而改善稳压器瞬态响应。图1提供了来自Vishay microBUCK产品的一种3 A稳压器示例。

图1: 阶跃响应为SiP12107。VIN = 5 V,VOUT = 1.2,Fsw = 2 MHz;20 kHz时条件下负载阶跃 = 0 - 3 A;L = 330 nH,CIN = 22 μF,COUT = 22 μF;黄色 = VOUT,蓝色 = 电流。

从图中可以看出,在22 μF (0805) 最小输入和输出电容时,阶跃响应为37 mV Pk-Pk(负载还有一些电容)。

稳压器使用电流模式恒定导通时间 (CM-COT) 拓扑结构,且不需要通过外部纹波抑制来提供稳定性。这可以帮助降低元件数量和提供优异的瞬态响应。

选择合适的稳压器

在选择稳压器时,首要选择标准之一是所要求的输入工作电压。其次应当检查电流要求。在最终备选器件名单确定后,再对一些特性进行检查,如工作频率范围、低电流模式省电量等,这样设计人员就能确定最适合应用的器件。

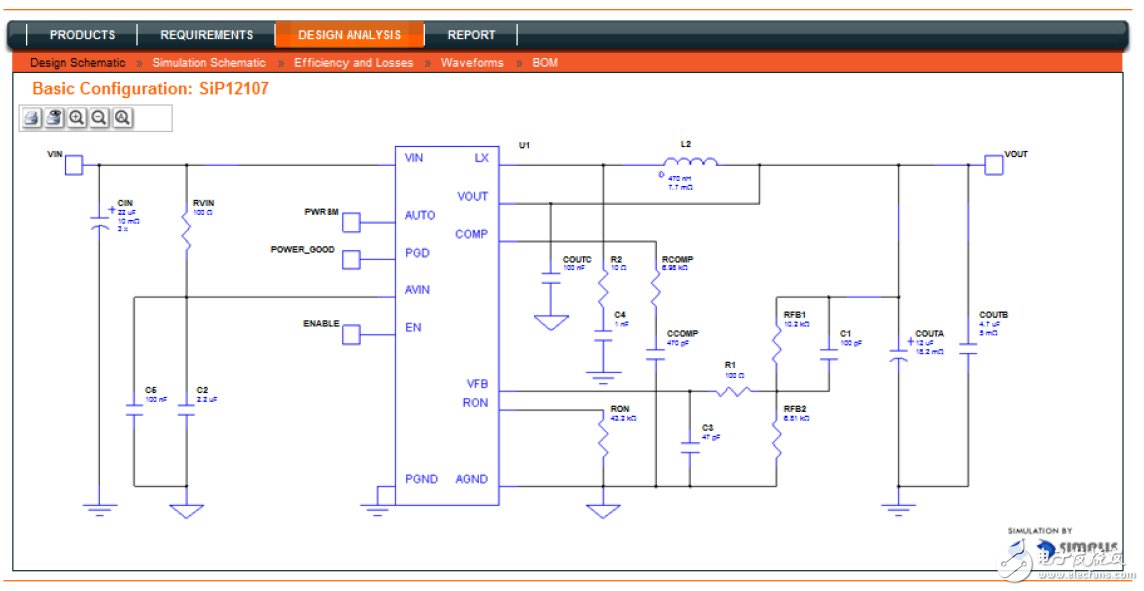

多家开关稳压器供应商现在都提供在线仿真工具来辅助电源设计。例如,Vishay稳压器有PowerCAD在线仿真工具支持。在使用上述方法分析了可选器件之后,在线仿真工具可让用户快速完成设计(参见图2的仿真电路原理图)。这个步骤完成后,接着可以检查工作波形,如启动、阶跃响应及稳态工作,以了解电流和电压幅值。该仿真器的特性还包括高效率、所有元件损耗的细分类目以及BOM生成器。

图2:Vishay PowerCAD软件仿真电路原理图

初始设计过程示例

我们以选择时钟速度为362 MHz的Cyclone IV EP4CGX75为例。

1.使用PowerPlay确定每个电源轨的电流要求。在此例中,我们只对输出端具有最差情况负载时的FPGA供电进行分析。表2列出了从早期估算器软件得到的设计技术规格。

表2:来自Altera PowerPlay的设计技术规格

2.现在可以选择器件。从表2可以看出,器件的核心电压在电流为5 A时是1.2 V。另外还有来自这个电压轨的另一个1 A要求,使得来自该电压轨的总电流要求为6 A。实际上,其他两个电压也是这样,并且导致图3所示的电源架构。

图3:示例解决方案

3.运行Vishay PowerCAD仿真器,得到表3中的结果。

这些仿真与最终设计在效率方面的差异不超过1%。虽然它们不能取代详尽的设计过程,但有助于设计人员在费时费力完成硬件设计任务前快速了解可能得到的结果。

作者:Owain Bryant,Vishay Siliconix产品应用工程师

——本文选自电子发烧友网09月技术特刊《智能工业特刊》,转载请注明出处,违者必究!

-

恩智浦 MCX N系列之电源管理(MCX N94/54与MCX N23)2024-12-05 2490

-

FPGA的高速接口应用注意事项2024-05-27 3161

-

FPGA的27个实例2014-05-10 5407

-

FPGA电源排序考虑因素2018-09-10 1891

-

请问目前FPGA设计流程还需要考虑哪些事项?2019-10-11 1420

-

FPGA很有价值的27个实例分享2023-09-21 514

-

具有多个电压轨的FPGA和DSP电源设计实例2009-09-25 917

-

透过USB设定FPGA2013-01-10 521

-

FPGA语音通信平台设计实例2016-06-07 588

-

27个FPGA实例源代码2016-08-19 2019

-

SDN部署前必须考虑的7个事项2017-01-12 721

-

设计fpga稳定电源定序的注意事项2017-11-15 4086

-

使用FPGA设计的2个实例详细说明2020-09-23 1347

-

27个FPGA实例源代码合集2021-01-14 3891

-

先进FPGA的电源设计注意事项(电源设计器121)2024-08-26 412

全部0条评论

快来发表一下你的评论吧 !