为什么英特尔那么牛?制程工艺引业界惊叹!

工艺/制造

描述

半导体制程工艺上,英特尔要是说第二,那没人敢说第一。晶圆制造这个圈子,英特尔毫无疑问处于第一流,其他厂商包括IBM,英飞凌,NEC,意法半导体以及东芝等公司,以及目前半导体代工行业的老大老二老三——台积电、 GlobalFoundries、三星,统统都是二流。

说这么绝对可能有人不服,小编举最近的一个例子,英特尔仅仅破一次例为美国芯片制造商Altera代工首个四核64位ARM Cortex-A53处理器,就引发了业界一片惊叹。

为了让大家一窥 Intel在半导体制造工艺上的牛逼,笔者选取数月前参加Intel新品交流会后,印象深刻的45nm以下HKMG的成型工艺来做探讨。

随着晶体管尺寸的不断缩小,HKMG(high-k绝缘层+金属栅极)技术几乎已经成为45nm以下级别制程的必备技术。不过在制作HKMG结构晶体管的 工艺方面,业内却存在两大各自固执己见的不同阵营,以IBM为代表的前栅极Gate-first工艺流派和以Intel为代表的后栅极Gate-last 工艺流派。更准确点说,在步入HKMG时代之初,只有Intel 和其他所有半导体企业之别。

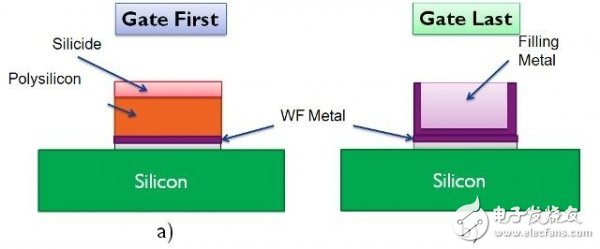

前栅极和后栅极工艺实现HKMG结构,在技术上有什么差别,请看这段引用:

Gate- last是用于制作金属栅极结构的一种工艺技术,这种技术的特点是在对硅片进行漏/源区离子注入操作以及随后的高温退火工步完成之后再形成金属栅极;与此相对的是Gate-first工艺,这种工艺的特点是在对硅片进行漏/源区离子注入操作以及随后的退火工步完成之前便生成金属栅极。Gate-last工艺的难点则在于工艺较复杂,芯片的管芯密度同等条件下要比Gate-first工艺低,需要设计方积极配合修改电路设计才可以达到与Gate-first 工艺相同的管芯密度级别。采用Gate-first工艺制作HKMG的劣势,是用来制作high-k绝缘层和制作金属栅极的材料必须经受漏源极退火工步的高温,会导致PMOS管Vt门限电压的上升,这样会影响了管子的性能。

如果对这段不太理解的童鞋,只需要记住一点:后栅极成型HKMG技术制造的芯片,功耗更低、漏电更少,高频(即高性能)运行状态也更稳定;但是生产制造技术复杂、良品率低、初期很难大规模量产;(在没有采用3D晶体管结构前)管芯密度低,对晶圆的利用不够经济;真正实用时,还需要用户层面的配合,即客户厂商根据需求配合修改电路设计。

45nm以下必要的HKMG技术中Gate-first/Gate-last成型工艺各有优劣,Intel追求未来的性能增长选择Gate-last,其他厂商则选择整体难度较小、眼下更容易实用的Gate-first,经过几年发展后,情况如何呢?

先看Gate-first,下面这段话引用自英特尔中国技术发言人洪力的评价:

28 纳米去年TSMC(台积电)刚刚用到所谓后栅极工艺,英特尔从45纳米开始用后栅工艺,那是4年以前的事。这个时候功耗就来的小,那个时候我们出来包括 IBM那些所有的人出来说英特尔宣布做后栅工艺的时候,不可能达到经济利益上的量产,因为太难做了,英特尔做出来了。为什么后栅很重要,当处理器运算的频率高的时候,你的功耗就会很大,这部分做起来很不容易。所以你会看到去年很长时间都讲到产能不足的问题,现在TSMC有了,三星的 28纳米还是前栅工艺的。到22纳米的时候我们其实已经开始做三维晶体管,这是晶体管的一个创新,栅极起来了。那样的分布方式使得它的性能和功耗、密度都会有一个更大的提高,你去看一看TSMC的3D的晶体管是2015年开始量产,可以看到中间差多远,三年半的时间。此28纳米和彼22纳米不是一回事。还有一些厂商说还有14纳米更小的,这跟做逻辑的不是一回事,所以英特尔领先是按代来衡量的,是一代还是两代。

再看看Gate-last,这是台积电研发部门高级副总裁蒋尚义从Gate-first阵营转向Gate-last阵营时说的话:

和 20年前一样,我们现在又遇到了如何控制Vt(管子门限电压)的难题。如今的Gate-first+HKMG工艺同样存在很难控制管子Vt电压的问题。尽管厂商可以在管子的上覆层(capping layer)上想办法对这种缺陷进行补偿,不过这种方案“极其复杂和困难程度相当高”Gate-last工艺当然也存在一些局限性。比如这种工艺制出的管子结构很难实现平整化。不过如果设计方的Layout团队能够在电路设计方面做出一些改动,那么就可以克服这个问题,使Gate-last工艺制作出来的芯片的管芯密度与Gate-first工艺相近。在我们采用后栅极工艺的时候,有的客户一开始抱怨连连,曾一度表示如果采用这种新工艺,那么产品的管芯密度很难与Gate-first保持一致,不过经过我们多次面对面的商谈讨论,客户们已经完全接受了这种新的工艺。我相信目前仍坚守Gate-first阵营的厂商在22nm制程节点将被迫转向采用Gate-last工艺。我不是在批评他们,只是认为他们最终会改变观念的。除非他们能找到一种成本低,极具创意的方案来控制管子的门限电压,否则他们必然要转向Gate-last工艺。

这里不得不提的是,据蒋尚义介绍,20年前,半导体产业也同样面临类似的难题,当时的半导体厂商计划在NMOS/PMOS管中统一采用N+掺杂的多晶硅材料来制作栅极,厂商们发现当在PMOS管中采用这种栅极材料之后,管子的性能表现并不好,管子的Vt电压很难降低到理想的水平。为此,有部分厂商试图往PMOS管的沟道中掺杂补偿性的杂质材料,以达到控制Vt的目的。不过此举又带来了很多副作用,比如加剧了短沟道效应对管子性能的影响能力。

为何45nm刚开始的时候,只有一家Intel知道使用后栅极,因为:伟大的企业,特质都是相同的——目光长远,极富预见性。Intel 如今的领先优势有多大,洪力的描述非常清楚地表达出了目前半导体代工业老大TSMC和Intel 的差距,这里就不再重复了。

台积电“以史为鉴”,转向后栅极工艺。而目前正在冉冉升起的三星(目前半导体代工市场份额已经仅次于台积电和GlobalFoundries),更是精明,早在步入HKMG时代之初,三星虽然加入了前栅极工艺的阵营,但是据传一直在偷偷研发和尝试后栅极工艺。(待续,下篇将说明目前后栅极成型HKMG工艺芯片的分布情况,并做相关的分析和对比)

很多人知道28nm制程比40纳米先进,耗电更低、发热更少、集成的晶体管更多。更进一步,不少人还知道HKMG(high-k绝缘层+金属栅极)是实现更先进制程的必备技术。但了解HKMG的两种工艺——前栅极/后栅极的人就很少了吧。HKMG的这两种工艺对芯片性能/功耗的影响,同样十分巨大。

很多人知道28nm制程比40纳米先进,耗电更低、发热更少、集成的晶体管更多。更进一步,不少人还知道HKMG(high-k绝缘层+金属栅极)是实现更先进制程的必备技术。但了解HKMG的两种工艺——前栅极/后栅极的人就很少了吧。HKMG的这两种工艺对芯片性能/功耗的影响,同样十分巨大。

为了让大家对芯片制造工艺好坏有一个全面认识,先普及下几个重要的概念。

线宽

28nm和40nm指的是芯片上晶体管和晶体管之间导线连线的宽度。半导体业界习惯用线宽这个工艺尺寸来代表硅芯片生产工艺的水平。线宽越小,晶体管也越小,让晶体管工作需要的电压和电流就越低,晶体管开关的速度也就越快,这样新工艺的晶体管就可以工作在更高的频率下,随之而来的就是芯片性能的提升。简而言之就是,线宽越小,芯片更省电的同时,性能还会提高。

晶体管栅极

我们通过所说的芯片上的晶体管,是指金属氧化物半导体场效应管(简称:金氧半场效晶体管,MOSFET),有栅极(gate)、漏极(drain)、源极(source)三个端。

其中缩小栅极面积让晶体管尺寸变小,是工艺进化的关键。HKMG指的就是金属栅极/高介电常数绝缘层(High-k)栅结构,相对于传统的poly/SiON多晶硅氮氧化硅,下面的图表可以直观地展示它们的不同。

阻碍传统的poly/SiON栅极面积做小的原因,是下方的氧化物绝缘层(主要材料是二氧化硅,不过有些新的高级制程已经可以使用如氮氧化硅silicon oxynitride, SiON做为氧化层之用)的厚度是不能无限缩小的。栅极氧化层随着晶体管尺寸变小而越来越薄,目前主流的半导体制程中,甚至已经做出厚度仅有1.2纳米的栅极氧化层,大约等于5个原子叠在一起的厚度而已。在这种尺度下,所有的物理现象都在量子力学所规范的世界内,例如电子的穿隧效应。因为穿隧效应,有些电子有机会越过氧化层所形成的位能障壁(potential barrier)而产生漏电流,这也是今日集成电路芯片功耗的来源之一。为了解决这个问题,有一些介电常数比二氧化硅更高的物质被用在栅极氧化层中。

high- k工艺就是使用高介电常数的物质替代SiO2作为栅介电层。intel采用的HfO2介电常数为25,相比SiO2的4高了6倍左右,所以同样电压同样电场强度,介电层厚度可以大6倍,这样就大大减小了栅泄漏。后来,intel在 45nm 启用了 high-k ,其他企业则已在或将在 32nm/28nm 阶段启用 high-k 技术。high-k技术不仅能够大幅减小栅极的漏电量,还能有效降低栅极电容。这样晶体管的关键尺寸便能得到进一步的缩小,而管子的驱动能力也能得到有效的改善。

简而言之,与poly/SiOn相比,使用HKMG栅极,晶体管能做的更小,漏电也更少。目前同制程下,HKMG比poly/SiON耗能低30-35%,所以理论上,32nm的HKMG耗能差不多等同于22.5-24nm的poly/SiON。

前栅极/后栅极

前面我们论证了HKMG相对于poly/SiON的优势,但很少人知道,即使同样是HKMG栅极,如果采用不同的制造工艺——前栅极(gate-first)/后栅极(gate-last),芯片表现是不一样的。

煮机上一篇文章已经说过,前栅极工艺制作HKMG,用来制作high-k绝缘层和制作金属栅极的材料必须经受漏源极退火工步的高温,会导致晶体管Vt门限电压上升,这样会影响管子的性能。具体表现,就是当处理器运算的频率高的时候,功耗就会很大。

所以,在高性能/低功耗方面,使用后栅极工艺HKMG栅极的芯片较好。

好了,我们花了很长的篇幅给大家讲解了HKMG栅极相对于poly/SiON栅极的优势,以及后栅极工艺HKMG为什么比前栅极工艺HKMG更好,下面将是重头戏了。

英特尔为什么牛——移动芯片制程工艺一览

前两篇说了一大堆,无非论证了,除了大家熟悉的xx纳米(线宽)越小制程越先进,评价目前半导体制程水平还有两点:Poly/SiON栅极和 HKMG栅极的档次差距,以及如果同样是HKMG栅极的情况下,采用前栅极工艺(gate-first)和后栅极工艺(gate-last)对芯片在实际应用时的影响。

前两篇说了一大堆,无非论证了,除了大家熟悉的xx纳米(线宽)越小制程越先进,评价目前半导体制程水平还有两点:Poly/SiON栅极和HKMG栅极的档次差距,以及如果同样是HKMG栅极的情况下,采用前栅极工艺(gate-first)和后栅极工艺(gate-last)对芯片在实际应用时的影响。

这里再总结一下:

(1)与poly/SiON相比,使用HKMG栅极,晶体管能做的更小,漏电也更少

(2)在高性能/低功耗方面,使用后栅极工艺HKMG栅极的芯片较好

可能大家会提到FinEFT即3D晶体管,这个是整个晶体管层面上的创新(三栅极晶体管),而之前我们讨论的、无论是关于HKMG栅极和poly/SiON 栅极,还是gate-first/gate-last工艺,创新仅仅局限在传统晶体管的栅极上。考虑到目前只有Intel 一家实现了3D晶体管的大规模量产和实用,其他厂商完全与其不在一个档次上,而此文的主要目的是比较台积电、Globalfoundries、三星目前半导体制程工艺的优劣,所以就不再深究FinEFT的影响了。

台积电28nm制程工艺分布情况

台积电目前四种适应不同市场定位设备的28nm工艺,其中HP、HPL、HPM皆采用了HKMG栅极和后栅极工艺,而LP采用了poly/SiON栅极和前栅极工艺。所以,综合来看,HPM最好,LP最差。

参照上图,性能方面HPM>HP>HPL>LP,漏电HPL<HPM<LP<HP。

实用层面,高通MSM8960 Snapdragon S4使用的就是28nm LP工艺,而红米吹嘘的联发科四核芯片MT6589T也是台积电最差的28nm LP工艺。

HPM的实用典范则是高通的骁龙800。最近MTK(联发科)发展势头惊人,已经曝光的下一代四核芯片MT6588和八核芯片MT6592将采用台积电28nm级别综合最好的HPM工艺。

英伟达A15核心的Tegra 4使用的是漏电最少的HPL,看来为了控制A15的功耗,英伟达也只有在制程工艺上弥补了。

GlobalFoundries的28/32nm 制程工艺情况

Globalfoundries四种28nm制程工艺和单独列出的32nm制程,皆是gate-first即前栅极工艺,可见其目前的制造水准。

这里不得不八卦一下,Globalfoundries最初成立是依靠从AMD分离出来的晶圆制造厂,后来获得中东超富产油小国的Advanced Technology Investment Company(ATIC)公司投资入股,到最后ATIC全资入股,所以Globalfoundries烧钱起来是毫不吝啬的。中东富豪投资这一行,花钱起来让人侧目,但似乎并不怎么上进。

如上表,32nm级别的SHP和28nm级别的HPP、HP、SLP都是HKMG栅极,而G(unoffical)则是传统的Poly/SiON。客户一栏里我们也可以发现,Globalfoundries主要客户还是AMD。

另外,据说Globalfoundires依靠价格优势以及台积电产能不足,今年第三季度从台积电那里分流了点MTK(联发科)和高通的28nm级芯片的订单,具体用在哪些产品上,笔者并不清楚,但可以肯定的是,这些芯片的品质非常一般。

三星也传出把Globalfoundries当做是“后备工厂”,因为目前三星的晶圆工厂已无法同时满足自家芯片和苹果A系列移动芯片的需求,就把一部分订单转包给了Globalfoundries。苹果整天吵着要“脱离”三星,事实上,三星根本无所谓,你脱离了反倒释放了产能,可以给自己的产品集中供货。

三星 28/32nm制程工艺情况

三星目前的28nm级别制程使用的是HKMG栅极,但是是前栅极工艺。自家的Exyons 5系列芯片和苹果的A7,都是采用的此种工艺。

但是千万别以此小看了三星。早在业界进入HKMG时代之初,三星声明支持前栅极工艺却秘密研发后栅极工艺,下一代无20nm/14nm全面使用后栅极工艺应该是板上钉钉了。

还有更惊人的,三星的14nm级FinEFT即3D晶体管早在2012年年底就已经流片成功,相传明年旗舰Galaxy s5上的Exyons 6系列芯片就使用这种工艺制造,而量产时间点,就在明年2014年年初!相比之下,目前晶圆代工市场份额最大的台积电,其产品路线图显示2015年才会量产3D晶体管芯片。而Globalfoundries,在三星已经流片14nm FinEFT晶圆成功的前几个月,才刚刚宣布14nm 3D晶体管的研发计划。

如果传言属实,三星进步神速不但会在技术上最接近Intel,最先进制程的大规模量产实用层面,则一举超过包括 Intel、台积电和Globalfoundries。未来一年将是晶圆代工市场格局发生关键性转折的一年,三星无论在技术上、还是率先大规模实用最先进制程工艺上,很可能一鸣惊人,就此逆转老3的地位。

至于苹果要脱离三星,圈内稍微有点常识的都知道,这对苹果来说是得不偿失,只能在媒体上吹风而已。把订单交给台积电,台积电不愿承担风险,为台积电增加投资和补贴意味着抬高成本;而把订单交给GlobalFoundries,GF如此懒散不求上进的“土豪”,无论是大规模量产供货上,还是产品技术品质,都竞争不过勤奋的亚洲人。Intel ?苹果得看别人的心情。

总结

Intel在后PC时代还是保持着Tick-Tock的节奏,这几年在制程级别的代级领先和更先进的工艺技术,还是前几年积累的。竞争对手与其差距正在慢慢缩小。其中,三星尤其值得警惕。

晶圆制造领域Intel 之外的其他厂商,台积电的表现算是稳扎稳打,但基于赢利/商业利益的考量,技术演进的速度还是过于保守了。靠钱堆起来的Globalfoundries 开始有了起色,正在慢慢走向成熟,但土豪的气质依然未变,靠脚底下石油不愁吃不愁穿的阿拉伯人,最欠缺的其实是亚洲人的上进心/危机感。

三星的话,不多说了,看不久的将来会发生什么吧。

-

457868671

2016-02-12

0 回复 举报三星还是前栅,台积电后栅拿到苹果A10的全部的制作订单。三星还是要加油啊 收起回复

457868671

2016-02-12

0 回复 举报三星还是前栅,台积电后栅拿到苹果A10的全部的制作订单。三星还是要加油啊 收起回复

-

刘拓

2013-11-23

1 回复 举报牛叉,,确实牛叉。。。 收起回复

刘拓

2013-11-23

1 回复 举报牛叉,,确实牛叉。。。 收起回复

-

制程技术的飞跃 英特尔22纳米制程剖析2013-01-29 3998

-

展示10纳米制程,英特尔推动FPGA技术进展2017-09-20 6820

-

#高通 #英特尔 #Elite 高通X Elite芯片或终结苹果、英特尔的芯片王朝深圳市浮思特科技有限公司 2023-10-27

-

英特尔转型移动领域难言乐观2012-11-07 3268

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 3065

-

英特尔半导体制程的节点命名2019-07-17 3482

-

为什么选择加入英特尔?2019-07-25 5210

-

英特尔重新思考解决芯片短缺的常用基板2022-06-20 6761

-

英特尔推出32纳米制程工艺的酷睿i72010-03-26 2119

-

英特尔开始研发7纳米和5纳米制程工艺2012-05-17 1400

-

英特尔14nm工艺制程永流传2019-12-02 9024

-

浅析英特尔加速制程工艺和封装技术创新2021-08-09 2221

-

英特尔的Intel 4工艺详述2022-06-22 7433

-

英特尔和ARM合作 基于英特尔18A工艺进行设计技术协同优化2023-04-19 1707

-

英特尔全新16nm制程工艺有何优势2023-07-15 2134

全部0条评论

快来发表一下你的评论吧 !