初学者必看:破解PCB设计常见错误!

描述

在新手开始PCB设计时,通常将该过程视为简单的“连接点”:只要建立了连接,如何建立这些连接并不是特别重要。

不幸的是,这与事实相去甚远。作为 PCB 设计工程师,尤其是随着电子设备速度的不断提高和排放标准的严格,我们需要关注 PCB 和互连的最复杂的细节。如果我们粗心大意,我们就有可能面临信号完整性差和电磁兼容性差的风险。

在过去的几年里,我们遇到了相当多的其他PCB设计工程师的PCB,其中有很多常见的,错误的情况。

本文旨在说明初学者的五大PCB设计错误,以及我们可以做些什么来避免犯这些错误。让我们开始吧!

走线间距:

制造商将拥有他们可以制造的最小间隙。所需的间隙越小,电路板的成本通常就越高。

初学者的一个常见错误是认为简单地遵守允许的最小或可制造的间隙是要走的路。如上所示,所有信号类型的走线都打包在一起,仅受设计规则的限制,设置为制造商允许的最小走线间距。

不幸的是,这种操作会使制造变得更加困难,而且容易提高PCB不良率,这种布线方式会显著增加走线到走线的耦合,从而导致串扰和噪声增加。

除非根本无法避免,否则应尽量避免长距离紧密间隔、平行运行的走线。

因此,我们的第一个简单技巧是在迹线之间留出足够的间距。根据经验,这至少是信号层到相邻参考层之间间距的三倍。例如,对于 0.11mm 的介电厚度,我们希望走线间距最小为 0.33mm,但最好更大。

走线宽度:

另一个常见的初学者PCB设计错误是将相同的走线宽度用于任何类型的走线。无论是载电走线、高阻抗节点还是高速信号等。

在整个设计中使用相同的走线宽度可能很方便,但这肯定不是最佳选择。

迹线及其宽度应根据各种因素确定大小。例如,承载较大电流的走线应更宽,高阻抗和灵敏的信号走线需要更细,射频信号的走线通常需要控制阻抗。

很多人会惊讶地发现,例如,0.2mm宽的走线可以处理高达约一安培的电流,而温度仅为20摄氏度!

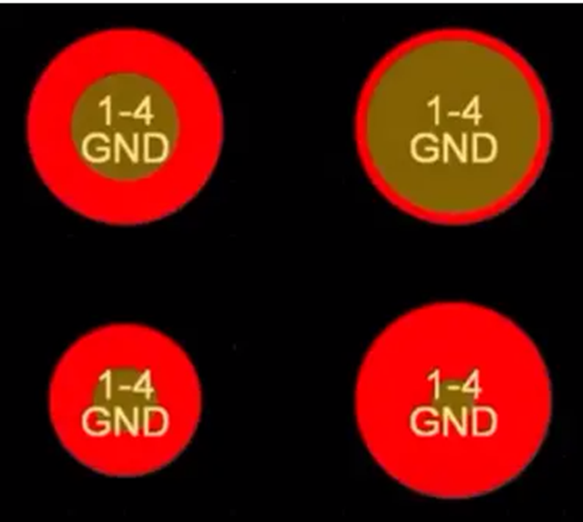

Via Sizin:

与走线一样,通孔也需要适当调整尺寸。对于通孔,我们有两个主要参数需要确定。整体通孔直径和钻头直径。从通孔直径中减去钻头,然后将结果减半,得到环形环。

制造商将对钻头直径和环形环具有最小能力。初学者 PCB 设计人员通常会使钻头直径过大或过小,或者环形环太小而无法可靠制造(即使有!)

我对“标准”通孔的建议是直径为0.7 毫米,钻头为 0.3 毫米。这样的通孔可以很容易地承载大约一到两安培的电流。

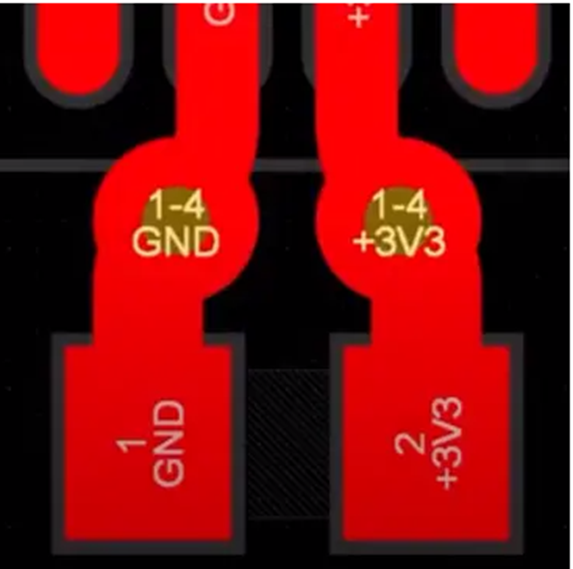

解耦:

对于PCB设计新手工程师来说,正确的去耦是一个经常被忽视的方面。然而,不幸的是,解耦对于一个运行良好和正常运行的系统至关重要。

通过低阻抗连接实现良好的去耦,确保在短时间内向需要大量能量的IC提供适当的功率。随着IC上升和下降时间的减少,以及电流需求的增加,这成为一个更加关键的问题。

我们可以通过将去耦电容器放置在靠近相关IC引脚的位置,使用短而宽的走线,以及将电源通孔彼此靠近,从而实现良好的去耦。

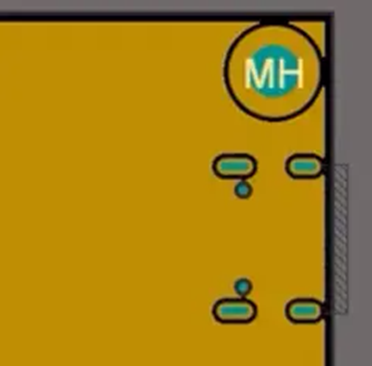

Reference Planes:

最后一个技巧是在设计中使用实心基准(最常见的是“GND”或“0V”平面)。

许多设计工程师只关心信号的正向路径。然而,信号和电力在闭环中传播,需要返回源头。

事实证明,当在PCB上铺设AC(频率大于几kHz)走线时,返回电流瞬时位于下面的平面中。这是由于电磁场包含信号的实际能量并在迹线和平面之间产生。

因此,我们需要确保对于交流信号,我们正下方有一个参考平面。这可以是 0V,或者在某些情况下,可以是合适的参考电源平面。我们还需要确保在这个参考平面上不会产生任何大的空隙或分裂,如果我们这样做了,我们不会在信号层上用迹线穿过这些分裂。这样做会产生严重的 EMI 问题。

声明:文章和图片来源于网络,版权归原作者所有。如有侵权,请联系删除。

-

protel技术大全--初学者必看2012-08-04 5960

-

PCB LAYOUT技术大全---初学者必看!2013-01-09 26135

-

MATLAB入门教程-初学者必看2013-06-28 4524

-

Linux初学者必看!!!2014-01-07 3268

-

PCB LAYOUT技术-初学者必备2011-07-12 4822

-

PCB LAYOUT初学者必看!2013-09-13 2085

-

初学者常见的Python运行错误及其示例归纳2017-11-15 2841

-

初学者PCB设计师的几大问题2020-09-23 1771

-

PCB设计初学者和爱好者的常见错误应引起注意2020-11-16 2994

-

初学者必看的基本电子技术概念2021-05-17 1588

-

Labview初学者常见问题及解答2021-05-25 1317

-

初学者必看的电源测试项目要点及教程2021-07-01 1466

-

初学者必看的LABVIEW工程师编程经验2021-07-12 1514

-

ARM与嵌入式linux入门的建议(初学者必看)2021-08-04 1077

-

初学者必看的单片机程序汇总2021-09-15 1933

全部0条评论

快来发表一下你的评论吧 !