全芯片ESD防护网络

电子说

描述

导语:

据统计,静电放电(Electro-Static Discharge, ESD)造成的芯片失效占到集成电路产品失效总数的38%。完好的全芯片ESD防护设计,一方面取决于满足ESD设计窗口要求的优质ESD器件结构,另一方面全芯片ESD防护网络的考量也格外重要。

正文:

静电放电造成的CMOS IC损坏已是众所周知的芯片可靠性问题之一。随着工艺水平的不断进步,先进的工艺制程严重降低了深亚微米CMOS IC的静电防护能力,给ESD器件结构的设计带来了更大的挑战。因此,设计满足ESD窗口的优质ESD器件成为重要的研发方向之一。然而,全芯片ESD防护网络的设计也格外重要。

一般而言,为加强ESD防护能力,大多数IC会在输入PAD、输出PAD和电源PAD周边做上ESD防护电路。但有时即使在输入、输出和电源轨上已有适当的ESD防护器件或电路,IC内部电路仍然会因ESD测试而发现异常损伤问题,而保护内核电路的ESD器件却没有损坏。因此,全芯片ESD防护设计必须要注意全芯片防护网络架构的设计,才能够真正避免内部电路发生异常损伤。下面列举IO测试和Pin to Pin两种测试下的内部电路异常损坏情形和具体解决办法。

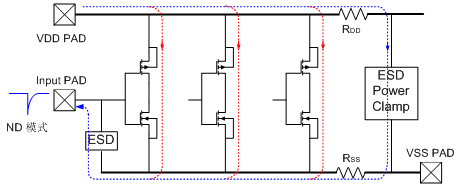

1、IO脚的测试

如图1所示,在ND模式下,输入PAD有一负脉冲,VDD PAD接地。因VSS浮接,原本落在输入PAD与VDD线之间的ESD负电压,转变成落在VDD与VSS电源线之间,该ESD电压应该经ESD Power clamp和Input PAD的ESD旁路泄放。但是,若IC内的VDD与VSS电源线散布极长,该ND模式的ESD电压会经由VDD与VSS电源线而进入IC的内部电路中(红色路径),导致IC内部电路的ESD损伤。

图1 IO脚的测试

图1所示情形说明了电源线过长时,杂散电阻/电容会降低ESD箝位电路的防护效果。因此,解决办法是除了在VDD和VSS PAD放置ESD power clamp以外,在电源线间适当的地方加入VDD与VSS的ESD power clamp电路,能够协助大幅提升输入/输出脚的ESD耐压能力。

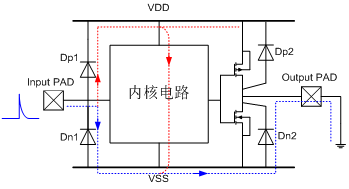

2、Pin to Pin的测试

如图2所示,一个正ESD电压加到IC的某一输入脚,IC的另一输出脚相对接地。此时该ESD脉冲应该利用输入脚上的ESD防护二极管Dn1雪崩击穿来旁通ESD电流到浮接的VSS电源线上,再经由输出脚NMOS的寄生二极管Dn2流出IC到地。但是,在Dn1雪崩击穿前,该ESD电流会先经由输入脚的二极管Dp1对浮接的VDD电源线充电,而浮接的VSS也会因输出脚接地而被Dn2偏置在接近地的电压准位。这样,该ESD脉冲会转变成落在VDD与VSS电源线间的ESD过压。因此,ESD电流会随着VDD与VSS电源线而进入IC的内部电路(红色路径),造成IC内部损伤。

图2 Pin to Pin的测试

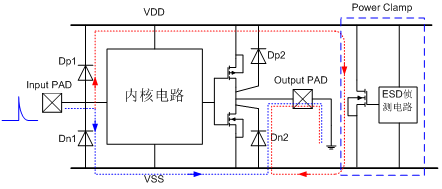

如图2所示的情形说明了,出现在IC的输入脚或输出脚上的ESD电压可以转变落在VDD和VSS之间,因此,要能够有效地保护到整颗IC不受ESD损坏,必须在IC的VDD与VSS电源线间做一有效的ESD防护电路。一般而言,VDD与VSS电源线之间会放置大尺寸的GGNMOS元件,但是,即使有该NMOS元件当做ESD防护元件来旁通ESD放电电流,IC的内部电路依然会出现ESD损伤的问题。其原因是IC的内部电路通常使用最小间距,因而内部电路元件因具有最小尺寸会先于电源线间的GGNMOS击穿导通,因此,GGNMOS元件不能够有效地来保护IC的内部电路。解决办法是使用ESD侦测电路,使VDD到VSS间的NMOS具有更低的导通电压,如图3所示。

图3 ESD网络改进后的Pin to Pin测试

-

ESD防护设计的核心准则2026-04-20 610

-

汽车网络ESD防护利器:ESD772详解2026-02-25 417

-

如何提高ESD静电防护 PCB ESD防护设计的重要措施2023-09-14 4967

-

数字孪生智慧加油站,构建安全防护网2022-11-03 1772

-

如何进行ESD防护?2022-04-27 6669

-

USB3.0接口的ESD防护设计2020-10-27 1258

-

探索ESD防护器件的原理及选用2020-09-22 3152

-

【转】电路级静电防护设计技巧与ESD防护方法2019-04-23 2926

-

铁丝防护网@享受自己辛福有价值生活2018-12-15 199

-

电路级静电防护设计技巧与ESD防护方法2018-10-23 2706

-

浅析ESD 防护与ESD 防护器件2017-07-31 5326

-

网络播放器端口防护2017-06-20 4277

-

IPv6防火墙设计系统 构建全方位的安全防护网络2013-01-08 2144

-

ESD防护的PCB设计准则2009-04-07 2859

全部0条评论

快来发表一下你的评论吧 !