MIT突破传统架构,挑战36核心处理器

处理器/DSP

描述

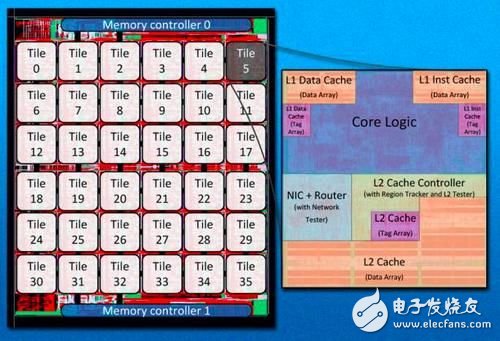

美国麻省理工学院(MIT)的研究人员们最近利用“片上网络” (NoC)技术,期望打造出一款具有快取一致性且能够扩展至任何核心数的多核心架构。截至目前为止,研究人员们已经开发出一款36核心的处理器晶片原型了。

MIT 开发的36核心原型采用类似“铺砖”(tile)的实体布局,每一个tile中包含一颗核心以及一个路由器,用于将固定大小的讯息封包传送到相邻核心,最后传送到目标核心。为了维持快取一致性,MIT研究人员透过主网络采用Snoopy协议的二级“影子”网格方式,从而实现更具扩展性的架构,此外,速度也比传统分布式目录快取一致性更快24%,比AMD的HyperTransport汇流排更快12%。

MIT连结32颗核心(tile)以及2个NoC,透过协议保持核心之间的快取一致性。

MIT 电子工程与计算机科学系教授Li-Shiuan Peh表示:“影子网络是一种无需缓冲、免竞争的2D网格网络,能够保持Snoopy协议的一致性。它可确保所有的节点都知道将会到达主网络的数据请求来源。所有的节点都将始终如一地执行优先排序──这对于Snoopy 协议的一致性至关重要。”

由于略过L2快取,发出的请求被传送至主要网络上。接着在影子网络上发出一项通知给所有的核心告知来源核心的请求即将到达。由于采用单一位元传送,来自其他核心所发出的通知可合并传送,从而加速在影子网络上的传送速度。

目前针对多核心晶片的开发可采用多种不同的互连拓扑。一般来说,在8颗核心以下的晶片可直接使用汇流排轮流连接各核心。另一方面,MIT的36颗心处理器架构采用晶片上网格网络的方式,让人联想到英特尔(Intel)在2007年发表的Teraflop Research Chip(代号Polaris),它采用的就是相邻晶片之间的直接互连方式,传送至远端核心的资料同样经由核心之间逐次传送的方式,直到到达目的为止。然而,英特尔的50核心Xeon Phi则改以多个高速路径的方式分别传送资料与位址,取代了网格网络的传送方式。

另一方面,MIT建议使用双网格网络──一个用于传送资料,另一个则用于Snoop协议,以确保由一颗核心发出的数据请求是最新的。每颗核心都有其快取来保持经常使用中的资料,只需偶而传送回主记忆体以取得更新。Snoop协议采用二级影子网格以确保请求的资料来自于最近更新来源,以及指定优先层级,让每颗核心都能以正确的顺序接收到所需的资料,从而执行平行运算。

在原型晶片通过功能验证后,包括Li-Shiuan Peh与Bhavya Daya等研究人员们还将以 Linux 平行版本展开SCORPIO协议测试。一旦经验证可行,Li-Shiuan Peh计划发布以Verilog硬件描述语言(HDL)编写的晶片微架构。

-

晶心科技推出突破性的RISC-V 27系列处理器及向量扩展指令处理器2020-01-03 3508

-

光子 AI 处理器的核心原理及突破性进展2025-04-19 3796

-

看看 XBOX360的核心处理器2012-02-27 2714

-

分享:中国造ARM架构处理器:完胜英特尔x86处理器?2015-11-19 3959

-

RISC架构在ARM微处理器的应用2019-07-15 2233

-

大小核设计架构对多核处理器有哪些影响?2019-09-02 4014

-

浅谈ARM处理器架构2020-08-18 4205

-

微处理器架构的后起之秀——RISC-V2023-04-14 591

-

处理器核心2009-12-17 9289

-

Intel宣布新处理器 48核心胶水封装2018-11-05 791

-

新架构新动能,64核心的EPYC处理器带来全新体验2020-01-09 3230

-

音频处理器的架构_音频处理器的延时怎么调整2020-04-09 5863

-

EDA行业与微处理器设计共同面临的挑战2022-04-12 2091

-

HPC处理器的多核架构挑战2022-07-14 1904

-

处理器架构与指令集2023-04-26 8234

全部0条评论

快来发表一下你的评论吧 !