FPGA工程师的研发之道——总线的研究

FPGA/ASIC技术

描述

如果设计中有多个模块,每个模块内部有许多寄存器或者存储块需要配置或者提供读出那么实现方式有多种,主要如下:

实现方式一:可以在模块顶部将所有寄存器引出,提供统一的模块进行配置和读出。这种方式简单是简单,但是顶层连接工作量较大,并且如果配置个数较多,导致顶层中寄存器的数目也会较多。

实现方式二:通过总线进行连接,为每个模块分配一个地址范围。这样寄存器等扩展就可以在模块内部进行扩展,而不用再顶层进行过多的顶层互联。如下图所示:

那如果进行总线的选择,那么有一种极为简单的总线推荐被使用,那就是AVALON-MM的总线

ALTERA提出两种总线类型,分别是AVALON-MM,

AVALON-ST。分别用于连接memeory 和数据流的传送

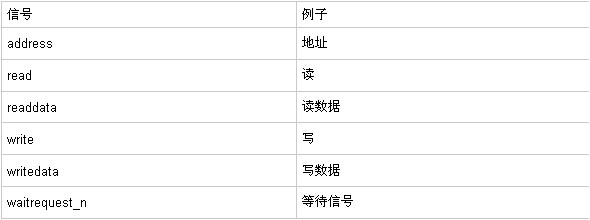

MM不是你想的意思,其英文为memory map。实现内存映射是其主要目的。主要信号包括如下表所示:

AVALON因此可以说是最简单实用的总线形态了。对于其操作来说,总线为同步类型的总线,写信号只需要在写使能有效时,同时提供写数据即可,而读数据等待信号无效时,读出数据有效。

同样数据类型读数据(readdata)和写数据(writedata)的宽度可以根据设计的需要灵活配置为(8,16,32----256---1024)BIT等值。即可以支持非常大的位宽,但普通应用,只需要(8,16,32,64)BIT等即可满足应用。

那假设总线宽度32,基本上主流的数据总线的宽度。如果需要更细粒度的划分,确定读写某个字节有效,那么byteenable信号也是必须的。其需要4bit来标示32bit(4个byte)中那个有效,每一BIT表示一个字节,因此如果要完全表示所有的字节有效,因此字节有效信号的宽度为(数据总线的宽度/8)。AVALON还可以有burst的操作。主设备可以通过burstcount设备确定brust的长度,为2的n-1次方。

对于普通的应用,通过上述表格中的基本操作即可满足需求,这也正是AVALON-mm总线的优势。此外模块按此标准提供连接接口,各种模块可以挂在NIOSII的片上系统上。

如果模块之间为点对点的连接,同时传递大数据量的操作,那么的AVALON-mm总线就不太适合,因此AVALON_streaming总线就适合这种应用场景。

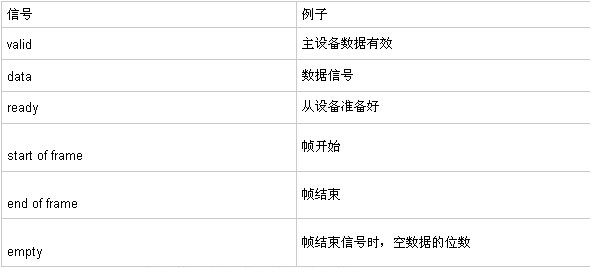

AVALON_streaming总线本质上是一种同步并行总线,即在同步时钟状态下,使能有效代表传递数据有效。其基本信号如下表所示:

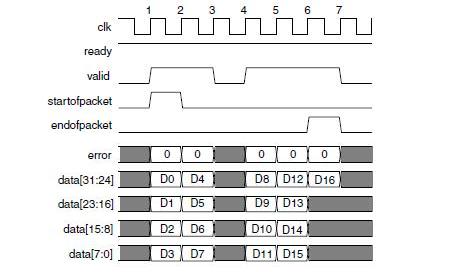

从上图中,可以看出各信号在数据传输中的作用,对于从设备获取数据的处理,就是VALID有效时,数据有效的采样操作,非常简单方便,易于处理。如果从设备设定ready永为1,则表示没有反压的机制,则主设备,可根据自身收包情况一直向从设备发送数据包。此外还有其他辅助信号,可以根据设计需要进行添加。

使用总线使模块标准化,便于代码的移植和设计复用。同时标准总线的设定和统一定义也利于项目团队代码的标准化,便于理解和传播。

下文将介绍两种其他应用较广的总线形态,AHB(AMBA)如果说在PC时代,垄断PC江湖的是WINTEL(微软和英特尔),那么在移动互联网时代,最具有这个潜质的就是谷歌的andriod操作系统和ARM芯片。基于ARM公司授权的各型ARM处理器,基本上在各型嵌入式终端设备占据了垄断地位。“背靠大树好乘凉”,因此,用于作为ARM处理做片上系统互联的AMBA总线标准亦成为业界应用最广泛的标准。

AMBA总线事实上为三个总线标准的合集,分别是AHB、ASB、APB。ASB已逐渐被AHB所取代,现在使用最广泛的为AHB和APB总线,以及最新的扩展AXI总线。实际上,现今系统设计中,经常会借鉴AHB或APB总线标准,用于设计各种IP和片内模块之间的互联。首先来说AHB和APB总线,一家公司为什么会退出有两种类型总线,这是因为AHB一般认为其具备更高的性能和总线吞吐能力,而APB为低速总线,用于连接低速外设。两种总线互补,能够在性能和功耗方面进行互补。

如上图所示

:AHB总线与APB总线在一个嵌入式系统中的应用场景。

分别用于连接低速设备和高速设备。下表列举其一些主要的差别。

作为单次传输来说,AHB与APB的主要区别在AHB周期不固定,操作完成标示由从设备返回hready标示,而APB周期固定。作为burst传输来说,AHB支持增量和回环两种方式的突发。举例说,增量就是挨个地址自加,如总线宽度为32,地址每次自加4(字节)。而回环,比如当前地址为0xA4,而回环突发操作位0xA4, 0xA8, 0xAC, 0xA0。这种突发方式对于一些cache读写内存是非常有用的,这样可以把0xA0-0xA15十六个内存地址一次性读出。如果设计一条这样的cache line,地址0xA0-0xA15其高位地址一致,便于匹配,这样这16个字节可以通过一次突发就能全部填满。(即回环这种设计与处理器的cache结构是相关的,现在的cache line有逐渐扩大的趋势,一般64字节也较为常见)。

由于支持多个主设备和多个从设备进行交互,那么对于多个主设备之间就存在竞争。(从设备之间存在竞争否?从设备之间是通过地址区分的,被动接受主设备的访问,不会存储竞争的问题。)因此如何解决竞争,那就需要仲裁,即主设备谁需要访问总线,则发起HBUSREQ,而仲裁器收到HBUSREQ,返回给相应主设备HGRANT。此时该设备才能访问总线。除此之外AHB还有其他一些信号,用于辅助整个系统的传输,感兴趣的同志,可以看一下AMBA的总线规范。值得一提的是,作为一个总线规范,其提供了全集的解决方案,而作为实现部分,只需要在满足规范的前提下,实现必要的功能即可,例如AHB总线中规定,其突发最大可1K字节,但是作为一个从设备,不一定需要支持这么大的操作,即实现功能可在总线框架内进行裁剪,选择实现支持的类型即可。

在FPGA内部设计中,经常有多个主设备访问同一从设备的例子,例如内部多个模块都需要访问外部存储器,其实现方式有多种,通过AHB的连接架构,可以实现一个标准、可扩展的接口单元,用于访问外部存储器。并且可以作为IP使用。AHB从设备只需要根据需要,支持某些burst传输即可。

随着SOC(片上系统的发展),对于高带宽、低延时的总线需求更加迫切,ARM公司适时退出AXI(AMBA3.0)作为扩展。

上图分别是AXI接口的读写操作,分别可以看出,对于AXI总线来说,其有5组独立的总线,分别是写地址,写数据,写响应,读地址,读数据信号。地址和数据信号分开,每组都有自己的控制信号。

每个通道中间没有时序关联,如何进行操作的?举例来说明,例如读数据操作,实际上,主设备向从设备中写了一个读的命令,包括读地址,burst大小,方式等。收到后从设备按照相应的命令读取相应大小的数据,传回主设备,其操作可以简化的看做两个缓冲区类型的操作,主设备将读命令写入从设备的命令缓冲区,从设备取出后,根据命令将相应的数据返回给主设备的接收缓冲区中。这种操作的好处显而易见,能够最大限度的减少总线的开销,因此其读与读操作之间独立,不用等待读回,就可以发送下一次的读信号。写操作的流程亦然。

对FPGA设计来说,例如xilinx的接口IP(DDR例化时的接口),都已支持AXI的接口。FPGA工程师熟悉相应的总线接口信号和特点,对于技术方案选择,IP使用和验证,都是非常重要的。尽量在设计中选择标准总线接口,对于设计复用,模块共享来说,则是必由之路。而模块(IP)复用的益处随着设计不断增大将会不断显现。

-

#FPGA 本科生也能成为FPGA研发工程师明德扬助教小易老师 2023-09-23

-

招聘FPGA研发工程师——北京市电加工研究所2014-07-02 3076

-

招聘:软件工程师(数字信号处理方向-FPGA)、硬件工程师2015-04-25 3810

-

招聘 电子研发工程师2016-07-22 3608

-

转:ARM学习大纲——资深工程师的进阶之道2016-08-30 5181

-

【招聘】电子研发工程师 硬件工程师2016-09-13 4833

-

资深工程师的进阶之道2016-09-27 7583

-

诚聘硬件研发工程师(FPGA)2016-11-14 3123

-

国内知名企业招聘FPGA研发工程师2017-03-07 2447

-

【上海】诚聘FPGA研发工程师2017-07-31 2246

-

诚招“FPGA工程师、嵌入式系统开发工程师”2018-01-13 3527

-

想做硬件研发工程师需要学习的课程有哪些?2018-03-19 5961

-

有在华为的FPGA工程师吗?我是一名在读研究生,学的也是FPGA,想去华为,请教一下~~~2019-04-01 7236

-

!!!!!!!高薪诚高级FPGA工程师,Base广东佛山2021-10-22 1290

-

FPGA工程师需要具备哪些技能?2023-11-09 2452

全部0条评论

快来发表一下你的评论吧 !