射频前端软硬体技术跃进 SDR系统更臻成熟

RF/无线

描述

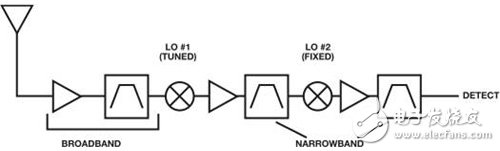

在传统的超外差(Superheterodyne)架构中,类比电路负责处理宽频前端,甚至有些包括窄频中频(IF)级(图1)。在类比与数位格式之间的转换动作离前端电路相当远,可能位于中频级或甚至位于基频级。此一主要的类比做法数10年来已经有效导入大量的消费性产品市场,并一路渗透至先进的雷达等射频应用上。

然而,系统设计人员面临现今复杂多变的频宽、格式、频率以及效能等射频设计需求时,这样的拓扑已不再适用。目前的无线电系统须支援位于跨广阔频谱的多重频段,并支援不同类型的调变(包括先导性QAM、多阶式、OFDM等的基本调幅(AM)和调频(FM))。如此一来,无线电系统将不再只是与无线电有关,而须以在复杂的电子设计、雷达干扰系统中,透过更为宽广的频宽进行多重讯号侦测、解码及实现对策。

图1 传统超外差架构示意图

因应多频多模设计 无线电系统改搭SDR架构

在单一系统中整合所有射频功能需要多重、平行的频道,而每个频道采用一个特定频率、格式与调变方式,包括新的物料、元件,以及功率消耗的影响都导致传统射频设计不切实际。因此,设计人员便开始将固有类比射频世界,与处理器相容的数位世界之间的讯号转换,并移到更加靠近天线的位置,在用以接收讯号的低杂讯放大器(LNA)后马上处理,并放在用以传输讯号的功率放大器(PA)之前,如此一来,单一硬体讯号链可一用再用,进而取代传统做法。

目前较新的无线电系统设计,係采用一颗主控处理器,通常是现场可编程闸阵列(FPGA),以韧体进行讯号处理、解码与分析,如此便可最小化甚至省去本地振盪器、混频器和其他频率与特定频宽元件的需求。

藉由执行不同软体程式码区块与演算法,让捷变收发器(Agile Transceiver,或译为敏捷性收发器)得以处理众多的讯号、频率与格式。在有些应用中,这样弹性且多变的架构被称为软体定义无线电(SDR),直接数位或数位无线电,不论是针对无线电或是雷达,这种灵敏度不只是一种有吸引力的方法,在因应复杂且不断演进的系统与产品需求上,它是强制必要的。

ADC/DAC跃居SDR射频设计要角

捷变收发器的好处是明确且广为人知的,但是要将它们落实却相当困难。当然,工程师需要一个有足够记忆体支援,并具备快速且效能强大的处理单元(即FPGA),不过这点在大部分设计中并非敏捷性无线电的关键项目。

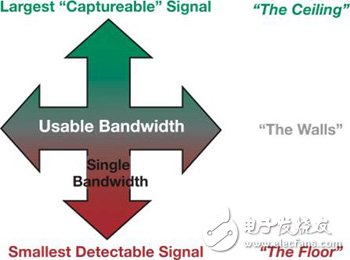

真正的挑战是在ADC与DAC转换器须满足各式各样的参数,以及极为严格的效能规格。由于SDR和捷变收发器可带来极高的资料率,因此在无线电系统中,也须具备一种对极高资料率有效且有效率的数位界面,并与FPGA设计相容。无庸置疑,新一代无线电系统内建的ADC和DAC转换器效能,将决定最终所能达成的讯号撷取与范围,以及许多其他系统功能规格(图2)。

图2 转换器决定有多少资讯可通过类比域与数位域之间。

为开发一款合适的射频前端转换器,有一些已经广为人知的转换器参数,当然必须提升到新的水準。基本的传统参数诸如转换速度、解析度、积分与差动非线性(INL/DNL),以及撷取/稳定时间仍受重视。

但是现在,除前述参数以外,有一些较少为人知的参数在定义最大化潜在系统效能上,正扮演着相当大且复杂的角色,包括讯号杂讯比(SNR)、失真和总谐波失真 (THD)、取样抖动、时脉抖动、讯号对杂讯和失真(SINAD)、有效位元数(ENOB)、无寄生动态范围(SFDR)和杂讯频谱密度(NSD)等。设计工程师也须针对诸如处理增益这类讯号概念增进设计知识,并进一步了解在各种不同的参数之间的取捨与相关性。

直到最近,宽频单芯片转换器根本不用提供所需的转换率及其他规格,过去唯一的设计解决方案是交错两颗或更多较低速的转换器,但这种方案除成本与功耗更高、尺寸更大之外,还有许多严重的缺点,尤其交错型转换器需精準的同步化时序讯号以维持转换效能,并达到目标的效能水準,这在实现实际设计与电路板布线上非常困难。

至于最新的单芯片转换器,例如亚德诺半导体(ADI)的AD9631,即提供这些宽频应用的所有目标规格,能让雷达干扰电子设备在更宽广的频宽内对讯号进行辨别并且动作。

这颗转换器的核心效能,只是SDR系统设计迈向成功、可行的一部分,适用于这些宽频前端应用的转换器以极高的资料率,本质上产生接收位元,成为一种新的数位界面做法。有史以来,转换器使用平行界面往返转换资料(图3),当此界面的最大速率约500Mbit/s无法再支援该需求时,转换器供应商转而改采串列式低电压差动讯号(LVDS)互连,因该界面提供更高的速度(约1Gbit/s)与更低的电压漂移,再加上其简化的布局,也能增加杂讯免疫力。不过,即使 LVDS在此处也达不到需求。

图3 转换器数位界面配置图

因此,一种新型界面标準--JESD204变得愈形重要。此标準定义一种介于ADC与DAC转换器和相关处理器(主要是 FPGA)之间极高速、多通道的串列界面。它不只以最高达12.5Gbit/s传输速率支援资料本身的传送,也附加一种尖端的资料格式与复杂的协定,用以建立传送通道、最小化串音杂讯,以确保资料的错误标记、定义交握。

与此同时,该界面也允许多重转换器被连结到单一处理器(在一些应用诸如MIMO前端中,此为必要规格。)

扣连软硬体供应链 芯片商加速推展SDR设计

除提升转换器上的效能需求外,无线电系统中的FPGA也须随之升级。它必须处理大量资料,支援传送与接收模式,代表它须有一个在GHz范围内的时脉率,同时还须具有一个处理核心由其设计与实作最佳化,并搭配韧体做为一个有效率的即时资料处理引擎,以在低功耗前提下,执行复杂的演算法。

高效率、最佳化宽频的转换器和与它们相关的高速FPGA,都是造就成功且即时的捷变无线电收发器设计的必要因素,但是这些条件仍然不够。由于元件的复杂度,互连格式与协定的挑战,和电路板布线细微化,现在「单打独斗」或者几乎独自开发是不可行的。跳过别人已经经歷并解决过的问题,而试图重新发明轮子的做法也不实际,况且设计的问题别人已经克服了。简而言之,风险很高,而且市场竞争很激烈。

要让一台基本的系统启动运行并不是一件小事,为使它通过目标的侦错与认证,设计工程师须从IC供应商处及第叁方伙伴处得到深入的支援,除得到捷变收发器的基本硬体功能外,还有复杂演算法,以及测试验证的挑战都需多方面的支援策略。

那就是何以有一个与转换器供应商相关连的趋势,以ADI为例,该公司已发展出一套完整的开发生态系统,包含参考设计、开发工具、HDL程式码、Linux 驱动软体,以及与FPGA供应商建立的合作关係,确认在FPGA、FPGA夹层卡(FMC)和先进的侦错工具之间的互通性。

不仅如此,射频前端元件开发商也须与独立的第叁方技术合作伙伴组成策略联盟,以发挥各自的技术专长,并共同整合出完整的射频子系统设计,从天线到处理器,乃至于演算法开发、编码及特殊应用等。

综上所述,SDR和捷变收发器设计面临的技术挑战包括元件、软体效能,以及多重面向设计考量,射频前端元件开发商须达成更高的元件规格,并提供评估工具、应用、参考设计,以及第叁方伙伴的Know-how和产品支援,才能帮助无线电系统研发团队更容易达成多重设计目的,并兼顾终端产品的成本与时间目标。

关于作者

-

cjz0723

2014-08-14

0 回复 举报东莞市俊致电子科技有限公司是一家从事于物联网行业,专注于无线数据传输,无线透传模块,WIFI模块、3G/4G转WIFI、 ZIGBE模块、2.4G视频模块、DTU/RTU终端设备无线产品的研发、生产、销售与服务一体的高新科技技术企业。同时也从事了移动通讯模块2G/3G/4G/WIFI的研发\生产\销售,为广大客户提供全方全的设计方案, www.dgjun.com 收起回复

cjz0723

2014-08-14

0 回复 举报东莞市俊致电子科技有限公司是一家从事于物联网行业,专注于无线数据传输,无线透传模块,WIFI模块、3G/4G转WIFI、 ZIGBE模块、2.4G视频模块、DTU/RTU终端设备无线产品的研发、生产、销售与服务一体的高新科技技术企业。同时也从事了移动通讯模块2G/3G/4G/WIFI的研发\生产\销售,为广大客户提供全方全的设计方案, www.dgjun.com 收起回复

-

介绍SDR的技术原理 以SDR LTE系统为例进一步解析SDR系统的工作流程2019-05-11 4553

-

什么是射频前端?2019-07-30 5260

-

采用射频前端的小卫星通信系统工作原理是什么?2019-08-09 2677

-

接收机的射频前端设计怎么实现?2019-08-22 4726

-

射频开展优势明显 前端市场潜力巨大2019-12-20 3834

-

具有射频监测能力的雷达接收前端技术介绍2020-12-21 1542

-

硅锗技术改善射频前端性能2006-05-07 848

-

智能天线射频前端电路的研究和设计2009-10-23 641

-

小卫星通信系统射频前端设计2011-08-20 2846

-

满足通讯市场应用需求的SDR系统2017-02-10 2698

-

SDR的技术原理介绍及案例分析2017-11-21 40054

-

基于SDR架构的前沿数字设备发展简述2017-12-13 2815

-

射频前端和射频器件详解2018-10-27 56044

-

如何使用PLL技术实现接收机射频前端的设计2020-09-23 1033

-

射频前端和射频芯片的关系2023-09-05 4358

全部0条评论

快来发表一下你的评论吧 !