基于FPGA的USB3.0 HUB设计方案

FPGA/ASIC技术

描述

USB总线是目前最为成功,应用最为广泛的外设接口。随着时代的进步和发展,电子产品、手持设备、超大容量的高清视频设备以及千万像素的数码相机等设备的需求越来越高,USB接口规范也需要相应地进行不断地更新和升级。USB3.0的最高理论速度达到了5Gbit/s,向需要更大电力支持的设备提供更好的支持和电力供应,它在USB2.0的基础上增加了新的电源管理功能,采用全双工数据通信,提供更快的传输速度,并且向下兼容USB2.0和USB1.1设备。USB体系主要包括三个部分:主机,设备和物理连接。主机通常是PC或者主机控制器;设备是指常用的U盘、带USB的摄像头、相机等设备;物理连接就是通常用的传输线,在USB3.0系统中,采用了对偶单纯形四线制差分信号线,因此可以支持双向并发数据流传输,这也是USB3.0相比于USB2.0设备速度提升的关键因素。

HUB是USB系统中的重要组成部分,且能够应用在大多数操作系统,它是建立主机与USB设备之间的桥梁。作为一类特殊的USB设备,可以同时将一个接口转换为多个接口,为用户提供了效率和便捷。

1. USB3.0 HUB的简介

1.1 USB3.0 HUB的基本组成

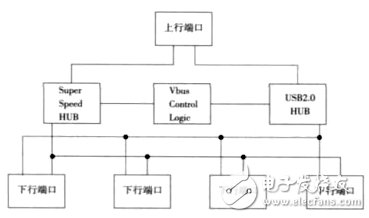

根据最新USB3.0的协议规定,USB3.0 HUB主要由Super Speed HUB,Vbus ControlLogic,USB2.0 HUB以及上下行端口组成。由于USB3.0是向下兼容的,所以它有完整的USB2.0 HUB设计,而Super Speed HUB部分就是USB3.0 HUB区别于USB2.0 HUB的主要部分。USB3.0 HUB基本结构如图1所示。

图1 USB3.0 HUB的基本结构

1.2 USB3.0集线器的功能

USB3.0 HUB是USB系统中的重要部分,它的基本功能如下:

1)基本连接功能。

2)电源管理功能。USB3.0能够提供900mA的电源,这样就可以给那些连接USB3.0的设备更快更好地完成充电。由于新的接口提供了额外的两条线,900mA的电力支持能够驱动无线适配器,这样在900mA的高电力支持下可以摆脱靠线缆连接的必要性。在大量数据传输的同时,空闲的设备可以自动进入低功耗状态,给正在传输的设备提供更好更快的性能支持。

3)设备连接和断开检测。

4)总线的错误检测和恢复。

5)HUB3.0的自动挂起和恢复功能。

6)向下兼容,下行端口同时支持高/低/全速设备。

2. Super Speed HUB的设计

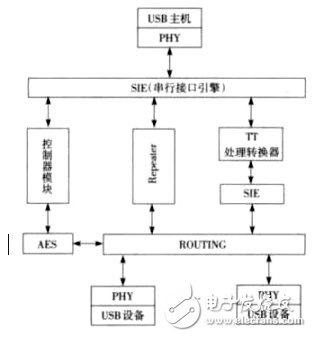

USB3.0 HUB是一种便携的低成本的USB3.0扩展接口,它的下行端口面向USB设备,上行端口面向PC主机或者嵌入式主机控制器,速度由上行端口的主机来决定,同时它在下行端口给设备提供连接和断开的检测,根据USB3.0最新协议规范,要实现上节所述各项功能设计。Super Speed HUB的整体构架如图2所示,包括SIE、控制、处理转换、中继、路由、AES加解密等部分。

图2 USB3.0 HUB的整体构架

2.1 SIE(Serial Interface Engine)模块

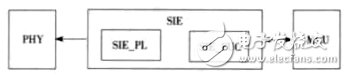

Super Speed HUB中的SIE模块处理USB规范中物理层和协议层的协议解析,它主要实现包的识别与产生、比特填充和提取、时钟与数据分离、NRZI编码和解码、PID(包标识符)的产生和检测、CRC校验码的识别和产生、地址检测等。SIE模块设计中,分为SIE_PL和SIE_FUC两个部分。SIE_PL模块负责数据包的解析与组织,PID(包标识符)产生与检测、CRC校验识别与产生、地址检测等。SIE_FUC模块主要实现SIE模块与MCU的接口逻辑功能。另外,为了使本系统设计更加稳定,SIE模块中采用跨时钟域的设计,一个是本地的48MHz的全局时钟,另外一个是USB主机从接收到的数据流中采样接收的12MHz数据时钟(即将48MHz本地全局时钟4分频得到)。SIE模块设计框图如图3所示。

图3 SIE模块设计框图

2.2 HUB控制器模块

HUB控制器主要完成HUB的管理及控制,实现与主机的交互。主机端通过类请求与HUB控制器模块通信,取得HUB端口的描述符,并且完成USB HUB及其下行端口的管理和控制。主机通过向端点0发送类请求和标准请求来实现HUB的枚举过程。

2.3 AES模块

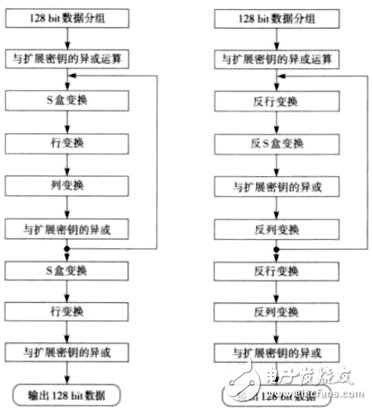

AES是一种基于置换和代替的算法,它实现加解密功能。在USB3.0 Super Speed模式下,根据用户的需求,当数据从上行端口向下行端口传输时,对数据进行加密,以防止信息窃取。同样,在数据由下行端口向上行端口传输时实现其解密过程。AES算法加解密过程如图4所示。

图4 AES算法加解密过程

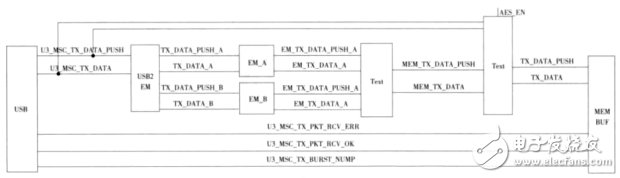

在加解密的过程中,由于USB3.0 HUB的传输速度可达到3200Mbit/s,但是AES的加解密IP在250MHz的吞吐率下最高速率只能达到2400Mbit/s,因此在加解密的过程中需要2个AES来实现其功能。图5是USB3.0 AES加密原理图,从图中可以看到上行端口会向EM_A发送奇数128bit数据,向EM_B发送偶数128bit数据,同时,Mem_buf模块也会轮询地从EM_A模块和EM_B模块接受数据。而在以前的USB2.0的模式下,数据位宽只有8bit,全速的带宽为480Mbit/s,所以只需要1个AES就可以。

图5 AES算法加密原理图

2.4 ROUTING模块

ROUTING模块即路由逻辑模块,它的作用是根据连接到下行端口设备的速度来决定将下行端口连接到中继模块还是连接到TT模块。由于在USB3.0HUB的上行端口中的速度是高速的,而下行端口则不确定为高速、全速或者低速,所以当下行端口设备的速度为高速时,ROUTING模块连接到中继模块,如果下行端口设备的速度为全速或者低速时就连接到TT模块。

2.5 Repeater中继模块

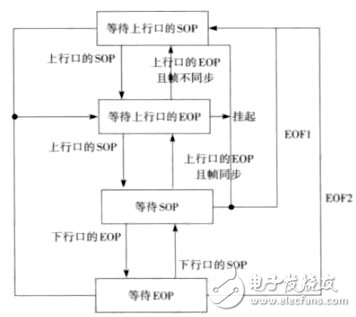

集线器中继模块在HUB的数据转发中起到建立和拆除上行端口和下行端口之间的连接,并且处理集线器的挂起和唤醒的作用。中继器把上行端口的数据发送到下行端口,把下行端口的数据发送到上行端口,并且要用本地时钟来从端口上发送和接受数据。它以数据包为单位控制端口的建立和连接以及HUB的唤醒和挂起。如图6所示为Repeater的连接状态机。

图6 Repeater的连接状态机

2.6 PHY模块

PHY模型就是通常所说的USB物理收发器模型,它的作用是实现数据的串并转换。因为在上行端口是并行数据,而在面向设备和电缆中的下行端口是串行数据。

2.7 TT处理转换器

TT模块的作用是完成传输事务转发和速度的匹配。当上行端口在高速环境下运行而下行端口在全速或者低速下运行时,TT处理转换器就是将高速事务转换成低速事务。由于要满足速度的匹配,因此TT处理器必须采用缓存的方式来存储,在缓存的上行端口是一个高速处理器,用来处理高速数据的收发;缓存的下行端口是全速和低速处理器,用来处理全/低速数据的接受和发送。

3. FPGA仿真与验证

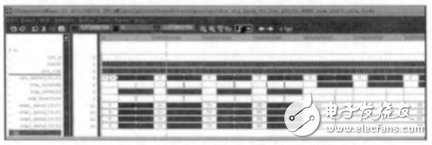

为了更好地完成仿真和验证,采用ModelsimSE和Navos公司的Debussy软件。首先搭建仿真环境,包括编译测试文件、仿真调用文件、引导文件、宏定义文件以及激励文件。首先将C语言的驱动程序在Linux环境下转换为二进制的kvout激励文件,把二进制的kvout文件存储在外挂的Flash中然后再存储到内置的RAM中,使其成为发出指令的源头;同时USBDevice的行为级模型也会装载部分命令以达到仿真的目的。如图7所示为USB3.0HUB高速数据批量传输仿真结果。

图7 USB3.0HUB高速数据批量传输仿真(截图)

图中数据包的总大小为4096byte,rst_n为系统复位信号,clk30为主机端12M时钟,pci_clk为本地时钟,cpu_datao是从主机发送出的数据,utm0_data,utm1_data,utm2_data,utm3_data分别为经过USB3.0HUB扩展后的4路高速信号,Utm_rxready,utm_rxvalid,utm_rxactive分别为端口的控制信号。

为了加强整个设计的可靠性,必须进行FPGA验证,FPGA验证选择的是Altera的StratixIIS180开发板,采用QuartusII将RTL级的verilog代码进行变异并且综合成网表,然后通过USB-blaster下载线下载到FPGA测试版中,另外激励文件是在Linux环境下编译产生的,并且通过EJTAG下载到测试版中。把激励文件下载到FPGA板子中后,把HUB的上行端口连接到USB的主机,此时如果主机检查出有USB HUB连接,会产生1个复位信号;在HUB复位后,USB主机向USB Device发送令牌包,并且对HUB进行枚举,主机识别出该HUB;当主机对USB3.0 HUB成功枚举后按照USB协议进行数据传输。

在传输速率上,可以通过USB3.0 HUB传输1个比较大的文件,并且用ATTO DISK BENCHMARK软件来测试其读写速度,通过ATTO可以显示出读取数据可以提高到1088Mbit/s,写入速度可以达到840Mbit/s(USB2.0 HUB的读写速度分别为240Mbit/s和184Mbit/s);很显然这个读写速度比USB2.0的提高了5~6倍。当然由于软件和硬件的各种原因,这个实际的传输速度离其理论最大值5G bit/s有一定的差距,但已基本实现其高速传输的功能。

从verilog的功能仿真、时序仿真和FPGA验证表明,USB3.0 HUB基本实现了高速数据的传输,达到了预期的效果。

4. 总结

USB及HUB接口是目前计算机以及微控制器中最常用的通用高速接口,它可以连接串口、U盘、音频、视频、手机、相机等绝大多数的外设设备。USB3.0正在以其高速度、高性能、高可靠性、低成本等特点逐渐代替更多的USB2.0产品,成为通信电子市场的主要接口。本文中设计的USB3.0 HUB实现了多媒体数据的高速同步及时传输;更佳的电源管理功能以及支持AES加密解密等功能,这些都将促使它在市场上迅速普及。但是USB3.0及其HUB依旧有自己的瓶颈,比如在某些应用中需要尽可能高的吞吐量时,线缆的长度会受到限制;同时电缆的材质以及信号的质量也会在整体上影响传输的效果,所以在传输百兆以上数据流时,所用线缆最好不要超过3m。

-

基于FPGA的USB3.0回环传输测试方案2023-10-01 7878

-

基于FPGA的USB3.0 HUB设计方案2023-06-09 4322

-

4端口USB3.0 VL813方案2022-08-04 1393

-

基于VL813芯片的USB3.0 HUB方案2022-05-27 6351

-

FPGA和USB3.0通信-USB3.0 PHY介绍2021-12-20 2105

-

USB3.0 HUB的资料2021-11-16 2035

-

FPGA和USB3.0通信-USB3.0 PHY简介2021-11-09 10952

-

分享一个不错的基于VL813的USB3.0 HUB方案2021-06-15 2529

-

全部开源USB3.0 HUB 1拖4电路设计方案2020-11-04 9310

-

USB3.0 HUB方案之VL817-Q72020-03-13 21456

-

4端口的USB3.0的HUB用的最多的是GL3520方案2019-07-30 36520

-

实现了多媒体数据的同步传输的USB3.0 HUB设计方案2018-11-01 13260

全部0条评论

快来发表一下你的评论吧 !