基于JTAG口对F1aSh的在线编程平台

实时应用开发

描述

随着嵌入式技术的发展,在一些高端的掌上设备中,都使用了Flash芯片,如Compaq的iPAQ、联想的天祺系列等产品。但对于研发人员来说,在开发阶段需要大量的程序调试,就意味着要对F1ash进行擦除和改写的工作,因此,如何对F1ash进行在线编程是问题的关键所在。本文介绍一种通过 JTAG对Flash进行的在线编程方法。

1 JTAG简介

JTAG(Joint Test Action Group)是1985年制定的检测PCB和IC芯片的一个标准,1990年被修改后成为IEEE的一个标准,即IEEEll49.1-1990。通过这个标准,可对具有JTAG口芯片的硬件电路进行边界扫描和故障检测。

具有JTAG口的芯片都有如下JTAG引脚定义:

TCK--测试时钟输入;

TDI--测试

数据输入,数据通过TDI输入JTAG口;

TDO--测试数据输出,数据通过TDO从JTAG口输出;

TMS--测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST一测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

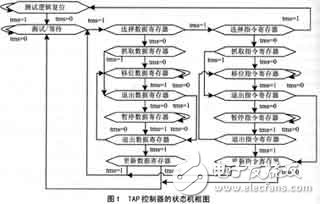

JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。图1为TAP控制器的状态机框图。

2 JTAG芯片的边界扫描寄存器

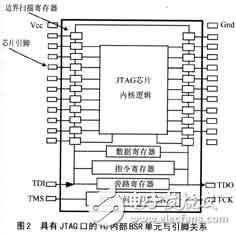

JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR(Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。图2为具有JTAG口的IC内部BSR单元与引脚的关系。

3 JTAG在线写FIash的硬件电路设计和与PC的连接方式

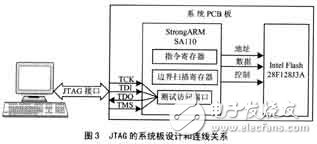

以含JTAG接口的StrongARM SAlll0为例,Flash为Intel 28F128J32 16MB容量。SAlll0的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SAll10的数据线和地址线及控制线与Flash的地址线、数据线和控制线相连。因 SAlll0的数据线、地址线及控制线的引脚上都有其相应BSC,只要用JTAG指令将数据、地址及控制信号送到其BSC中,就可通过BSC对应的引脚将信号送给Flash,实现对Flash的操作。JTAG的系统板设计和连线关系如图3所示。

4 通过使用TAP状态机的指令实行对FIash的操作

通过TCK、TMS的设置,可将JTAG设置为接收指令或数据状态。JTAG常用指令如下:

SAMPLE/PRELOAD--用此指令采样BSC内容或将数据写入BSC单元;

EXTEST--当执行此指令时,BSC的内容通过引脚送到其连接的相应芯片的引脚,我们就是通过这条指令实现在线写F1ash的;

BYPASS--此指令将一个一位寄存器置于BSC的移位回路中,即仅有一个一位寄存器处于TDI和TDO之间。

在PCB电路设计好后,即可用程序先将对JTAG的控制指令,通过TDI送入JTAG控制器的指令寄存器中。再通过TDI将要写Flash的地址、数据及控制线信号入BSR中,并将数据锁存到BSC中,用EXTEST指令通过BSC将数据写入Flash。

5 软件编程

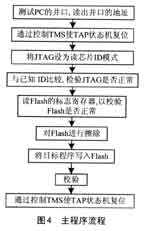

在线写Flash的程序用Turbo C编写。程序使用PC的并行口,将程序通过含有JTAG的芯片写入Flash芯片。程序先对PC的并口初始化,对JTAG口复位和测试,并读F1ash,判断是否加锁。如加锁,必须先解锁,方可进行操作。写Flash之前,必须对其先擦除。将JTAG芯片设置在EXTEST模式,通过PC的并口,将目标文件通过JTAG写入Flash,

并在烧写完成后进行校验。程序主流程如图4所示。

通过JTAG的读芯片ID子程序如下

void id_command(void){

putp(1,0,IP);//Run-Test/Idle:使JTAG复位

putp(1,0,IP);//Run-Test/Idle

putp(1,0,IP);//Run-Test/Idle

putp(1,0,IP);//Run-Test/Idle

putp(1,1,IP);

putp(1,1,IP); //选择指令寄存器

putp(1,0,IP); //捕获指令寄存器

putp(1,0,IP); //移位指令寄存器

putp(0,0,IP); // SAlll0 JTAG口指令长度5位,

//IDCODE为01100

putp(1,0,IP);

putp(1,0,IP);

putp(0,0,IP);

putp(0,0,1P);

putp(0,1,IP); // 退出指令寄存器

putp(1,1,IP); // 更新指令寄存器,执行指令寄存器中的

// 指令

putp(1,0,IP); // Run-Test/Idle

putp(1,0,IP); //Run-Test/Idle

putp(1,0,IP); //Run-Test/Idle

putp(1,1,IP);

putp(1,0,IP);

if(check-id(SAlll0ID))

error_out(“failed tO read device ID for the SA-1110”);

putp(1,1,IP);//退出数据寄存器

putp(1,1,IP);//更新数据寄存器

PUTP(1,0,IP); // Run-Test/Idle,使JTAG复位

putp(1,0,IP);//Run-Test/Idle

putp(1,0,IP); //Run-Test/Idle}

6 电路设计和编程中的注意事项

①F1ash芯片的WE、CE、OE等控制线必须与SAlll0的BSR相连。只有这样,才能通过BSR控制Flash的相应引脚。

②JTAG口与PC并口的连接线要尽量短,原则上不大于15 cm。

③F1ash在擦写和编程时所需的工作电流较大,在选用系统的供电芯片时,必须加以考虑。

④为提高对Flash的编程速度,尽量使TCK不低于6 MHz,可在编写烧写Flash程序时实现。

-

JTAG如何工作?是谁动了我的JTAG口?2023-12-04 2885

-

一文详解ash程序和login程序2022-10-21 5007

-

一种基于DSP和JTAG接口的FPGA系统在线编程设计2019-06-13 2486

-

STM32F100xx SWD在线编程参考手册2022-10-28 781

-

基于JTAG的在线编程2009-04-15 489

-

JTAG口及其对Flash的在线编程2009-04-16 783

-

通过JTAG 口对DSP 外部Flash 存储器的在线编程2009-05-15 634

-

基于JTAG 的在线编程2009-05-18 620

-

flash存储器在线编程2017-10-11 5818

-

JTAG口对DSP外部Flash存储器的在线编程设计方案解析2017-10-24 1186

-

JTAG仿真口电路设计2017-12-02 1927

-

jtag的基本原理与调试原理2017-12-10 12632

-

什么是JTAG口?今日带你深度了解JTAG口2021-03-17 13445

-

探讨一下JTAG口是什么?2022-07-26 2060

-

关于JTAG口,你了解多少?2023-06-07 3201

全部0条评论

快来发表一下你的评论吧 !

他们网站有白皮书可以下载,写得非常好,建议看看。 收起回复