ADI:16位10 MSPS ADC AD7626的单端转差分高速驱动电子线路设计

存储技术

描述

电路特点

16位10MSPS PulSAR ADC

经过优化的单端至差分驱动器

输入为2.4MHz时,SNR为88dB

电路功能

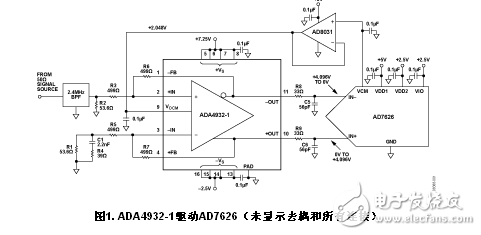

图1所示电路可将高频单端输入信号转换为平衡差分信号,用于驱动16位10 MSPS PulSAR® ADC AD7626。该电路采用低功耗差分放大器ADA4932-1 来驱动ADC,最大限度提升AD7626的高频输入信号音性能。此器件组合的真正优势在于低功耗、高性能。

AD7626具有突破业界标准的动态性能,在10 MSPS下信噪比为91.5 dB,实现16位INL性能,无延迟,LVDS接口,功耗仅有136 mW。AD7626使用SAR架构,主要特性是能够以10 MSPS无延迟采样,不会发生流水线式ADC常有的“流水线延迟”,同时具备出色的线性度。

ADA4932-1具有低失真(10 MHz时100 dB SFDR)、快速建立时间(9 ns达到0.1%)、高带宽(560 MHz,-3 dB,G = 1)和低电流(9.6 mA)等特性,是驱动AD7626的理想选择。它还能轻松设定所需的输出共模电压。

该组合提供了业界领先的动态性能并减小了电路板面积:AD7626采用5 mm × 5mm、32引脚LFCSP封装,ADA4932 -1采用3mm× 3mm、16引脚LFCSP封装),AD8031 采用5引脚SOT23封装。

电路描述

采用差分放大器成功驱动ADC需要正确平衡差分放大器的各端。

图1显示了ADA4932-1、AD7626和相关电路的原理图。在使用的测试电路中,信号源之后配置有2.4 MHz带通滤波器。该带通滤波器能抑制2.4 MHz信号的谐波,并确保只有目标频率的信号能够通过并由ADA4932-1和AD7626进行处理。

本例中信号源的特性阻抗为50 Ω,通过带通滤波器交流耦合到ADA4932-1。将信号源施加于ADA4932-1的正输入时,要求信号源也以50 Ω正确端接(通常情况下任何源阻抗均可)。选中端接电阻R2,以使R2与ADA4932-1输入阻抗的并联组合等于50 Ω。

为使ADA4932-1的两个输入端保持适当平衡和对称,与输入源阻抗等效的戴维南阻抗和端阻抗必须添加到反相输入端。在这种情况下,就涉及到滤波器的交流特性。

如图1所示,戴维南等效网络显示在ADA4932-1的反相输入端。频率为2.4 MHz时,此电路性能得到优化。C1和R4串联组合后,与电阻R1并联。频率为2.4 MHz时,C1和R4的复合串联组合等于55.6 Ω。与R1并联的55.6 Ω阻抗与戴维南等效电路在同相输入端的输入阻抗只有几欧姆之差。两个输入的匹配可确保输出对称、均衡且经过优化,可实现最低失真。

有关单端输入端接方法的详细说明,请参阅应用笔记AN-1026“高速差分ADC驱动器设计考虑”。此外,ADI公司DiffAmpCalcuator™设计工具大大简化了这一操作,并针对与差分放大器设计有关的其他问题提供了独到见解。

ADA4932-1差分驱动器的增益配置约为1(单端输入至差分输出)。由于50 Ω信号源以及在ADA4932-1输入端匹配的端阻抗的作用,相对于戴维南等效信号源电压,通道的净总增益大约为0.5。

使用配置为单位增益缓冲器的AD8031来缓冲AD7626的VCM输出电压(标称+2.048 V),即可设定ADA4932-1输出的共模电压。AD8031为ADA4932-1 VOCM引脚提供低源阻抗,并能驱动大型旁路电容,如图1所示。

当驱动AD7626(带开关电容输入的10 MSPS ADC)的高频输入时,ADA4932-1的作用尤其显著。ADA4932-1和AD7626 的IN+和IN-引脚之间的电阻(R8、R9)和电容(C5、C6)电路可充当低通噪声滤波器。该滤波器限制了AD7626的输入带宽,但其主要功能是优化驱动放大器和AD7626之间的接口。串联电阻将驱动放大器与ADC开关电容器前端的高频开关尖峰隔离。AD7626数据手册显示了20 Ω和56 pF的值。在图1所示电路中,这些值根据实际应用优化为33 Ω和56 pF。若要针对转换中的电路和输入频率对电阻-电容组合进行略微优化,只需改变R-C组合即可。但是切记,若组合不当,将限制AD7626的总谐波失真(THD)和线性度性能。此外,ADC带宽的增加会引起更多噪声。

ADA4932-1电源电压的选择也得到了优化。在电路中,对应于4.096V的内部基准电压,AD7626的输出共模电压(VCM引脚)为2.048 V,每个输入(IN+、IN-)在0 V和+4.096 V之间摆幅,发生180°错相,这提供了ADC的8.2 V满量程差分输入。对于线性运算的每个电源电压,ADA4932-1输出级需要大约1.4 V的裕量。当电源电压关于共模电压大致对称时,能获得最佳失真性能。如果选定-2.5 V负电源,则至少需要大约+6.5 V正电源才能关于2.048V共模电压对称。

实验表明,+7.25 V正电源可为2.4 MHz信号音提供最佳的总失真性能。

使用低抖动时钟源和AD7626的单音-1 dBFS幅度2.402 MHz输入,可产生图2所示的FFT结果:信噪比为88.49 dB,总谐波失真为-86.17 dBc。从图中可以看到,基波的谐波重新混叠到通带。例如,采样率为10 MSPS时,三次谐波(7.206 MHz)会在10.000 MHz-7.206 MHz = 2.794 MHz混叠到通带。图3所示为-6 dBfs幅度信号音的第二个FFT坐标图。

图2. AD7626输出,64,000点,FFT坐标图,-1 dBFS幅度,2.40173 MHz的输入信号音,10.000 MSPS采样率

图3. AD7626输出,64,000点,FFT坐标图,-6 dBFS幅度,2.40173 MHz输入信号音,10.000 MSPS采样率

计算信噪比和总谐波失真时,用整个奈奎斯特带宽的平均噪声取代了电路所用带通滤波器的通带准许通过的非谐波噪声。

该电路或任何高速电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、受控阻抗线路(如需要)、元件放置、信号路由以及电源层和接地层。(有关PCB布局的详细信息,请参见MT-031教程, MT-101教程 和高速印刷电路板布局实用指南一文。)

AD7626—典型连接和基准电压配置

AD7626的典型连接图。AD7626集成一个内部基准电压源,还可根据系统要求提供两个外部基准电压源。将 ADR280基准输出(1.2 V)施加到REFIN引脚可产生基准电压,然后由片内基准电压缓冲内部放大到正确的ADC基准电压4.096 V。ADR280可由用于AD7626的同一5 V模拟供电轨供电,同时使用片内基准电压缓冲。或者,也可以将4.096 V外部基准电压(ADR434 或 ADR444) )施加到ADC的非缓冲REF输入。此做法在多通道应用中很常见,在此类应用中,系统基准电压通常是分立缓冲的(使用AD8031),并且由所有ADC通道共享。ADR434和ADR444的配置也极其适用于单通道应用,此类应用需要较低的基准电压源温度系数(ADR434B和ADR444B最大为3 ppm/°C)。用于为放大器ADA4932-1供电的正供电轨也能为ADR434或ADR444的VIN电源引脚供电。

电路常见变化

经验证,采用图中所示的元件值,该电路能够稳定地工作,并具有良好的精度。虽然此电路为直流耦合,但应用于交流耦合也很常见。该电路的常见变化包括单电源电压、以差分方式驱动的输入以及需要信号衰减的输入。其它ADC驱动/差分放大器也可用于根据具体应用调整性能(如功率、噪声、带宽、架构等)。

如AD7626数据手册所示,当输入频率为1MHz或更低时,推荐使用驱动放大器ADA4899-1。如数据手册中AD7626典型工作特性一节的高频坐标图所示,使用ADA4938-1可通过最高达10 MHZ的高速信号有效驱动AD7626。

-

AD7626:16位、10 MSPS差分ADC的卓越性能与应用2026-04-01 136

-

CN0105 16位10 MSPS ADC AD7626的单端转差分高速驱动电路2021-06-04 1438

-

AN-1526:AD7625 16位6 MSPS脉冲星ADC的高速、精确、差分交流耦合驱动电路2021-05-20 937

-

AN-1575:AD7626 16位10 MSPS ADC的单端至差分高速驱动电路2021-05-15 850

-

AD7626:16位、10 MSPS、PulSAR差分ADC2021-03-20 837

-

EVAL-AD7626FMCZ,用于评估AD7626 16位,与系统开发平台板EVAL-SDP-CH1Z配合使用2019-08-15 2302

-

16位SAR模数转换器AD76262019-07-01 2767

-

AD7626 16位10 MSPS SAR转换器的性能特点介绍2019-06-06 5434

-

用于AD7626的Virtex-6 lm605板的LVDS时钟不起作用2019-04-03 2167

-

AD7626 16-Bit,10MSPS PulSAR差分ADC2019-02-22 734

-

请问ad7626的差分信号要求2018-09-10 2069

-

16位10 MSPS ADC AD7626的单端转差分高速驱动电路2013-02-01 1891

-

AD7626 pdf datasheet2008-08-14 1548

全部0条评论

快来发表一下你的评论吧 !