东芝新型TFET晶体管,使MCU功耗降至1/10

IGBT/功率器件

描述

东芝开发出了用于超低功耗MCU的新型晶体管技术,可将MCU的耗电量降至1/10以下,而且能够利用与现行标准晶体管(MOSFET)相同的CMOS工艺制造。东芝计划2017年投产配备该技术的MCU。设想的用途包括电池驱动型移动产品、可穿戴终端和传感器网络终端等。

在2014年9月8~11日举行的半导体器件技术国际会议“SSDM(International conference on Solid State Devices and Materials)2014”(茨城县筑波市)上,东芝发表了三篇与上述技术有关的论文。

工作电压降至0.5V以下

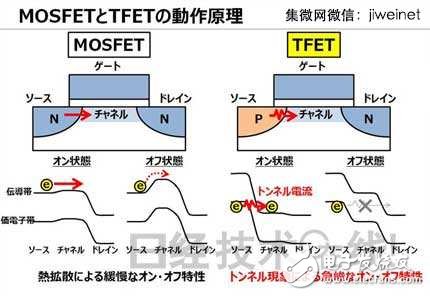

东芝开发的是名为隧道FET(Tunnel FET:TFET)的场效应晶体管。这是一种利用电子的能带间隧道现象控制开/关的晶体管,可通过使MOSFET的源极和漏极的导电型半导体(p或n)互补来实现。

TFET的特点是,与MOSFET相比能获得更为陡峭的开/关特性。MOSFET受电子的热扩散影响,表示开/关特性上升陡峭度的S因子只能减至约60mV/dec,而TFET能获得低于60mV/dec的非常小的S因子。

MOSFET与TFET的工作原理的区别

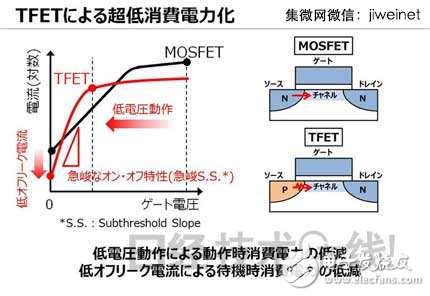

因此,TFET能以非常低的电压驱动,还能大幅减小关态漏电流。例如,工作电压“可降至MOSFET的1/2以下,也就是0.5V以下”(东芝半导体&存储产品公司半导体研发中心新器件技术开发部器件技术开发主任川中繁)。关态漏电流与MOSFET相比有望减小约2位数。工作电压低就能降低工作时所需电力,而关态漏电流小可削减待机时所需电力。

有望实现超低功耗

英特尔也将其视为新一代技术的有力候补

英特尔也是看中了TFET的潜力的企业之一。作为以低电压工作的新一代晶体管技术,该公司以前就在大力开发TFET。英特尔预定在SSDM 2014上就TFET发表特邀演讲,演讲题目为“Tunnel-FET Transistors for 13nm Gate-Length and Beyond”,由此可见,英特尔已将TFET作为10nm以后工艺的技术候补。

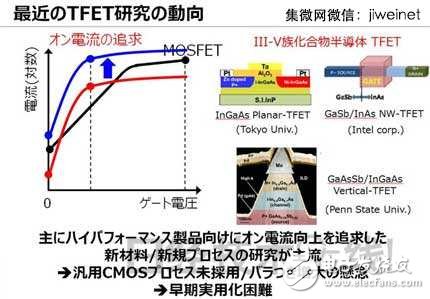

不过,以前就在推进开发的TFET存在一个巨大的课题,即无法获得充分的导通电流(驱动电流)。东芝半导体&存储产品公司半导体研发中心新器件技术开发部器件技术开发主任后藤正和介绍说,从TFET的工作原理来看,其开/关利用的是隧道现象,导通电阻比MOSFET大。因此,以前TFET的导通电流要比 MOSFET低3位数左右。

为弥补这个缺点,欲利用InGaAs和GaSb等III-V化合物半导体代替硅来实现TFET的研究逐渐兴起。这些材料与硅相比带隙更窄,因此可缩窄电子隧穿区域的宽度,相应地,能够提高导通电流。英特尔等在学会上发表的就是这种类型的TFET。

英特尔等大力开发

限定用途力争尽快实用化

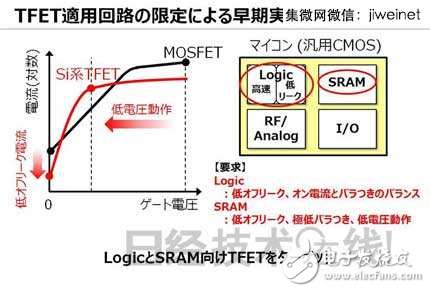

而东芝打算利用硅材料,实现能以CMOS工艺制造的TFET。这是因为,采用III-V化合物半导体的逻辑LSI用晶体管“连MOSFET都还没实现实用化,而TFET的技术难度比MOSFET更高”(后藤正和)。

东芝计划将TFET的用途也限定为“现实路线”,以尽快实现实用化。不打算将其用于智能手机用应用处理器等工作频率超过1GHz的用途,而是瞄准了重视耗电量、工作频率约为几十MHz的MCU。另外,并不打算将芯片上的所有MOSFET都换成TFET,只将其用于逻辑部分中特别重视低关态漏电流的区域和 SRAM。

计划将TFET用于逻辑部分中重视低关态漏电流的区域和SRAM

根据应用位置开发3种类型

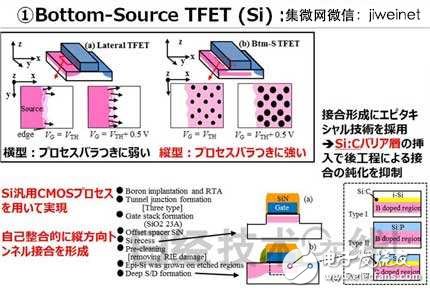

东芝此次开发出了可利用CMOS工艺制造,而且与以往的硅材料TFET相比在导通电流和工艺偏差方面更有利的TFET。此次开发的TFET有3种类型,分别根据设想应用的电路块对特性进行了优化。这三种TFET分别是(1)用于逻辑部分、关态漏电流小、导通电流和工艺偏差取得平衡的TFET;(2)用于逻辑部分、关态漏电流小、导通电流大的TFET;(3)用于SRAM、工艺偏差小的TFET。后两种是东芝和日本产综研的共同开发成果。

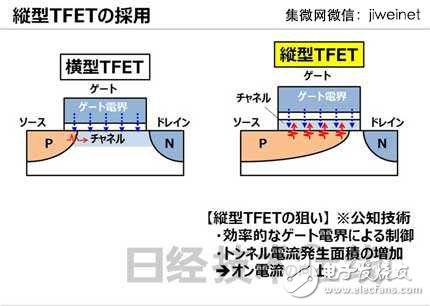

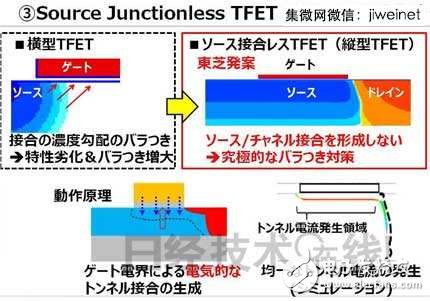

这三种TFET的相同点是,都采用了立式TFET构造。这种构造能将源极扩大到普通TFET(横式TFET)的沟道区域,隧道电流能沿着与栅极电场平行的方向流动。

采用立式TFET

采用这种构造有两个优点。首先,基于栅极电场的隧道电流控制性升高,因此能提高导通电流。其次,可扩大隧道电流流动区域的截面积,因此容易减小工艺偏差。

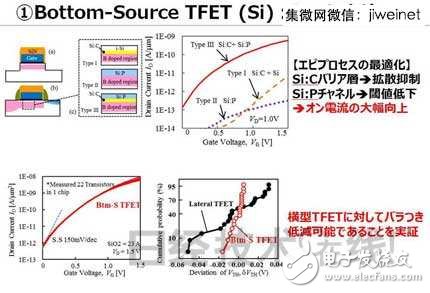

提高作为TFET缺点的导通电流

(1)是利用硅的外延生长,能以自对准工艺形成开/关特性出色的陡峭隧道结。形成隧道结时,在源极与沟道之间设置了防止源极中的添加杂质(B)扩散的 C(碳)掺杂层,还在沟道中添加P(磷)以降低阈值电压。通过这些措施,这种TFET的导通电流较以往的硅材料TFET提高了约一位数,还降低了工艺偏差。

利用硅的外延生长 )

导通电流大,工艺偏差小

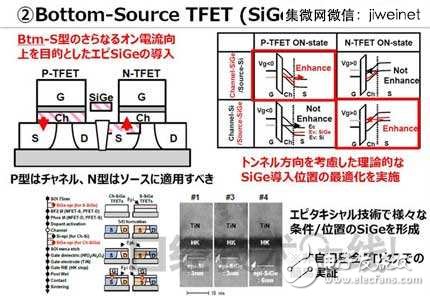

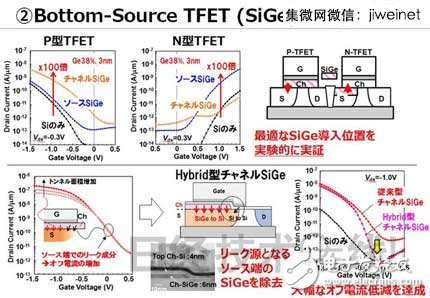

(2)利用了带隙比硅窄的材料SiGe,目的是在保持与CMOS工艺的亲和性的同时,获得比硅材料TFET更高的导通电流。

不过,即使源极、漏极和沟道全部采用SiGe,其效果也很小。东芝通过能带图推测了在构成CMOS的pFET和nFET的哪部分采用SiGe能提高导通电流。结果发现,在pFET的沟道和nFET的源极采用SiGe时,效果达到最大化。

与以往的硅材料TFET相比,这种TFET的导通电流提高到了100倍。通过部分去除源极端的SiGe,还抑制了采用SiGe造成的关态漏电流增大现象。

在SiGe的应用位置上下工夫

既能提高导通电流又能降低关态漏电流

采用无结构造将偏差降到最小

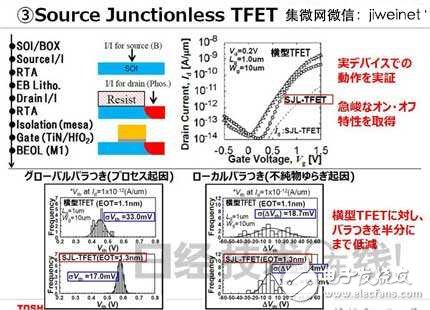

(3)采用去除了源极和沟道间的物理隧道结的“无结(Junctionless)”构造。这是此前不存在的“全新概念的器件”(后藤)。

据后藤介绍,立式TFET原本就采用了耐工艺偏差的构造,但为了形成隧道结而追加的制造工艺,使偏差不可避免地增大。因此,此次的构造弃用物理隧道结,利用加载栅极电场时耗尽层的扩展,以电气方式形成隧道结。对这种新构造器件的工作情况进行验证发现,其工艺偏差比横式TFET减少了一半。

去掉物理隧道结

偏差减半

今后,东芝将以量产为目标,开发把MOSFET和TFET配备在同一个芯片上的技术。其课题在于制造成本。TFET的制造工序数量比MOSFET更多,因此该公司打算使其在性能和芯片面积方面占优势,由此抵消成本增加的部分。计划使制造工序数“仅比MOSFET增加15%左右”(川中)。性能方面,计划使 S因子由目前的100左右降到60以下。

工艺技术“不打算采用(应用处理器使用的)最尖端工艺,而是利用65nm工艺或者更宽松的设计规则”(川中)。东芝计划在自家工厂量产这些产品。

-

什么是达林顿晶体管?2023-02-16 2097

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2575

-

1500W东芝最终晶体管PCB2022-07-21 712

-

一种被称为有机电化学晶体管(OECT)的新型晶体管技术2021-03-17 15584

-

如何改善晶体管的损耗2020-11-26 2191

-

晶体管简介2019-05-09 2271

-

晶体管的由来2019-05-05 2656

-

晶体管ON时的逆向电流2019-04-09 2146

-

隧穿场效应晶体管是什么_隧穿场效应晶体管的介绍2018-01-03 34648

-

为什么晶体管使用越久,功耗越低?2017-06-15 3758

-

东芝面向超低功率MCU开发隧穿场效应晶体管2014-10-08 1694

全部0条评论

快来发表一下你的评论吧 !