九项常被忽略的ADC技术指标

模拟技术

描述

模数转换器(ADC)的种类繁多,我们总是很难弄清哪种ADC才最适合既定应用。数据手册往往会使问题变得更加复杂,许多技术指标都以无法预料的方式影响着性能。

选择转换器时,工程师通常只关注分辨率、信噪比(SNR)或者谐波。这些虽然很重要,但其他技术指标同样举足轻重。

分辨率,可能是最易被误解的技术指标,它表示输出位数,但不提供性能数据。部分数据手册会列出有效位数(ENOB),它使用实际SNR测量来计算转换器的有效性。一种更加有用的转换器性能指标是噪声频谱密度(NSD),单位为dBm/Hz或HznV。NSD可以通过已知的采样速率、输入范围、SNR和输入阻抗计算得出(dBm/Hz)。已知这些参数,便可选择一款转换器来匹配前端电路的模拟性能,这种选择ADC的方法比仅仅列出分辨率更有效。

许多用户还会考虑杂散和谐波性能,这些都与分辨率无关,但转换器设计人员一般要调整他们的设计,使谐波与分辨率相一致。

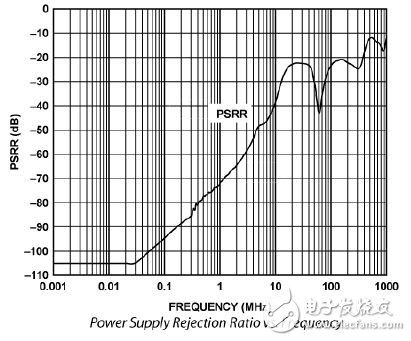

电源抑制(PSR)测量电源纹波如何与ADC输入耦合,显现在其数字输出上。如果PSR有限,相对于输入电平,电源线上的噪声将仅会受到30至50 dB的抑制。

一般而言,电源上的无用信号与转换器的输入范围相关。例如,如果电源上的噪声是20 mV rms ,而转换器输入范围是0.7 Vrms,则输入上的噪声是-31 dBFS。如果转换器的PSR为 30 dB,则相干噪声会在输出中显现为一条-61 dBFS谱线。在确定电源将需要多少滤波和去耦时,PSR尤其有用,PSR在医疗应用或工业应用等高噪声环境中非常重要。

图1

共模抑制(CMR)测量共模信号存在时所引起的差模信号。许多ADC采用差分输入来实现对共模信号的高抗扰度,因为差分输入结构本身能抑制偶数阶失真产物。

与PSR一样,电源纹波、接地层上产生的高功率信号、混频器和RF滤波器的RF泄漏以及能够产生高电场和磁场的应用会引入共模信号,虽然许多转换器未规定CMR,但他们通常具有50至80 dB的CMR。

时钟相关技术指标,尽管比较重要,但并不总是作出规定,而且可能难以确定。

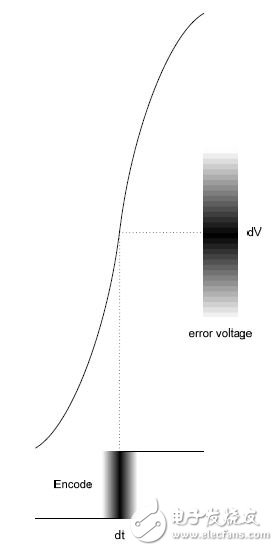

图2. 输入时钟与采样噪声的关系

时钟压摆率是实现额定性能所需的最小压摆率。多数转换器在时钟缓冲器上有足够的增益,以确保采样时刻界定明确,但如果压摆率过低使得采样时刻很不确定,将产生过量噪声。如果规定最小输入压摆率,用户应满足该要求,以确保额定噪声性能。

孔径抖动是ADC的内部时钟不确定性。ADC的噪声性能受内部和外部时钟抖动限制。

在典型的数据手册中,孔径抖动仅限转换器。外部孔径抖动以均方根方式与内部孔径抖动相加。对于低频应用,抖动可能并不重要,但随着模拟频率的增加,由抖动引起的噪声问题变得越来越明显。如果不使用充足的时钟,性能将比预期要差。

除由于时钟抖动而增加的噪声以外,时钟信号中与时钟不存在谐波关系的谱线也将显现为数字化输出的失真。因此,时钟信号应具有尽可能高的频谱纯度。

孔径延迟是采样信号的应用与实际进行输入信号采样的时刻之间的时间延迟。此时间通常为纳秒或更小,可能为正、为负或甚至为零。除非知道精确的采样时刻非常重要,否则孔径延迟并不重要。

转换时间和转换延迟是两个密切相关的技术指标。转换时间一般适用于逐次逼近型转换器(SAR),这类转换器使用高时钟速率处理输入信号,输入信号出现在输出上的时间明显晚于转换命令,但早于下一个转换命令。转换命令与转换完成之间的时间称为转换时间。

转换延迟通常适用于流水线式转换器。作为测量用于产生数字输出的流水线(内部数字级)数目的技术指标,转换延迟通常用流水线延迟来规定。通过将此数目乘以应用中使用的采样周期,可计算实际转换时间。

唤醒时间,为了降低功耗敏感型应用的功耗,器件通常在相对不用期间关断,这样做确实可以节省大量功耗,但器件重新启动时,内部基准电压源的稳定以及内部时钟的功能恢复都需要一定的时间,此时转换的数据将不满足技术指标。

输出负载,同所有数字输出器件一样,ADC,尤其是CMOS输出器件,规定输出驱动能力。出于可靠性的原因,知道输出驱动能力比较重要,但最佳性能一般是在未达到完全驱动能力时。

在高性能应用中,重要的是,将输出负载降至最低,并提供适当的去耦和优化布局,以尽可能降低电源上的压降。为了避免此类问题发生,许多转换器都提供LVDS输出。LVDS具有对称性,因此可以降低开关电流并提高总体性能。如果可以,应该使用LVDS输出以确保最佳性能。

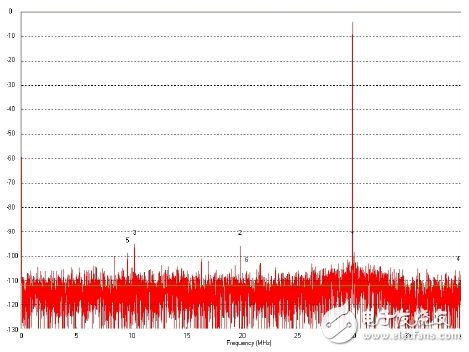

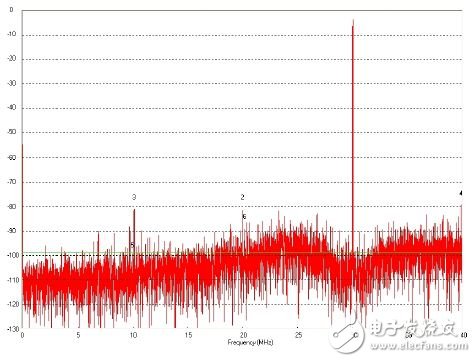

未规定标准,一个至关重要的未规定项目是PCB布局。虽然可规定内容的不多,但它会显着影响转换器的性能。例如,如果应用未能采用充足的去耦电容,就会存在过多的电源噪声。由于PSR有限,电源上的噪声会耦合到模拟输入中,并破坏数字输出频谱,如图3所示。

图 3a

图 3b

-

ADC采样保持电路的工作原理和技术指标2024-10-05 6560

-

经常被忽略的ADC技术指标你知道有哪些吗?2021-04-14 2004

-

选择转换器时需要关注哪些技术指标?2021-04-09 1230

-

9个常被忽略的ADC技术指标2021-04-02 2157

-

常被忽略的九项ADC技术指标,你常忽略哪些?2018-10-29 1900

-

9个常被忽略的ADC技术指标,一起来看看!2018-03-26 11298

-

九项常被忽略的ADC技术规格2017-04-04 2749

-

9项常被忽略的ADC指标技术指标2011-01-02 788

-

常被忽略的九项ADC技术指标2010-10-11 1060

全部0条评论

快来发表一下你的评论吧 !