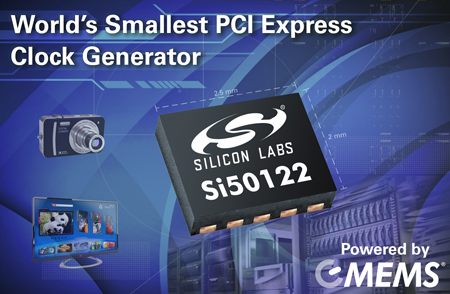

Silicon Labs推出业界最小尺寸PCI Express时钟IC

EDA/IC设计

描述

中国,北京-2014年10月9日-高性能模拟与混合信号IC领导厂商Silicon Labs(芯科实验室有限公司, NASDAQ:SLAB)今天宣布针对消费电子和嵌入式应用推出业界最小尺寸的符合PCI Express(PCIe)标准的时钟发生器芯片,在这些应用中可靠性、板面积、器件数量和功耗通常是其关键设计要素。设计旨在满足PCIe Gen 1/2/3标准的严格规范,新型的Si50122时钟凭借Silicon Labs低功耗PCIe和CMEMS®技术为各类应用提供了节能、免片外晶体的时钟解决方案,这些应用包括数字录像机和静态照相机、IP机顶盒、高清视频 流播放机、高清晰度数字电视、家庭娱乐和音频系统、多功能打印机、消费类和小型商业存储设备、家庭网关和无线接入设备等。

Si50122是第一个集成Silicon Labs CMEMS专利技术的时钟发生器芯片。片内的CMEMS谐振器为芯片内的CMOS时钟电路提供了一个稳定的频率参考,省去了通常所需的大体积、分立的石英 晶体。通过利用CMEMS技术,Si50122 PCIe时钟提供了极佳的抗冲击和抗振动性,即使在恶劣的条件下(例如极端温度变化)也能够确保高可靠性并保证性能。手持消费电子产品容易遭遇碰撞或跌落 的情况,使用稳固的CMEMS PCIe时钟发生器而不是基于晶体的解决方案,能够消除由于石英谐振器损坏而导致系统故障的风险。

支持 极小的2mm x 2.5mm 10引脚TDFN封装,Si50122是业内现有的最小尺寸的PCIe时钟发生器,也是业内最低功耗的免片外晶体的PCIe时钟解决方案。结合了业内领先 的小尺寸和超低功耗,Si50122成为采用PCIe互联标准的空间受限的手持和电池供电型消费电子和嵌入式应用的最佳解决方案。

为了 降低系统成本、功耗和器件数量并简化电路板设计,Si50122 PCIe时钟发生器采用了低功耗的“推挽(Push-pull)”式HCSL输出缓冲器,省去了HCSL输出通常所需的所有外部终端电阻。而竞争对手芯片 通常使用传统的输出缓冲器架构,其需要1个电源电阻器以及每个输出端口上多达4个终端电阻器,这迫使设计人员在使用2路输出器件时要管理多达9个片外电阻 器。通过省去众多的片外器件,推挽技术使得设计人员能够在输出引脚和接收器之间使用直连线,从而获得更可靠的信号完整性。其他大多数PCIe时钟供应商通 常采用传统的恒流(constant-current)技术,相较之下,在输出缓冲器中采用推挽技术功耗可降低60%以上。

Si50122 PCIe时钟芯片提供2路低功耗100MHz差分HCSL输出和1路25MHz LVCMOS时钟输出。由于它是免片外晶体的解决方案,因此它不需要片外25MHz参考时钟源。正如Silicon Labs全部的PCIe计时IC产品组合一样,Si50122芯片完全超越了PCIe Gen 1/2/3标准中对于抖动性能的要求,并且支持可选的扩频调制功能以进一步降低电磁干扰(EMI)。

Silicon Labs计时产品营销总监James Wilson表示,“随着当今功耗和空间受限的消费电子和嵌入式产品不断采用PCIe标准,开发人员需要新一代PCIe时钟解决方案以最小化功耗、BOM 数量和电路板面积。我们设计新型的基于CMEMS的免片外晶体Si50122 PCIe时钟,旨在为快速扩展的PCIe市场提供高集成度、低功耗、高可靠性和设计的简易化”。

价格和供货

Si50122 PCIe时钟发生器现在已经量产,可提供样片。在一万片采购量时单价为0.77美元。为了加速PCIe应用开发,Silicon Labs还提供了Si50122-Ax-EVB评估板,零售价格为125美元。

关于Silicon Labs

Silicon Labs公司(NASDAQ股票代码:SLAB)是在物联网、互联网基础设施、工业控制、消费电子和汽车等市场领域中领先的芯片、软件和系统解决方案提供 商。我们解决电子行业各项难题,在性能、节能、互联和简约设计方面为客户带来显著优势。Silicon Labs拥有世界一流的具有卓越软件和混合信号设计经验的工程团队,提供设计人员把最初想法快速、简便的转化为最终产品所需的工具和技术。

- 相关推荐

- 热点推荐

- PCI Express

- Silicon Labs公司

- Si50122

-

Silicon Labs推出业界最小最节能的PCI Express时钟2013-05-23 1637

-

业界最低抖动、最高集成度、最低功耗的时钟发生器2017-10-09 7623

-

Silicon Labs发布业界首款支持4G / LTE和以太网的无线时钟2017-10-12 4847

-

业内首款低功耗PCI Express Gen 4缓冲器提升功耗及性能标杆2018-03-15 3041

-

Silicon Labs全新时钟解决方案简化IEEE 1588系统集成2020-11-18 1184

-

Silicon Labs设计的Si4438收发器2018-12-22 3148

-

NI推出业界首款基于PCI Express的图像采集板卡2009-08-31 1216

-

Silicon Labs推出业界最低功耗微控制器系列2009-12-15 1632

-

Silicon Labs扩展其PCIe时钟发生器和时钟缓冲器产品组合2012-02-02 1843

-

Silicon Labs推出微型低功耗可定制时钟IC系列SI512XX2012-02-07 1360

-

Silicon Labs推出业界最低抖动的Si534x时钟系列产品2014-07-31 3537

-

Silicon Labs推出PCI Express缓冲器简化数据中心时钟设计2014-12-04 1341

-

Silicon Labs PCI Express时钟抖动计算工具简化计时设计2015-12-11 3065

-

Silicon Labs针对IoT终端节点推出全球最小尺寸的蓝牙SiP模块2016-11-09 1446

-

Silicon Labs PCI Express Gen 4时钟为数据中心 和消费类产品设计确立新的性能标杆2017-09-28 7774

全部0条评论

快来发表一下你的评论吧 !