Xilinx SDAccel 环境:为数据中心带来最佳单位功耗性能

FPGA/ASIC技术

描述

引言

数据中心运维人员总是不断在寻求更高的服务器性能。目前,他们主要是通过易于编程的多核CPU 和GPU 来开发应用,但CPU 和GPU 都遇到了单位功耗性能的瓶颈壁垒。从事海量数据中心应用开发(如密钥加速、图像识别、语音转录、加密和文本搜索等)的设计人员既希望GPU 易于编程,同时又希望硬件具有低功耗、高吞吐量和最低时延功能。然而,多核CPU和GPU 加速器在可扩展性上存在严重的问题:客户希望用简单的全高度插入式PCIe开发板作为数据中心服务器的应用加速器。这种开发板经配置可运行高功率图形卡,但客户同时希望功耗不超过25W,以便最大化可扩展性并最小化总功耗。

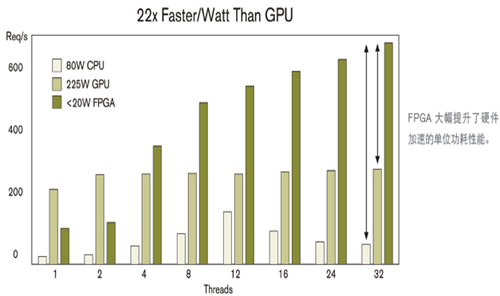

最近赛灵思同瑞士苏黎世联邦理工学院(ETH Zurich)联合开展的一系列研究发现,基于FPGA 的应用加速想比CPU/GPU实现方案,单位功耗性能可提升25 倍,而时延则缩短了50 到75 倍,与此同时还能实现出色的I/O 集成(PCIe、DDR4SDRAM 接口、高速以太网等)。换言之,FPGA 能在单芯片上提供高能效硬件应用加速所需的核心功能,并同时提供每个开发板目标功耗低于25W 的的解决方案。

中国网络服务领先企业百度公司在美国加州圣何塞举行的2014年热门芯片研讨会上介绍了支持性调查结果。百度的结论如下:

• 中端FPGA 能够实现375 GFLOPS 的性能,功耗仅为10-20W

• 基于FPGA 的加速器可部署在所有类型的服务器中。

• 和CPU 和GPU 相比, FPGA 在深度神经网络(DNN)预测系统中性能更加出色。DNN 系统用于语言识别、图像搜索、OCR、面部识别、网页搜索以及自然语言处理等各种不同应用。

FPGA 用于应用加速的最大问题在于编程。数据中心应用开发人员不希望采用以硬件为中心的RTL 流程,也就是传统FPGA的开发路径。他们所需要的是:

• 单位功耗性能更高

• 完全软件的开发环境

• 易于升级的设计

推出全新赛灵思SDAccel 环境

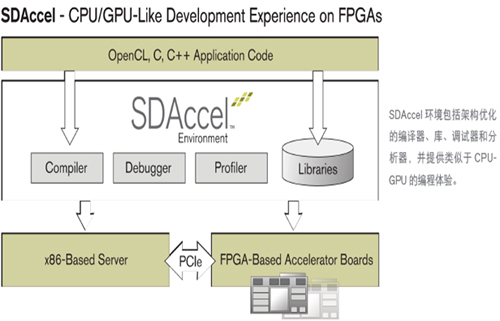

全新的赛灵思SDAccel 开发环境为数据中心应用开发人员提供了他们所需要的完整的FPGA 软硬件解决方案。SDAccel 包括可高效利用片上FPGA 资源的快速的、架构优化的编译器;熟悉的软件开发流程—— 其带有用于代码开发、特性分析与调试的Eclipse 集成设计环境(IDE),可提供类似于CPU/GPU 的工作环境;以及针对不同数据中心应用而优化的动态可重配置加速器,能在类似CPU/GPU 运行时间环境中即时更换。运行过程中应用能让不同处理模块在FPGA 中即时替换,且不会干扰服务器CPU 和FPGA 之间的连接,实现不间断的应用加速。

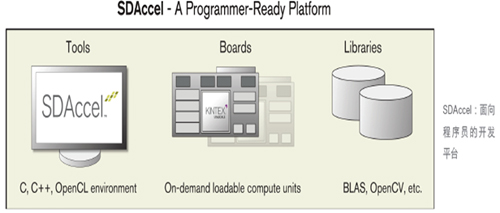

SDAccel 结合业界首款架构优化编译器、库和开发板,是唯一能在FPGA 上提供类似于CPU/GPU 的开发和运行时间体验。SDAccel 开发环境面向基于X86 服务器处理器的主机系统,并可提供现成的商用(COTS)PCIe 插卡,用于添加FPGA 功能。

行业首款面向C、C++ 和OpenCL 的架构优化编译器

SDAccel 的架构优化编译器使软件开发者能够优化并编译流媒体、低时延以及定制数据路径应用。SDAccel 编译器主要针对高性能赛灵思FPGA 并支持OpenCL,C 和C++ 任意组合的源代码。SDAccel 编译器相比高端CPU 性能提高达10 倍,而功耗仅为GPU 的1/10,同时能保持代码的兼容性和一个传统的软件编程模式,以便于应用移植并节约成本。根据客户基准,SDAccel 编译器相比同类竞争FPGA 解决方案,性能和资源效率均提升了3 倍。SDAccel 编译器自动生成的设计甚至比手动编码的RTL 设计方案的性能还高,在某些情况下可高出20% 之多。

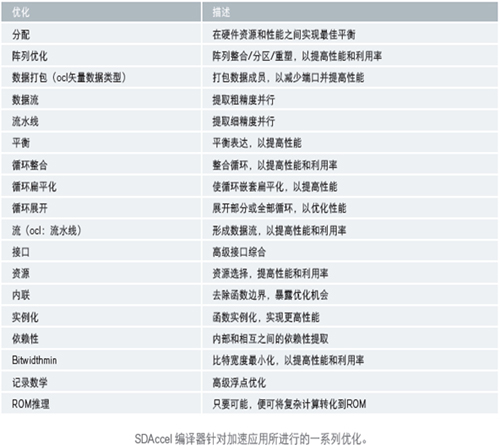

架构优化的SDAccel 编译器可以自动对应用源代码实施一系列基础甚至高级的优化方案。下表列出了SDAccel 编译器针对加速应用所进行的一系列优化。

其中一些自动优化能大幅提升整体应用的效率。举例来说,SDAccel 编译器的数据流流水线功能可对多个功能进行流水线化,而不会局限于仅能对单一功能进行优化。该编译器的存储器优化功能能极大地提升功效,从而让你能够在FPGA 中添加更多功能。SDAccel 是首款面向FPGA 平台的完全软件的开发环境,可实现类似于CPU/GPU 的开发体验。开发人员能用熟悉的工作流程优化应用,而且即便很少或者没有FPGA 使用经验,也能获益于FPGA 的平台优势。集成设计环境(IDE)不仅可提供编码模板和软件库,而且还支持在x86 平台上进行编译、调试、特性分析和FPGA 仿真。准备好部署后,IDE 能在配有自动仪器插入功能的数据中心用现成的商用 FPGA 平台上实现算法。

SDAccel 还经过精心构建,使CPU/GPU 开发人员能够轻松将其应用移植到FPGA 上,同时还可在熟悉的工作流程中维护和复用OpenCL、C 和C++ 代码。大量代码和库采用C 和C++ 格式。对于希望采用其现有代码库中的不同代码,或者采用第三方代码库,甚至继续组合使用C、C++ 或OpenCL 进行开发的开发者来说,能用C、C++ 或OpenCL 工作是最大的便利。

SDAccel 环境配套提供面向程序员的Eclipse IDE 以及一系列基于C 语言的FPGA 优化库和数据中心用现成商用平台。Convey Computer、Alpha Data Parallel Systems 和Pico Computing 公司可提供数据中心用加速板卡。2015 年年初还将增加更多商用现货(COTS)合作伙伴。SDAccel 库包括内置OpenCL 函数、DSP、视频和线性代数库,能支持高性能低功耗实现方案。针对特定领域加速,赛灵思联盟合作成员Auviz Systems 公司还提供优化的 OpenCV 和BLAS SDAccel 兼容库。

应用开发人员完全能在X86 仿真空间开始使用SDAccel 使其代码开始工作。一旦其确信其算法开发人员就能对代码进行特性分析,找到受益于加速的代码片段。然后开发人员就可以利用这些有针对性的片段,无缝采用快速自动生成的周期精确内核仿真,从而实现加速。这些快速仿真可用来调试和优化加速量,同时能在架构层面工作。业经验证的应用能方便地移植到主机/FPGA 系统。SDAccel 开发环境可支持所有这些来自同一控制中心(cockpit)的活动。

SDAccel 库对SDAccel 类似CPU/GPU 的开发体验发挥了重要作用。这些库包含底层数学库以及BLAS、OpenCV 和DSP 等高生产力库。这些库用C++(而不是用RTL)编写,因此在所有开发和调试阶段都能完全像编写一样使用。在项目早期阶段,所有开发工作都在CPU 主机上进行。由于SDAccel 库用C++ 语言编写,因此能与CPU 目标的应用代码一起编译,创建虚拟设计原型,让所有测试、调试和初始特性分析工作在主机上进行。在此阶段无需FPGA。

一旦应用经过初始调试和特性分析,需要硬件加速的关键功能可通过编译实现协同仿真,加速功能运行在基于CPU 的RTL仿真器上。这时,软件开发团队可观察所得的性能,确定应用能否满足性能目标要求。RTL 仿真能准确给出FPGA 硬件加速的性能情况,这就能让开发团队得到很好的性能估算,而且能高度确保所得的FPGA 配置能精确重现应用源代码的行为和结果。

加速功能随后可迁移到FPGA 上,生成最后的加速应用,可用于部署。SDAccel 编译器不是创建通用FPGA 配置,而是在编译时针对特定的赛灵思FPGA,包括器件速度等级,这样所得的加速功能就能针对FPGA 上的可用资源以及器件时序进行优化。在这时我们甚至还能测试功能,这对性能不会造成影响,硬件开销极低,而且还能在同样熟悉的SDAccel 开发环境中进行更多后期特性分析,以便充分利用FPGA 硬件,全面最大化应用加速效果。

CPU 级特性分析能发现应用瓶颈。协同仿真将告诉您这些瓶颈是否已经被加速特定功能消除掉。在FPGA 上对硬件加速功能进行特性分析能实现更多优化,进一步优化应用代码和加速功能。在任何时间以及各个阶段中,SDAccel 编译器都可选择性地检测应用代码,包括加速功能,这就意味着调试和特性分析能够以相同方式进行,而且无论开发工作进入到哪个阶段,都可用使用同一软件开发工具。

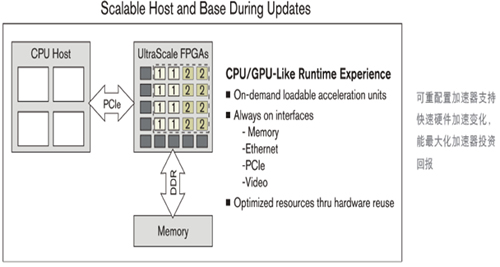

在FPGA 上首次带来类似CPU/GPU 的运行时间和升级体验

SDAccel 可提供支持实时类似CPU/GPU 运行时间升级的唯一FPGA 动态可重配置加速器。SDAccel 对于FPGA 解决方案的独特之处在于其利用唯一的FPGA 动态重配置功能可在内核升级时保持系统继续运行,这不仅可加载新的硬件加速器内核(这一点与CPU/GPU 加速器的功能类似),同时还能保持关键的系统接口和功能(如存储器、以太网、PCIe 和性能监控器)继续发挥作用。这种即时的系统重配置功能理想适用于数据中心计算需求及负载的立即更新。这种应用的一个实例就是图像搜索、视频转码和图像处理等功能的即时切换,从而带来战略性优势。

所有这些都能通过硬件重用转换为资源优化,这在数据中心环境中是一大优势。简而言之,基于SDAccel 的系统现在能加速应用,而如果未来需要另外一种类型的加速,系统能快速顺利地实现升级。

开发者可以管理和运行基于SDAccel 的系统就像在CPU/GPU 系统一样。利用SDAccel 和硬件快速动态重配置功能,我们甚至能在应用运行中重用FPGA。这种功能使得我们能用相同的FPGA 板卡执行不同的内核加速,硬件可针对不同的算法进行重新优化,且不会限制或中断应用流程。通过支持动态重配置,SDAccel 能让数据中心运维人员最大限度地发挥硬件加速投资价值。

实实在在的标准测试可证明SDAccel 的性能和价值

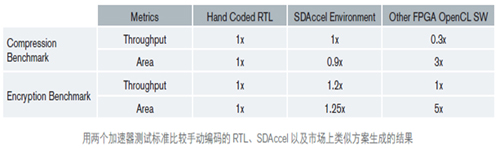

SDAccel 经过了具有实际标准测试的业界验证。举例来说,在压缩标准测试中,SDAccel 生成的硬件加速器比同类竞争工具生成的加速器速度高3 倍多,尺寸小3 倍。占位面积及吞吐量与手动优化的RTL 实现方案旗鼓相当甚至更优秀。

在上述的加密标准测试中,SDAccel 生成的硬件加速器比同类竞争工具生成的加速器速度快1.2 倍,而面积小4 倍。更棒的是,SDAccel 自动生成的加速器比用RTL 手动编码生成的加速器还快20%。SDAccel 开箱即用,可直接编加速器,而且QOR(结果质量)与手动编码结果质量旗鼓相当,甚至更胜一筹。

结论

SDAccel 可满足数据中心应用开发人员的需求,包括提供类似CPU/GPU 的工作环境,其生成的高效硬件加速器可实现最佳单位功耗性能,远胜于运行在CPU/GPU 上的加速器。SDAccel 通过带有系统内即时可重配置功能的单个控制中心环境(cockpit environment)支持软件工作流程,最大化数据中心硬件加速投资回报。因此,SDAccel 是一种独特而完整的FPGA解决方案,其易用性和功能远超同类竞争性工具。这些同类竞争性工具不能提供高生产力工作流程,也不能提供熟悉的环境,加速器性能更不能与SDAccel 自动生成的硬件加速器相提并论。

-

数据中心是什么2021-07-12 2118

-

高效率的快速部署 玩转模块化数据中心 相关资料推荐2021-07-05 2863

-

未来数据中心与光模块发展假设2020-08-07 2995

-

如何在降低TCO的同时提高数据中心性能?2019-10-10 3008

-

赛灵思宣布推出新的开发环境,将数据中心的单位功耗性能提高达25倍2019-08-01 3505

-

Xinlinx SDAccel开发环境是什么?2018-11-27 3887

-

Xilinx Alveo U200数据中心加速器卡的主要性能和优势2018-10-14 6797

-

针对OpenCL、C和 C++的SDAccel开发环境可利用FPGA实现数据中心应用加速2018-08-30 1568

-

走向绿色数据中心的7种手段2018-08-16 2444

-

Xilinx SDAccel 开发环境荣获 2015 EE Times 和 EDN ACE 大奖2017-02-09 488

-

Xilinx SDAccel 开发实验室亮相 SC15!2017-02-08 254

-

数据中心布线五大注意要点2016-07-21 13768

-

Xilinx发布新版SDAccel开发环境加速数据中心应用2015-05-28 2859

-

当CPU/GPU遭遇数据中心功耗天花板,SDAccel来了2014-12-03 3767

全部0条评论

快来发表一下你的评论吧 !