基于安路科技FPSoC器件DR1系列的视频采集/显示/处理解决方案

音视频及家电

描述

安路科技全新一代FPSoC器件DR1系列,集成高性能硬核处理器双核ARM Cortex-A35或单核64位RISC-V、丰富的片上内存和高低速外设接口、FPGA可编程逻辑、NPU/JPU硬件加速单元,内部通过高带宽总线互联,拥有高性能通用处理能力的同时,兼具安路FPGA的灵活性和扩展能力,定位复杂嵌入式系统、低功耗和高性能应用市场。

针对视频采集处理类应用,通常需要利用FPGA来应对多种多样的外部接口实现视频数据采集和传输,利用CPU来运行上层应用和算法,使用DR1器件可在单颗芯片内部实现这些功能。

相比多颗分立芯片的方案,带来的收益包括降低总体成本、降低电路板面积、提供更高的内部数据带宽来解决性能瓶颈、通过统一的开发工具以及省去芯片间通信等方式可大幅降低开发难度。

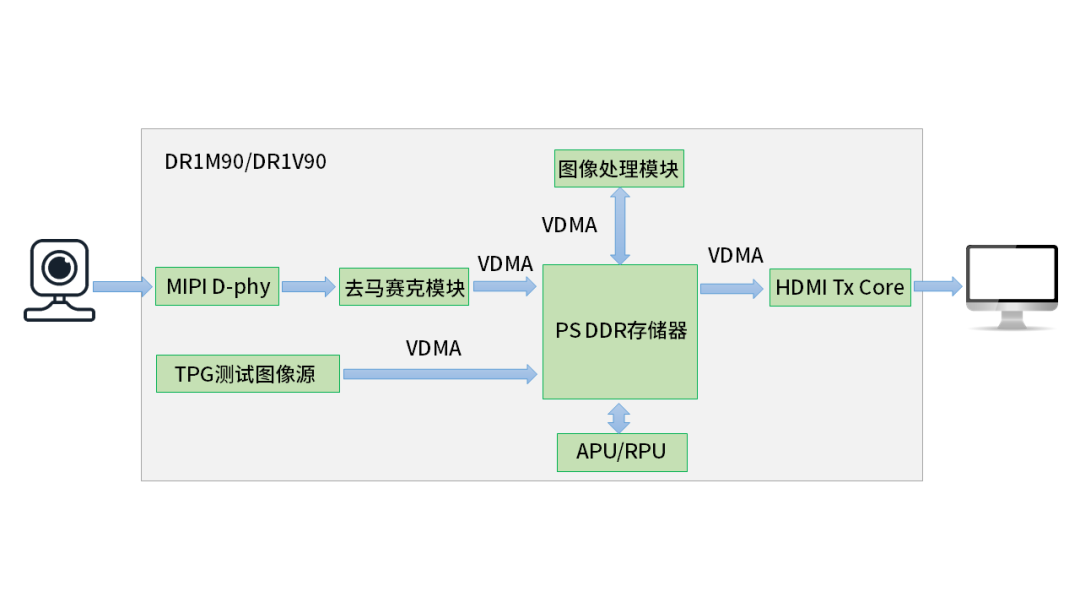

安路科技支持基于DR1M器件的视频采集/显示/处理解决方案,在一颗FPSoC芯片内实现MIPI摄像头视频采集、测试视频源生成、流模式视频处理、HDMI接口图像显示的全过程,并可在操作系统上运行例如基于QT的控制界面、用户算法等上层应用。

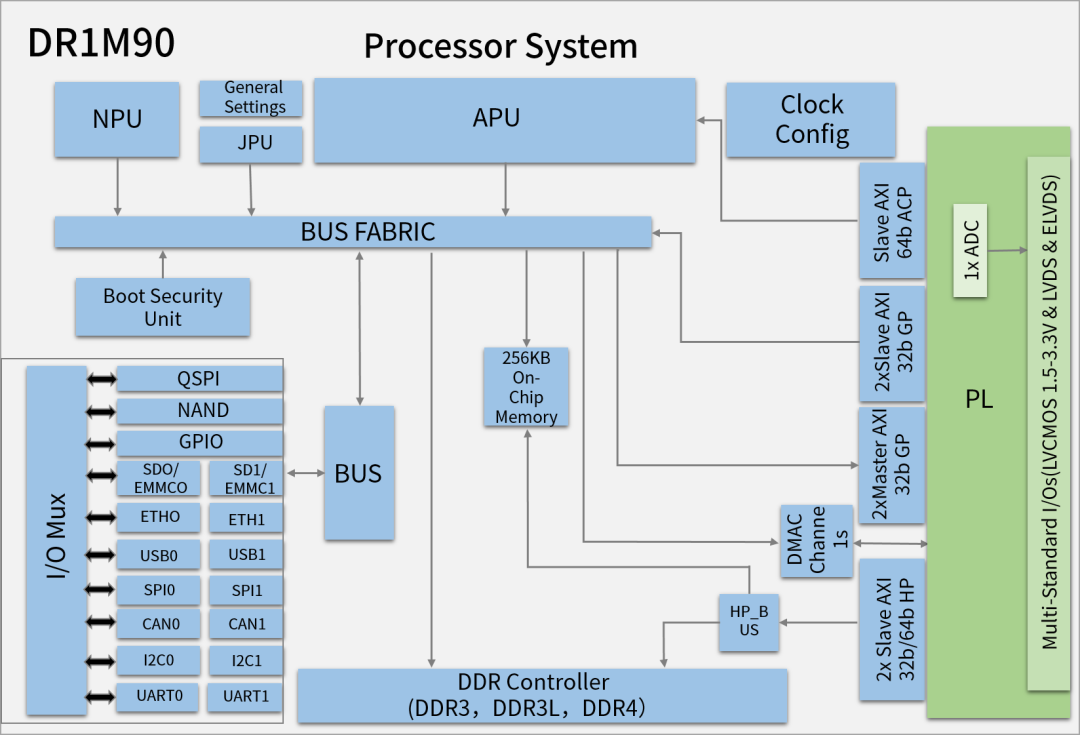

DR1M芯片架构图

其中ARM处理器运行通用任务,FPGA发挥其灵活性进行扩展接口或针对视频处理等特定任务进行并行加速。处理器和FPGA之间的高数据带宽使得二者各司其长,充分发挥异构处理优点,在性价比、开发难度、灵活性、电路板面积、功耗等方面为客户提供更优选择,可广泛应用于机器视觉、智能摄像头等图像视频处理领域。

方案介绍

整个环境包括:DR1M90 FPSoC开发板、开发板12V电源、MIPI摄像头、支持1080p的HDMI显示器及HDMI连接线。

FPSoC的MIPI接收采用的是芯片内部的硬核MIPI D-phy;视频数据搬运采用的是安路科技开发的VDMA软核IP,该IP专用于视频相关应用,主要特性有帧同步和多帧缓存等。

方案示意图

视频数据被VDMA搬运到PS DDR中,可选的由VDMA搬运到视频处理模块,处理完成后送回PS DDR,最后被VMDA发送到HDMI进行显示,在此过程中APU/RPU处理器也可对DDR中视频数据进行修改,如画框、图像叠加等。视频数据的来源有两路:摄像头和TPG。摄像头采集到的外部视频经过D-phy和去马赛克后进入DDR;TPG则是PL逻辑产生的测试视频,直接进入DDR。

-

基于安路DR1M90 FPSoC的Linux系统全流程开发指南(4)2025-11-30 2391

-

DR1 系列核心板 PS+PL 异构多核实战案例手册(二)2026-01-14 4872

-

安路科技发布SALDRAGON®飞龙系列全新FPSoC®器件,多元化产品矩阵加速布局下游市场2023-11-13 1651

-

米尔国产FPGA SoC芯选择,安路飞龙DR1M90核心板重磅发布2025-01-10 2803

-

搭载ARM,NPU,FPGA三种核心的开发板—米尔安路DR1M90飞龙派2025-06-13 1506

-

【米尔MYC-YM90X安路飞龙DR1开发板】HMI人机界面开发2025-08-14 6332

-

Altera的视频和图像处理解决方案2010-06-08 945

-

安路科技FPSoC器件助力实现视频图像接口转换和工业控制交互2022-07-25 2127

-

【世说芯品】FPSoC®产品SF1系列全新发布,高集成低功耗,助力实现多种应用场景2022-07-20 1520

-

可编程逻辑技术厂商安路科技发布SALDRAGON®飞龙系列全新FPSoC®器件2023-11-12 2621

-

安路科技发布全新FPSoC®器件,芯来RISC-V内核助力高性能融合2023-11-17 3047

-

安路科技DR1FPSoC多路以太网扩展方案2025-04-03 1470

-

安路科技DR1系列FPSOC荣获2025工博会集成电路创新成果奖2025-10-09 1280

-

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(1)2025-11-25 537

-

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(3)2025-11-26 484

全部0条评论

快来发表一下你的评论吧 !