RA6T2的16位模数转换器操作 [11] 配置RA6T2 ADC模块 (8)

描述

2 配置RA6T2 ADC模块

2.2 以16位深度操作ADC

2.2.6 数字滤波器功能

数字滤波器功能是获得高精度和高分辨率16位深度A/D转换结果不可或缺的一部分。因此,在过采样模式和混合模式下需要使用该功能。禁止在SAR模式下使用数字滤波器。

本节将介绍数字滤波器功能的特性和配置,并解释滤波器的操作方法。

2.2.6.1 配置和特性

每个ADC单元配备4个数字滤波器。数字滤波器是具有22个抽头的FIR型滤波器。在操作ADC之前,必须先配置数字滤波器。有两款预设滤波器可供选择:sinc滤波器(在FSP配置中称为sync3滤波器)或最小相位滤波器。

sinc3滤波器的频率响应如下图所示:

图9. Sinc3滤波器的归一化频率响应

最小相位滤波器的频率响应如下图所示:

图10. 最小相位滤波器的归一化频率响应

有关sinc3滤波器和最小相位滤波器特性的更多信息,请参见《RA6T2硬件用户手册》的“电气特性”一章。

数字滤波器通过ADDOPCRAn.DFSEL[2:0](n = 0至36)和ADDFSRm(m = 0、1)寄存器进行设置。下面的框图显示了数字滤波器配置:

图11. 数字滤波器框图

2.2.6.2 操作数字滤波器

如果使能数字滤波器功能,则A/D转换数据会按顺序输入数字滤波器。如果数字滤波器的所有抽头都填满数据,则会输出计算结果,并将其发送到下一个数据处理步骤。

过采样模式和混合模式的数字滤波器功能操作略有不同。

(1) 数字滤波器操作 – 过采样模式

在过采样模式下,A/D转换器连续对一个模拟通道进行过采样。每次执行过采样时,A/D转换数据会按顺序输入数字滤波器。滤波器的所有抽头都填满转换数据后,即会从滤波器输出计算结果,并将其发送到下一个数据处理步骤。

将A/D转换数据输出到下一个数据处理步骤后,会丢弃数字滤波器中的抽头数据。但是,如果使用A/D转换值相加/平均值计算功能,则在收集到计算A/D转换值的相加值或平均值所需的数据之前,将一直保留数字滤波器中的抽头数据。计算出A/D转换值相加值/平均值后,将丢弃数字滤波器中的抽头数据。

(2) 数字滤波器操作 – 混合模式

混合模式可以同时使用多个数字滤波器电路并行处理最多四个模拟通道的过采样数据(A/D转换数据)。每次执行过采样时,A/D转换数据会按顺序输入数字滤波器。滤波器的所有抽头都填满转换数据后,即会从滤波器输出计算结果,并将其发送到下一个数据处理步骤。

在混合模式 – 单次扫描模式组合下,将在扫描操作结束时丢弃数字滤波器中的抽头。

在混合模式 – 连续扫描模式组合下,只要继续执行连续扫描操作,数字滤波器中的抽头数据就会不断更新。因此,在数字滤波器中的所有抽头都填满数据后,每次执行过采样时都会输出一个新的计算结果。如果扫描操作由于A/D转换的强制停止而中止,将丢弃滤波器中的抽头数据。

混合模式 – 后台连续扫描模式组合与混合模式 – 连续扫描模式组合的数字滤波器操作相同。在后台连续扫描操作期间,数字滤波器和其他数据处理仍在后台进行。如果扫描操作由于A/D转换的强制停止而中止,将丢弃滤波器中的抽头数据。

2.3 ADC时序注意事项

本节将重点介绍有关操作ADC单元的几个时序注意事项。

2.3.1 采样率计算

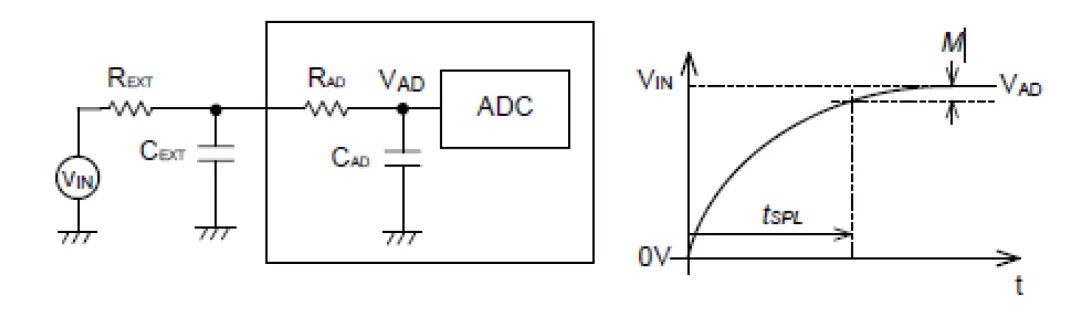

对外部输入的模拟信号进行A/D转换时,所需的采样时间取决于A/D转换器中的采样电容的充电时间。电路的简化模型如图12所示。采样时间可以通过以下等式粗略估算:

tSPL = (REXT + RAD) × (CEXT + kCAD) × ln [kCAD / (CEXT + kCAD) × (2N / M)]

图12. 简化电路模型和电容充电的采样时间曲线

在给定的等式中,时间是根据模拟输入电压 (VIN) 与采样电容电压 (VAD) 之差达到小于或等于采样误差(基于N位A/D转换器)所用的时间来估算的。

该等式只是经过简化的一般用例。它只能用于粗略估算采样时间,不能保证获得准确的采样时间。特别是对于正常精度通道,如果 (2N/M > 16384),采样时间估算的准确性会下降。

2.3.1.1 16位转换方法注意事项

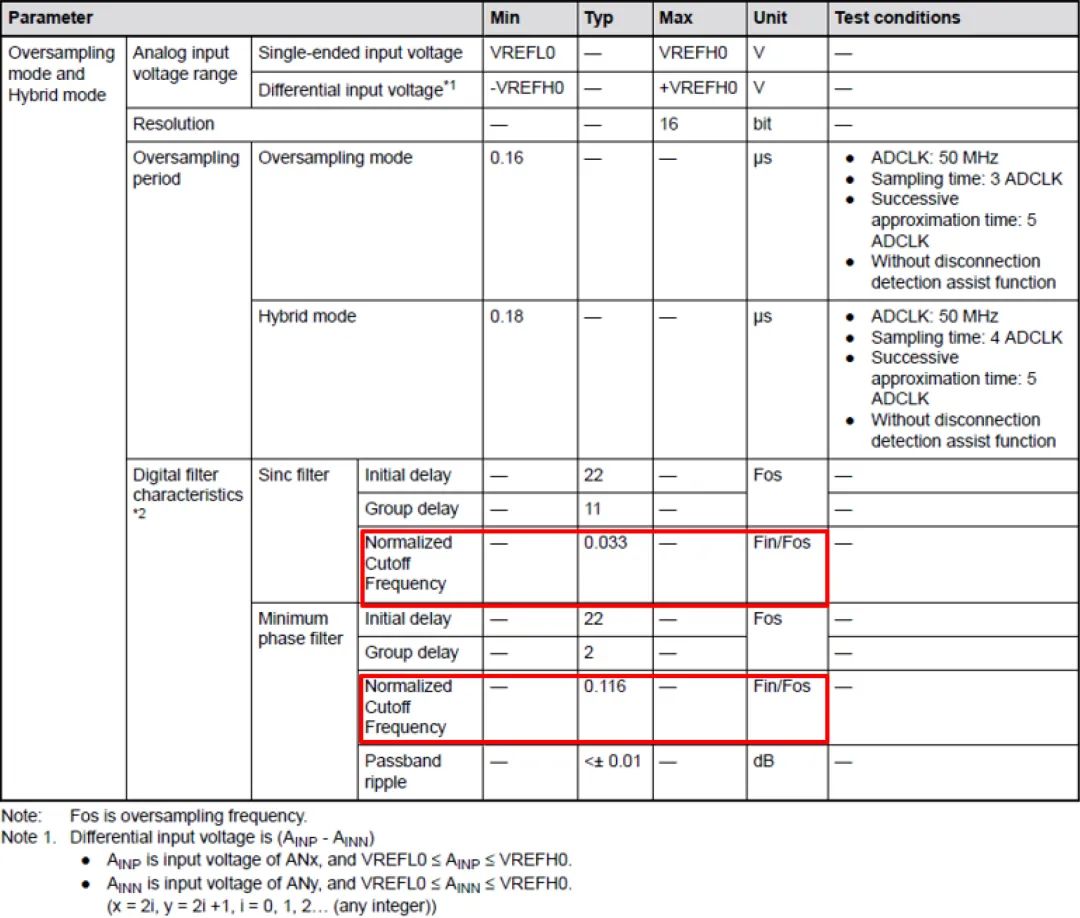

对于16位转换方法,其模拟输入信号频率的最大范围计算取决于最大采样频率以及所选数字滤波器的归一化截止频率。

采样时间的倒数即是采样频率。采样频率乘以所选相应数字滤波器的归一化截止频率即可得出输入频率的上限。归一化截止频率在下表中突出显示:

表9. 数字滤波器的归一化截止频率

计算示例:

如果转换时间为1460ns,则需要至少1个20ns的额外周期以对采样保持电路进行重新采样。因此,总周期为1480ns = 675.7KHz

Sinc滤波器:675.7KHz × 0.033 = 23.0KHz 最大输入频率

最小相位滤波器:675.7KHz × 0.116 = 78.4KHz 最大输入频率

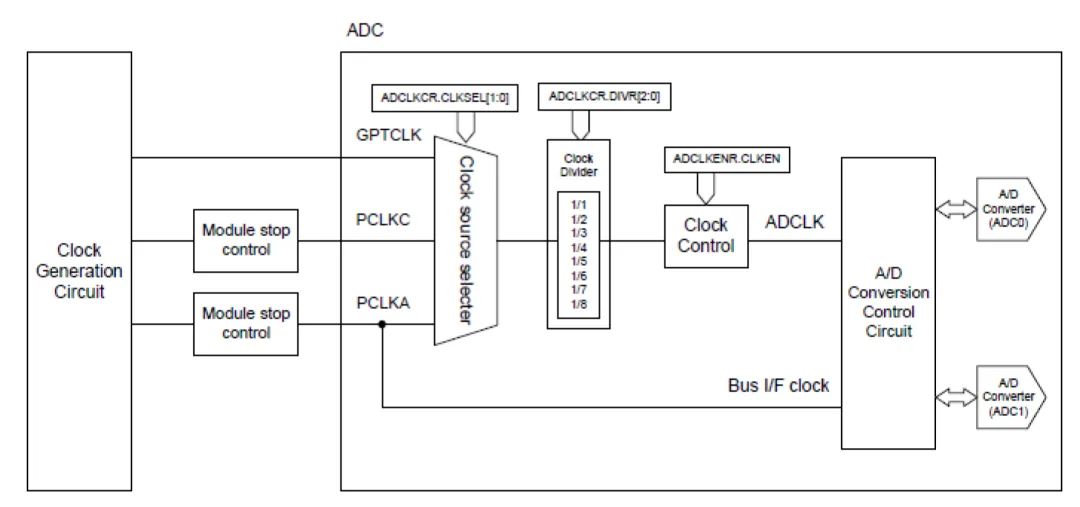

2.3.2 时钟速率

A/D转换时钟 (ADCLK) 是ADC的工作时钟。A/D转换器(ADC0和ADC1)基于ADCLK(作为基本时钟)运行和控制。下图为ADC的时钟结构:

图13. ADC外设的简化时钟结构

ADCLK由时钟源按照ADCLKCR寄存器中所选的分频比进行分频而产生。设置ADCLK的频率时应确保PCLKA ≥ ADCLK。此外,还应在《硬件用户手册》的“电气特性”一章规定的工作范围(最小25MHz到最大60MHz)内设置ADCLK的频率,以确保正常工作。

-

RA6T2的16位模数转换器操作 [14] 验证应用项目2024-06-26 1380

-

RA6T2的16位模数转换器操作 [13] 运行应用项目2024-06-19 1397

-

RA6T2的16位模数转换器操作 [12] 应用项目简介2024-06-10 1192

-

RA6T2的16位模数转换器操作 [10] 配置RA6T2 ADC模块 (7)2024-05-15 1377

-

RA6T2的16位模数转换器操作 [8] 配置RA6T2 ADC模块 (5)2024-04-29 2011

-

RA6T2的16位模数转换器操作 [7] 配置RA6T2 ADC模块 (4)2024-04-20 1537

-

RA6T2的16位模数转换器操作 [6] 配置RA6T2 ADC模块 (3)2024-04-12 1307

-

RA6T2的16位模数转换器操作 [5] 配置RA6T2 ADC模块 (2)2024-04-04 1482

-

RA6T2的16位模数转换器操作 [4] 配置RA6T2 ADC模块 (1)2024-03-29 1436

-

RA6T2的16位模数转换器操作 [2] A/D转换器概述 (2)2024-03-21 1735

-

RA6T2的16位模数转换器操作 [1] 简介,A/D转换器概述2024-03-13 2237

-

RA6T2的16位模数转换器操作 [11] 配置RA6T2 ADC模块 (8)2023-08-11 2224

-

RA6T2的16位模数转换器操作 [9] 配置RA6T2 ADC模块 (6)2023-08-04 1678

-

瑞萨MCU RA6T2的16位模数转换器操作 [4] 配置RA6T2 ADC模块 (1)2023-07-24 41860

全部0条评论

快来发表一下你的评论吧 !