安森美T10系列支持下一代大功率处理器

描述

随着数据中心为了满足人工智能计算的庞大处理需求而变得越来越耗电,提高能效变得至关重要。与一般的搜索引擎请求相比,搭载人工智能的引擎需要消耗超过 10 倍的电力,预计在未来不到两年的时间,全球数据中心的电力需求将达到约 1,000 太瓦时(TWh) 。从电网到处理器,电力需要经过四次转换来为人工智能请求的处理提供电能,这可能导致约 12% 的电力损耗。

安森美最新一代T10 PowerTrench系列和EliteSiC 650V MOSFET的强大组合为数据中心应用提供了一种完整解决方案,该方案在更小的封装尺寸下提供了无与伦比的能效和卓越的热性能。通过使用T10 PowerTrench系列和EliteSiC 650V解决方案,数据中心能够减少约1%的电力损耗。如果在全球的数据中心实施这一解决方案,每年可以减少约10太瓦时的能源消耗,相当于每年为近百万户家庭提供全年的用电量。

EliteSiC 650V MOSFET提供了卓越的开关性能和更低的器件电容,可在数据中心和储能系统中实现更高的效率。与上一代产品相比,新一代碳化硅(SiC) MOSFET的栅极电荷减半,并且将储存在输出电容(Eoss)和输出电荷(Qoss)中的能量均减少了44%。与超级结 (SJ) MOSFET 相比,它们在关断时没有拖尾电流,在高温下性能优越,能显著降低开关损耗。这使得客户能够在提高工作频率的同时减小系统元件的尺寸,从而全面降低系统成本。

T10 PowerTrench 系列专为处理对 DC-DC 功率转换级至关重要的大电流而设计,以紧凑的封装尺寸提供了更高的功率密度和卓越的热性能。这是通过屏蔽栅极沟槽设计实现的,该设计具有超低栅极电荷和小于 1 毫欧的导通电阻 RDS(on)。此外,软恢复体二极管和较低的 Qrr 有效地减少了振铃、过冲和电气噪声,从而确保了在应力下的最佳性能、可靠性和稳健性。该组合解决方案还符合超大规模运营商所需的严格的开放式机架 V3 (ORV3) 基本规范,支持下一代大功率处理器。

T10 屏蔽栅极沟槽技术

功率级内部的MOSFET必须能承受高电流,并对整个系统的效率产生显著影响。导通损耗和开关损耗共同构成了晶体管上的功率耗散。需要考虑的主要参数包括导通电阻RDS(ON)、栅极电荷以及寄生元件等,它们能在导通损耗和开关损耗之间取得平衡。

安森美用于低压和中压 MOSFET 的新型 T10 技术是理想的选择,该技术采用屏蔽栅极沟道设计,具有超低 QG 和 RDS(ON) < 1m 的特性。T10技术通过其行业领先的软恢复体二极管(Qrr, Trr)减少了振铃、过冲和噪声,实现了性能与恢复特性之间的完美平衡。

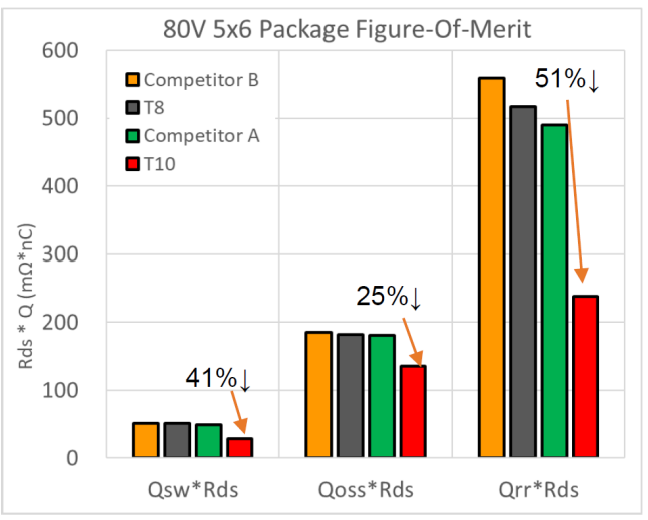

FOM改进

T10屏蔽栅极沟槽技术主要针对DC-DC转换应用,适用于各种需要 40V 和 80V MOSFET 的新型 48V 应用和传统 12V 应用。该技术旨在优化效率,降低输出电容及关键性能指标,同时实现更低的导通电阻RDS(ON)和栅极电荷QG。其中,出色的40V沟槽技术产品NVMFWS0D4N04XM,RDS(ON)可低至0.42mΩ,采用小巧的5x6封装。而对于80V的选项NVBLS0D8N08X,RDS(ON)则可低至0.79mΩ。对于低压 FET,衬底电阻可能占 RDS(ON) 的很大一部分。

因此,随着技术的进步,使用较低电阻率的衬底和减薄晶圆变得至关重要。在 T10 技术中,安森美成功减小了晶圆厚度,从而将 40V MOSFET 中衬底对 RDS(ON) 的影响从约 50% 减少到 22%。更薄的衬底也提高了器件的热性能。

审核编辑:彭菁

-

美高森美发布下一代高电压大功率系统设计指南2011-07-06 788

-

安森美半导体智能功率模块(IPM)及易于采用的工具和仿真支持2018-10-30 0

-

一文详解下一代功率器件宽禁带技术2020-10-27 0

-

安森美半导体1 A稳压器系列支持低于1 V电压轨2010-03-25 649

-

高通扩充下一代Snapdragon S4系列移动处理器2011-11-19 940

-

安森美开发下一代GaN-on-Si功率器件2012-10-10 1123

-

东芝推出支持下一代内容安全技术SeeQVault™的桥接芯片2014-04-07 1154

-

骁龙845最新消息曝光:明年上半年发布 将支持下一代Win10 ARM笔记本2017-07-25 1703

-

NVIDIA推出支持下一代自主机器的新平台NVIDIA Isaac2018-06-06 4017

-

UltraScale如何支持下一代Ultra系统2019-01-08 2659

-

硬件加速器提升下一代SHARC处理器的性能2021-04-23 674

-

安森美的智能技术赋能记忆科技下一代服务器的每一个节点2021-09-14 3058

-

适用于下一代大功率应用的XHP™2封装2023-11-29 1034

-

安森美将为大众汽车集团的下一代电动汽车提供电源技术2024-07-23 1238

-

安森美推动数据中心能效革新2024-11-14 228

全部0条评论

快来发表一下你的评论吧 !