SiC功率器件性能和可靠性的提升

描述

在电力电子领域,碳化硅(SiC)技术对于推动向电动移动性的转变和提高可再生能源系统的效率至关重要。随着市场需求的增加,功率半导体公司面临着迅速扩大生产能力的压力。尽管4H-SiC材料的质量和可用性有了显著提升,但生产低缺陷密度和高性能SiC晶片以实现最佳产量的挑战依然存在。

为了应对这一紧迫需求,一种开创性的SiC工程基板被引入以满足行业需求。2023年9月,一条专用制造线的揭幕标志着重要里程碑,预示着这种创新SiC基板的大规模生产开始。这一战略举措有望彻底改变SiC技术的格局,为当前制造限制提供突破性解决方案,并为电力电子应用的效率和性能提升铺平道路。

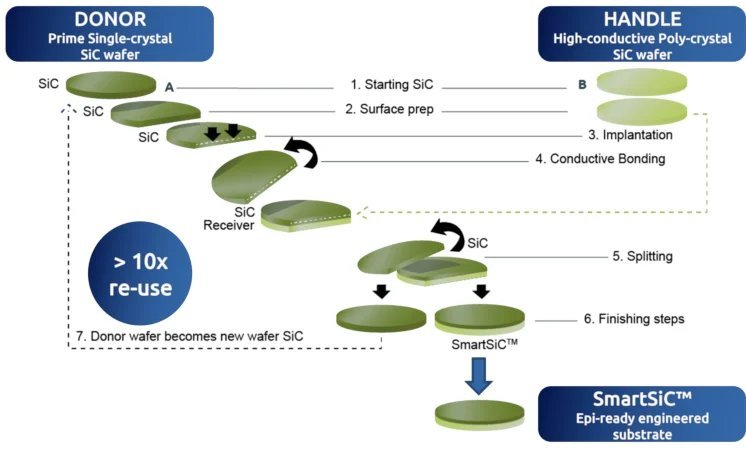

SmartSiC基板的制造依赖于Smart Cut技术,并在SiC器件制造中提供了显著优势。以下是其关键特性和益处的分解:

高质量SiC顶层:Smart Cut技术促进了高质量SiC层在支撑晶片上的转移,作为漂移外延生长的种子。这一过程对于优化器件产量和可靠性至关重要,确保最终器件符合严格的质量标准。

图1

图1

低电阻率支撑晶片:该技术采用低电阻率支撑晶片,典型电阻率为2 mOhm.cm(标准SiC材料电阻率约为20 mOhm.cm)。这一特性增强了器件导电性,同时实现了开关损耗的最小化,最终提高了基于SiC器件的应用的整体性能。

兼容不同晶片直径:Smart Cut技术兼容任何基板直径,适用于150 mm和200 mm晶片。

基于上述特性,获得的SmartSiC工程基板由亚微米厚(400至800 nm)的高质量单晶4H-SiC顶层和聚晶SiC支撑晶片组成。最终工程基板的厚度为150 mm晶片350 µm,200 mm晶片500 µm。这种组成确保了基板的结构完整性和性能,有助于SiC器件的可靠性和效率。

此外,通过使初始单晶供体晶片的可重复使用性成为可能,SmartSiC技术提供了对难以实现的SiC晶锭的最有效利用。与通常每晶锭最多提取50片晶片的传统SiC材料加工相比,Smart Cut技术可以从同一晶锭准备多达500个工程基板。这种生产力的显著提高代表了SiC器件制造的成本节约和资源高效解决方案。

应用于SmartSiC工程基板制造的Smart Cut过程如图1所示。

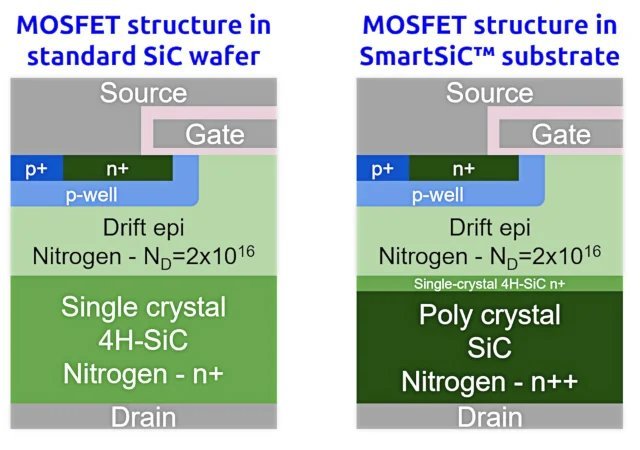

为了研究SmartSiC工程基板与标准单晶4H-SiC晶片的优点,在两种基板上制造了n型、13 mOhm/650 V Gen2平面SiC MOSFET,并作为单一批次同时处理。

作为参考的单晶4H-SiC晶片是氮掺杂的,典型电阻率为20 mOhm.cm,而SmartSiC基板的聚晶SiC支撑晶片具有更高的氮掺杂和典型电阻率为2 mOhm.cm。漂移外延是氮掺杂的,掺杂浓度ND≈2x1016cm-3。

图2

图2

磷和铝注入分别用于形成源极和体区域。栅氧化层是55nm厚的SiO2层,而高掺杂n型聚晶Si用作栅极电极。标准单晶SiC晶片和SmartSiC™基板上的测试车辆MOSFET结构如图2所示。

结果展示

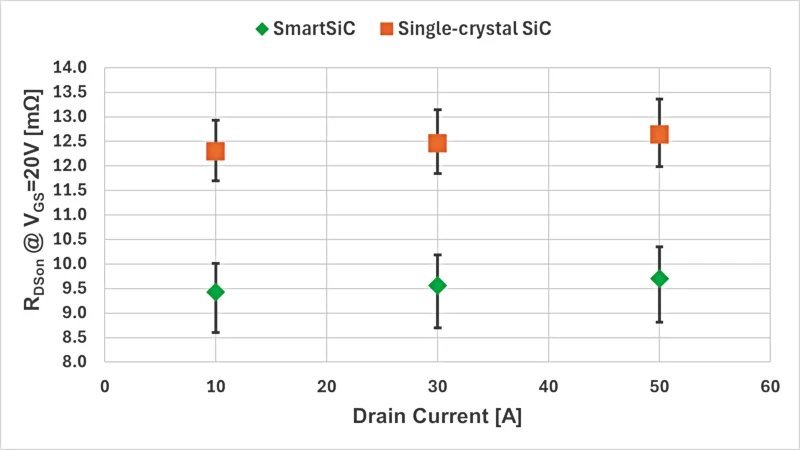

这里展示了在13 mOhm 650 V Gen2平面SiC MOSFET上获得的结果。

图3展示了器件的RDSon比较。结果显示,与SmartSiC基板相比,导通电阻平均降低了约24%。这一改进是由于SmartSiC基板的聚晶SiC支撑晶片的电阻率远低,以及其能够实现更低电阻率金属接触(在这种情况下是背面漏极接触)的能力。

图3

图3

如此强烈的RDSon降低(约24%)接近于从一代器件过渡到下一代时可以预期的水平。

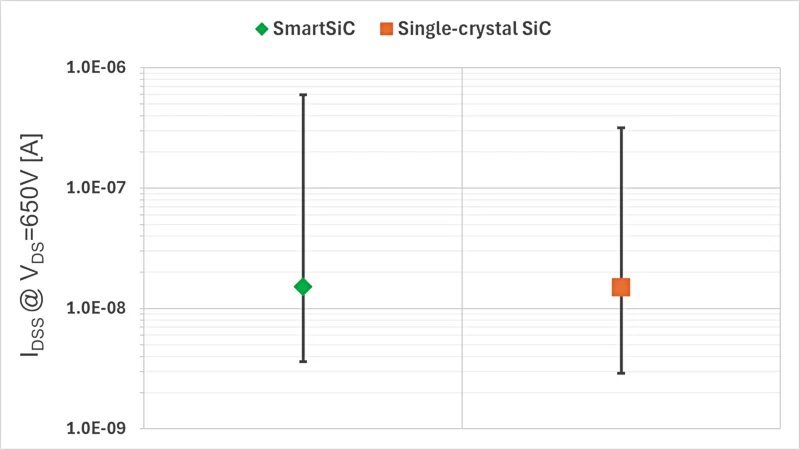

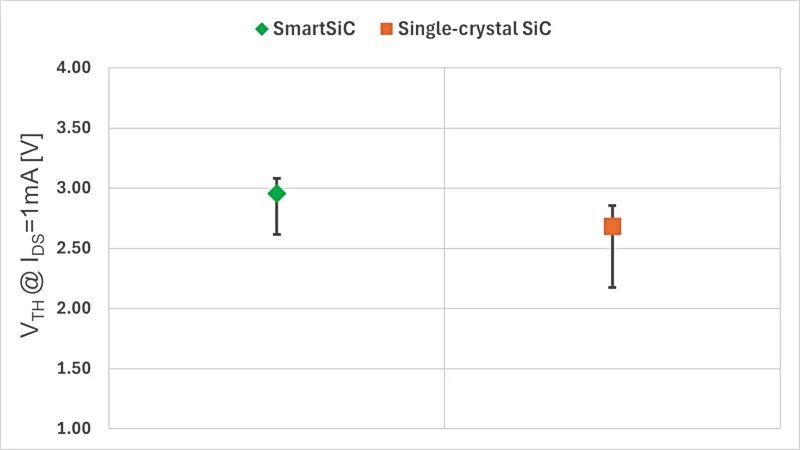

图4和图5分别展示了在单晶SiC晶片和SmartSiC基板上制造的同一器件的阈值电压和漏电流。结果显示,这两种基板在这些参数上表现出等效行为。

图4

图4

图5

图5

其他器件的潜力

如前所述,与电阻率约为20 mOhm.cm的标准单晶SiC基板相比,聚晶SiC材料可以实现低至1 mOhm.cm的电阻率,典型值约为2 mOhm.cm。此外,聚晶SiC的高掺杂水平有助于将接触电阻降低至远低于10 µOhm.cm²。这些特性使SmartSiC基板能够提高器件的电流密度,从而允许减小MOSFET和二极管的器件尺寸。

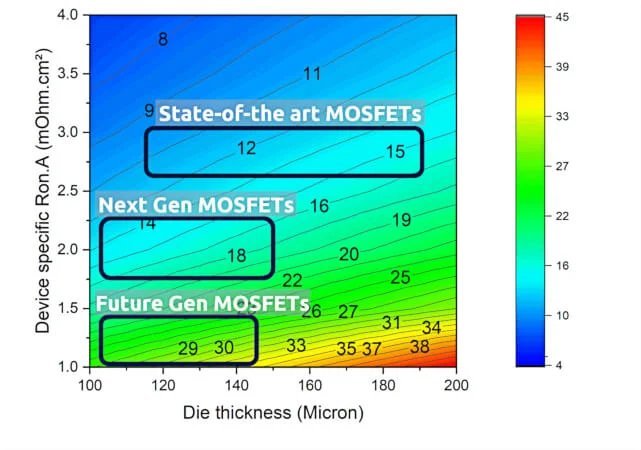

特别是对于FET,尽管总增益取决于初始器件特定电阻(Ron.A)和晶片厚度,但图6显示,FET技术越先进,获得的增益越高。我们所说的初始Ron.A是指器件在单晶SiC晶片上制造时的电阻。例如,对于初始Ron.A为2.8 mOhm.cm²和晶片厚度为180µm的FET,图5显示,在SmartSiC基板上制造时,新的Ron.A降低了15%(增益为15%)。请注意,这种增益与器件的电压等级无关。

前一段中提到的2.8 mOhm.cm²值对应于当前1200 V SiC MOSFET的先进水平。然而,当考虑到未来几年的器件代数时,预计Ron.A增益(减少)将超过20%,始终呈现出使用SmartSiC工程基板的优势,即“至少”多一代的优势。

极端增益情况出现在当今最先进的JFET中,这是400 V和800 V电动汽车固态断路器的首选。以750 V SiC JFET为例,初始Ron.A约为0.7 mOhm.cm²,预计增益约为30%。

图6

图6

最后但同样重要的是,初步分析显示,SmartSiC工程基板在特定电评估中进一步证实了其对双极退化的宝贵鲁棒性。这种退化现象出现在SiC基板上,是由于在暴露于高双极电流(由于电子和空穴同时存在)时,SiC晶体内的基平面位错(BPD)的滑动(扩展)。这通常发生在SiC MOSFET的反向导通期间,电流通过晶体管的PiN型体二极管。

为了验证这种鲁棒性,外延标准单晶SiC晶片和SmartSiC基板暴露于旨在揭示双极退化的应力条件下。这是通过使用ITES公司开发的E-V-C技术进行的。经过应力测试后,结果显示,与标准SiC晶片获得的结果相比,SmartSiC情况下的肖克利堆垛故障数量及其典型尺寸较低。结果表明,SmartSiC设计在抗双极退化方面具有固有的优势。这一特性之前通过在受到质子辐照的4H-SiC外延层上进行的正向电流应力测试进行了评估。

未来代数

在当前加速部署SiC器件以实现移动性和电力转换行业脱碳的背景下,SmartSiC提供了无与伦比的特性,允许更高的功率密度和更可靠的应用。

从在单晶SiC晶片和SmartSiC基板上制造的MOSFET获得的结果显示,后者提供的增益相当于从一代器件过渡到下一代时获得的增益。

在当前可用的器件代数上验证的增益显示,SmartSiC的优势在未来的器件代数中将更加明显,以及在Ron.A低得多的其他器件(如JFET)中。

-

深爱半导体 代理 SIC213XBER / SIC214XBER 高性能单相IPM模块2025-07-23 1199

-

如何测试SiC MOSFET栅氧可靠性2025-03-24 3091

-

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?2025-01-04 2577

-

提升SiC MOS器件性能可靠性的表面优化途径2023-12-12 2262

-

英飞凌如何控制基于SiC功率半导体器件的可靠性呢?2023-10-11 2420

-

SiC功率器件可靠性2023-08-07 513

-

碳化硅SiC MOSFET:低导通电阻和高可靠性的肖特基势垒二极管2023-04-11 2250

-

SiC-SBD的可靠性试验2023-02-08 1137

-

SiC功率器件的现状与展望!2022-11-11 2246

-

SiC MOSFET FIT率和栅极氧化物可靠性的关系2022-07-12 13930

-

SiC MOSFET:经济高效且可靠的高功率解决方案2019-07-30 4254

-

SiC-MOSFET的可靠性2018-11-30 4809

-

电子元器件的可靠性筛选2016-11-17 6494

全部0条评论

快来发表一下你的评论吧 !