如何简化PCIe 6.0交换机的设计

描述

本文翻译转载于:Cadence blog

作者:Deep Mehta

由于全球数据流量呈指数级增长,PCIe 6.0 交换机的市场需求也出现了激增。PCIe 6.0 交换机在高性能计算(HPC)系统(尤其是数据中心)中为需要大带宽和超低延迟的应用提供了重要的数据传输支持。然而,确保这些交换机严格满足性能、能效和成本等要求是一项艰巨的挑战。尽管如此,全面的测试和验证过程还是能够降低这些交换机设计的复杂性。

传统的验证方法仍具有价值,如 PCIe 5.0 交换机采用数据完整性和虚拟通道仲裁测试。尽管如此,PCIe 6.0 要求采用更全面的验证方法——比基本功能验证更深入的高阶验证策略,其中包括生成用于识别潜在性能问题并确保交换机在实际场景中以最佳状态运行的反向压力流量。只有主动应对这些挑战,才能设计出满足高性能计算应用要求的低延迟、高带宽交换机。

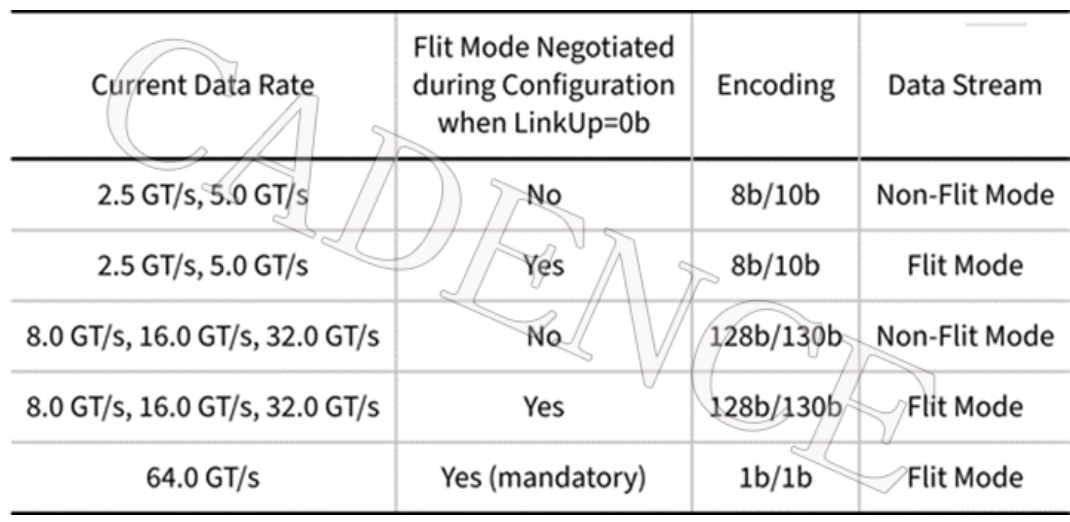

Flit 模式和非 Flit 模式的互操作性

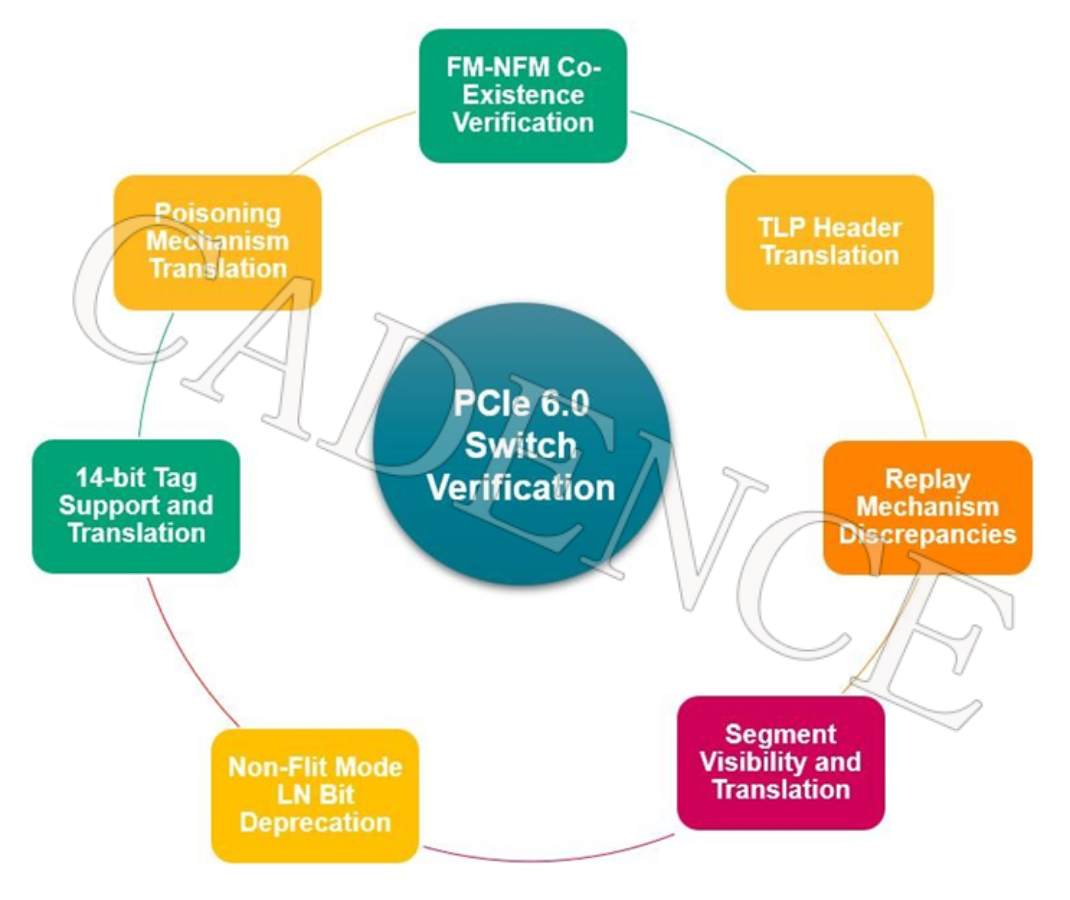

PCIe 6.0 新增的 Flit 模式对交换机提出了全新的验证挑战。如下图所示,我们可以将验证分为几个关键领域来思考。

● 共存验证:交换机必须能够有效处理通过不同端口的 Flit 模式(FM)和非 Flit 模式(NFM)的混合流量。这种验证方法确保了交换机的性能不会因为流量模式的异构性而降低。

● 事务层数据包(TLP)的数据头转换:NFM 和 FM 使用不同的数据头格式。当入口端和出口端采用不同运行模式时,交换机就需要对不同格式进行转换,验证策略的重点是确保该转换过程的正确性。

● 重传机制差异:FM 和 NFM 使用不同的重传机制。验证策略必须考虑这些差异,才能在重传期间妥善处理传输错误并确保数据完整性。

● 段的可见性和转换:段信息仅可在 FM 链路中直接访问,这使得 FM 和 NFM 事务层数据包(TLP)之间的路由变得更复杂,尤其是当入口端和出口端采用不同运行模式时。例如,交换机有时会报告 TLP 转换出口被阻止的错误,因此必须根据转换规则进行验证。

设备 3 的能力寄存器具有一个“段捕获”位;交换机在将一项 TLP 从 NFM 转换为 FM 时,必须遵循段捕获位的具体规则。

● 弃用 NFM 中的 LN 位:PCIe 6.0 弃用了 NFM 中使用的 LN(轻量级通知)位。验证策略必须针对弃用的 LN 位制定专门的转换规则。

● 14 位标签支持和转换:14 位标签是 FM 独有的。PCIe 规范规定了将请求从 FM 转换为 NFM 的具体转换规则,以解决标签位数差异的问题。

● 中毒机制转换:如果在 FM TLP 转换为 NFM TLP 的过程中应用了任一种中毒机制,则必须设置 NFM TLP 的错误中毒位(EP位)。相反,从 NFM 转换到 FM 时,如果在 NFM TLP 中设置了 EP 位,则该 EP 位必须在转换后的 FM TLP 中保留。验证策略应确保交换机遵循这些中毒机制的转换规则。

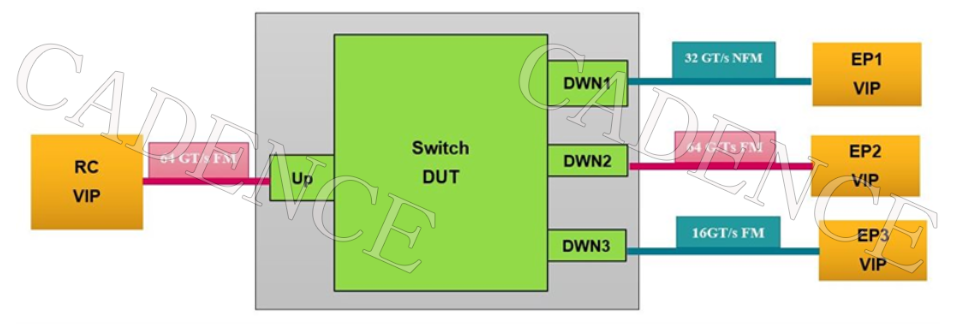

通过全面验证这些互操作性,设计人员可确保 PCIe 6.0 交换机有效且稳定地处理 FM 和 NFM 的混合流量。以下拓扑图展示了交换机端口上混合模式流量(FM 和 NFM)的一个示例场景,其中包含一个上行端口和三个下行端口,分别与根复合体(RC)和各个端点(EP)连接。

应考虑的性能损失

虽然应用这些转换规则和各种共享或专用信用管理能够简化交换机的设计,但在 Flit 模式下添加额外的无操作(NOP)流控单元或 NOP TLP 可能增加性能损失,并额外增加非 Flit 模式中的逻辑空闲(IDL)双字节。这也是现在必须在交换机设计的验证和验收标准中进行性能测试的原因。

交换机验证可以通过流量建模、延迟监控和缓冲区分析来识别和纠正性能问题。

● 流量建模:通过将大量 Flit 模式流量与非 Flit 模式流量互相转换,开发模拟真实世界流量模式的测试场景。测试策略需要根据随机因素评估,如不同的传输速度、链路宽度,以及生成的不同 TLP 类型的流量,确保所有交换机端口都采用了 Flit 模式和非 Flit 模式进行验证。

● 延迟监控:监控数据包在通过交换机时产生的延迟,并重点关注频繁转换模式的路径,找出可能表明转换过程效率低下的异常延迟峰值。

● 缓冲区分析:分析在流量模拟过程中交换机内部缓冲区的行为。必须识别出任何接近满载或溢出的缓冲区场景,因为这种情况可能表明过多的转换负载导致出现潜在的性能问题。换言之,交换机端口必须根据协议标准的规定对 TLP(包括“保留”TLP)进行缓冲和路由。

总 结✦

Summary

PCIe 6.0 标准为 PCIe 协议的分层堆栈带来了革命性的变化,其中最具颠覆性的创新是采用了“Flit”。根据标准的要求,交换机入口端会接收一个包含多目标 TLP 的 Flit 数据包,这些多目标 TLP 需要简化路由逻辑,才能利用转换逻辑将数据发送到相应的出口端(反之亦然)。在应用经 OHC 封装的转换逻辑时,不同的共享或专用信用管理和 TLP 重传机制的交换机路由逻辑可能会增加性能损失,仅验证数据集成测试无法识别出这种性能损失。必须对性能测试策略加以评估,才能确保对所有支持 Flit 模式和非 Flit 模式流量的交换机端口进行全面验证。此外,性能测试还有助于识别在不同负载条件(即有效负载长度)下可能出现的潜在瓶颈或问题。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续十年名列美国财富杂志评选的 100 家最适合工作的公司。

-

如何实现POE交换机串联?2025-03-25 1449

-

接入层交换机、汇聚层交换机和核心层交换机的区别2021-06-04 8066

-

交换机如何工作2009-08-01 1081

-

PCIe_交换机产品列表_产品快照2016-01-06 710

-

工业控制交换机和工业交换机的区别2020-01-21 2926

-

核心交换机、汇聚交换机与普通交换机的区别介绍2020-03-19 14258

-

家庭交换机怎么安装_交换机网速是平分的吗2020-03-25 11627

-

网络交换机的作用_网络交换机怎么用2020-04-02 7359

-

什么是网络交换机?网络交换机的分类标准2022-08-10 4686

-

核心交换机、汇聚交换机、接入交换机之间的对比分析2022-11-02 27439

-

pcie2.0交换机资料2023-03-27 869

-

PoE交换机可以当普通交换机使用吗2023-06-27 10843

-

以太网交换机的升级版:PCIe交换机2023-07-17 4272

-

PCIe交换机与路由器的区别2024-11-26 2073

-

0.1-6.0 GHz DPDT 交换机 skyworksinc2025-08-07 108

全部0条评论

快来发表一下你的评论吧 !