怎么建设Xilinx FPGA Artix-7教学实验室?山西工学院给您答案

描述

山西工学院是经教育部批准成立的一所省属公办全日制理工类普通本科高等学校。按照省委、省政府部署,在朔州市委、市政府的大力支持下,学校于2021年6月3日正式挂牌成立。

学校积极探索应用型高校人才培养模式创新,坚持“高校+产业研究院+龙头企业/行业”的特色发展模式,以建设现代产业学院为抓手,确定了工程化、智能化、管理化的人才培养特色,基本形成与我省的新兴产业集群和朔州经济社会发展需求对接的二级产业学院设置模式。

信息产业学院是山西工学院下设的二级学院。学院精准对接新一代信息技术应用创新领域,聚焦大数据、人工智能、云计算、虚拟现实、工业互联网、工业应用软件、智能感知、机器视觉、数字图像处理、智能信息处理,智能控制和现代通信技术等信息产业,牢牢把握培养产业需要的高素质应用型人才这条主线,奋力推进学院全方位高质量发展。

2►

培训情况

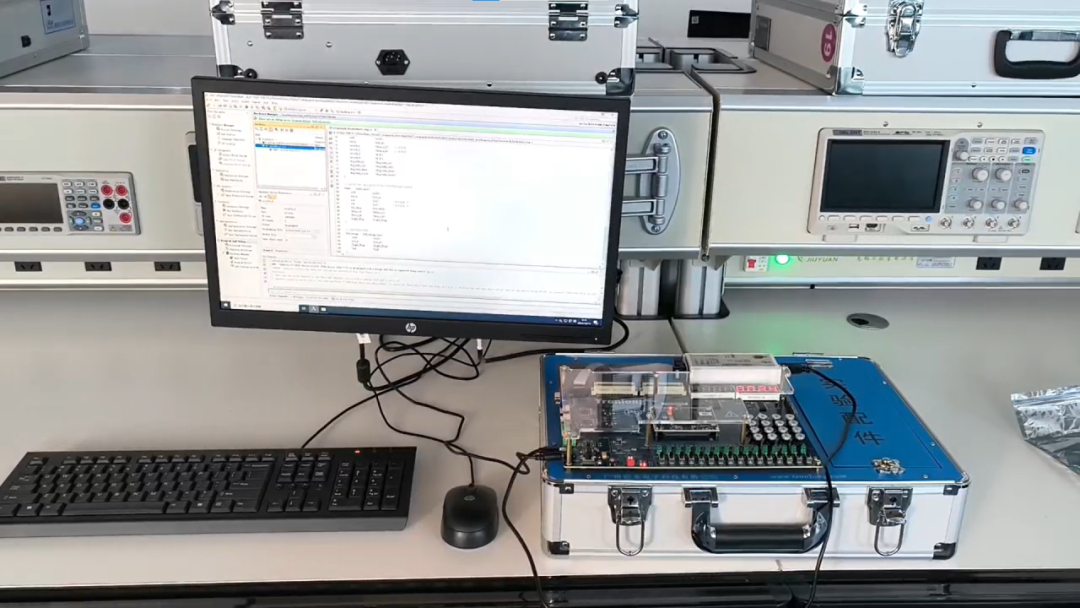

创龙教仪联合山西工学院共同建设FPGA教学平台,在信息产业学院-信息产业基础综合实验室,针对FPGA课程,探讨了该课程的应用方向,制定学生课程学习的培养计划。

TLA7-TEB相关实验(部分) | |

FPGA实验环境搭建与Vivado开发基础 | FPGA实验环境搭建 |

触发器设计实验 | 同步RS触发器的设计实验 |

组合逻辑实验 | 多数表决器实验(IP核) 四位二进制加法器实验 |

时序逻辑实验 | 时钟同步状态机的设计实验 同步计数器74x163的实现实验 |

FPGA基础外设实验 | 数码管显示实验 矩阵键盘实验 |

综合实验 | 电子秒表综合设计实验 DAC呼吸灯实验 篮球比赛24秒倒计时电路设计实验 简易洗衣机定时正反转控制电路设计实验 |

老师对于新内容表达出十足的热情,并对创龙教仪专业的技术能力与认真的工作态度表示了肯定。

面对日新月异的技术发展,创龙教仪在不断学习与探索新技术与高校新需求之间的联系,并通过不断改进的产品助力高校培养能够适应新社会生产需求的高级人才,以响应国家二十大“产教融合”的方针!

3►

特色案例

实验名称:

同步RS触发器的设计实验

实验目的:

(1) 掌握同步RS触发器的逻辑功能。

(2) 掌握同步RS触发器的Verilog实现。

(3) 掌握同步RS触发器的仿真图查看。

实验原理:

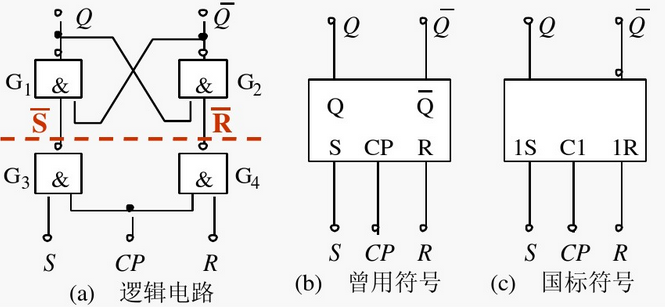

1、RS同步触发器

在实际应用中,通常要求触发器的状态按一定的时间节拍变化,即在时钟脉冲到达时,才根据输入信号改变状态;没有时钟信号时,即使输入信号改变,也不影响触发器的输出状态。为此,增加时钟脉冲输入端CP以及相应的输入控制电路,就有了同步RS触发器这一类数字芯片。同步RS触发器逻辑电路图如下所示:

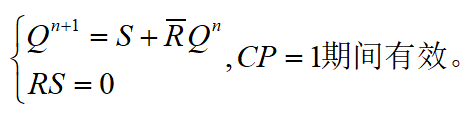

CP=0时,,触发器保持原来的状态不变;

CP=1时,工作情况与基本RS触发器相同。

特性方程如下:

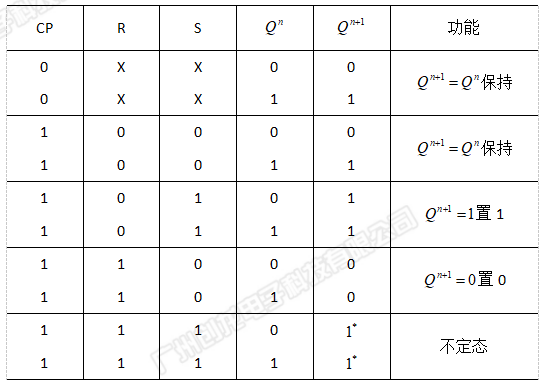

逻辑特性表如下:

同步RS触发器的主要特点如下:

(1) 时钟电平控制。在CP=1期间接收输入信号,CP=0时状态保持不变,与基本RS触发器相比,对触发器状态的转变增加了时钟控制。

(2) R、S之间有约束,不能允许出现R和S同时为1的情况,否则会使触发器处于禁止状态。

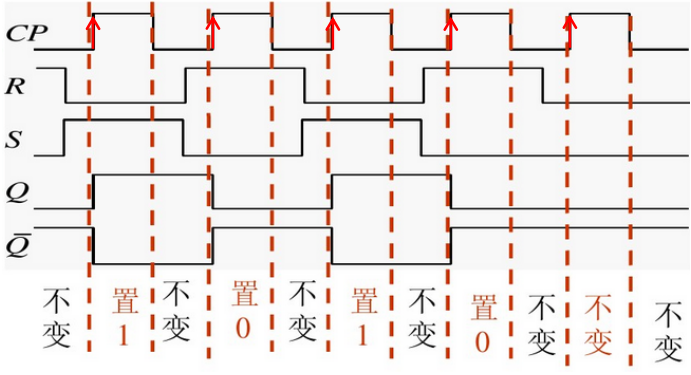

同步RS触发器(上升沿触发)的时序图如下所示:

实验操作:

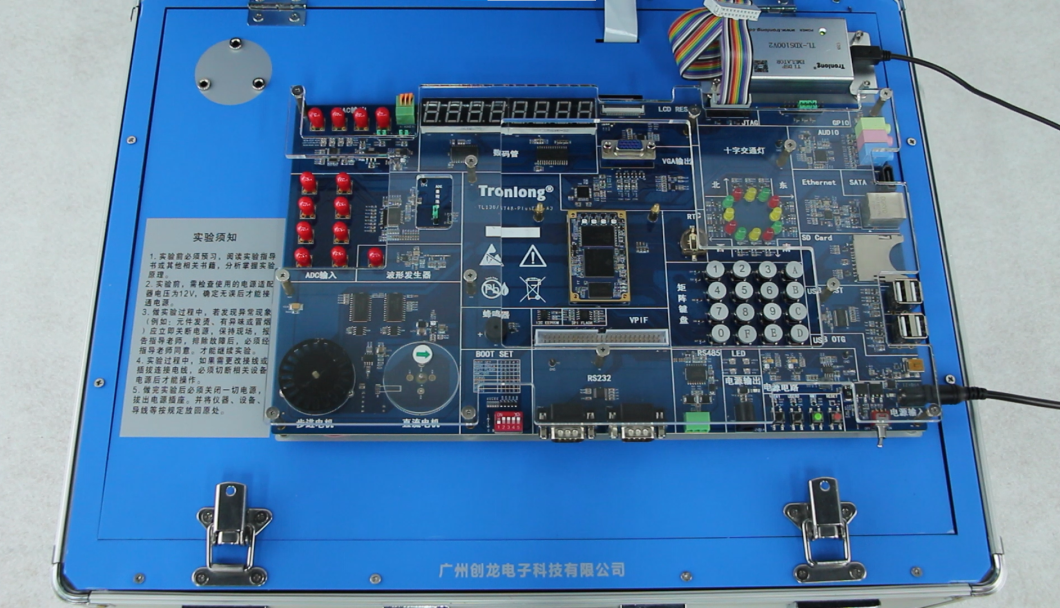

1、实验设备

(1) 软件:Vivado2015.2,Windows7以上操作系统。

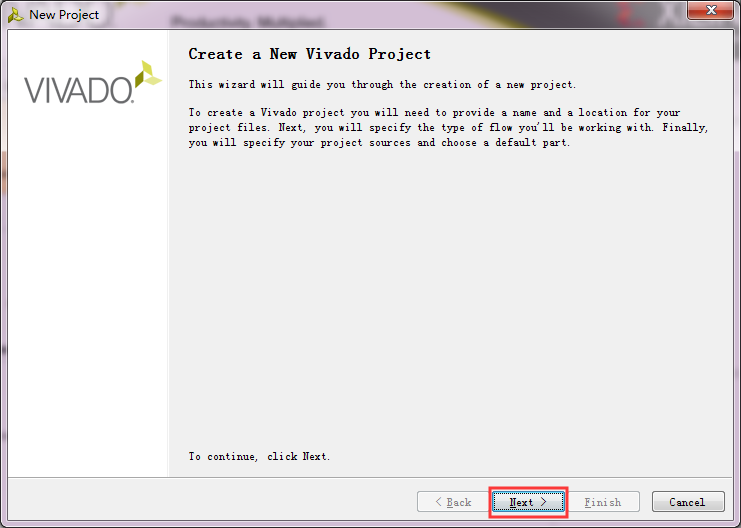

打开Vivado2015.2软件

创建一个新的工程

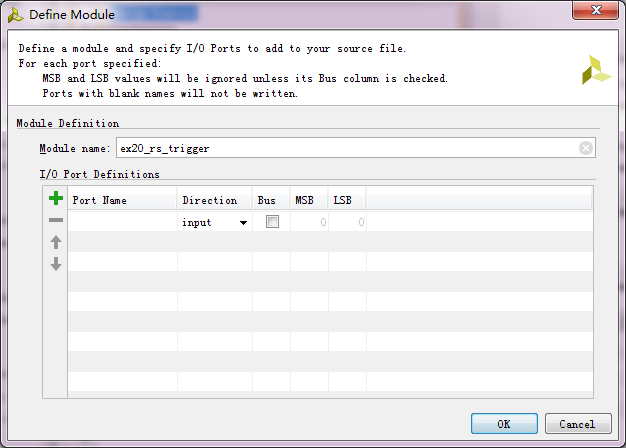

创建源文件

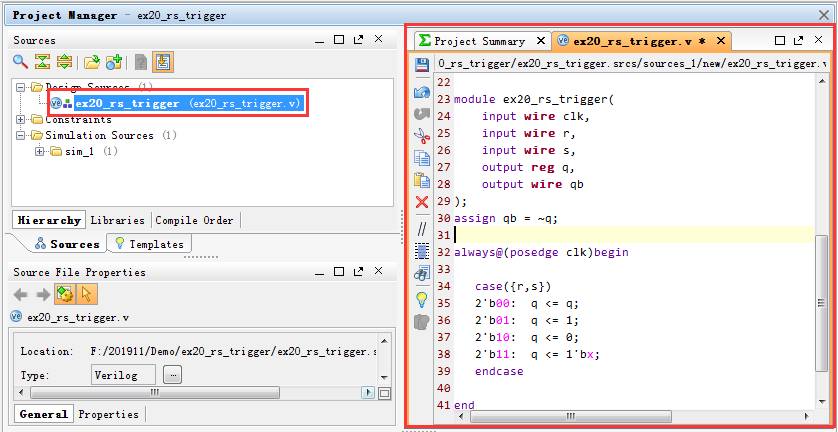

编写代码

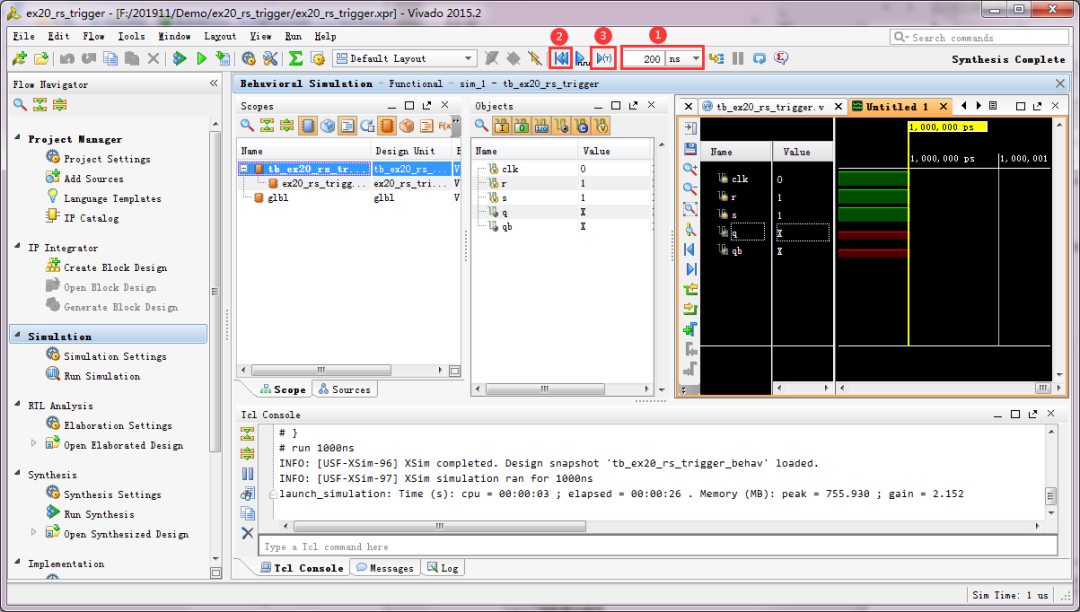

编写仿真代码 - 代码仿真

指定时间和单位为200ns后,运行

实验结果:

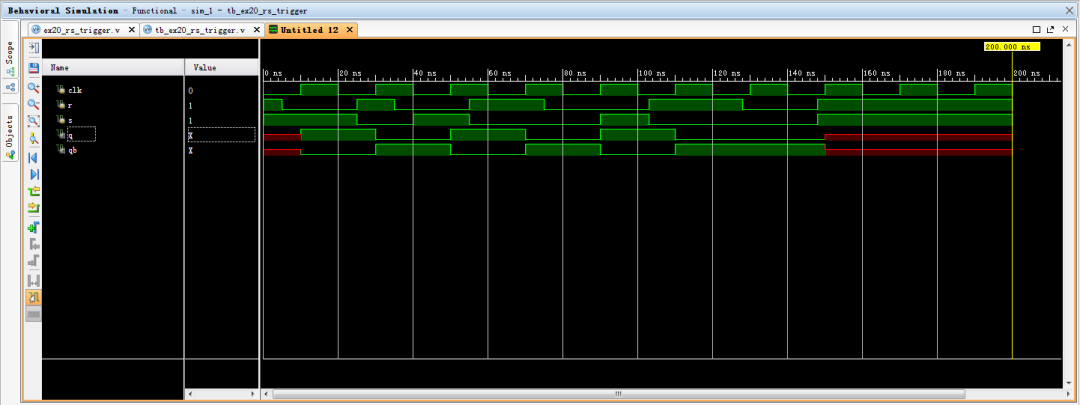

(1)信号含义。

clk:时钟信号CP,上升沿触发;

r:RS触发器的输入R;

s:RS触发器的输入S;

q:RS触发器的输出;

qb:输出q的取反。

(2)第一个时钟周期的上升沿到来之前,触发器输出状态不定(显示红色),RS触发器无效;从第一个时钟周期的上升沿开始,RS触发器有效,在时钟上升沿触发。R和S同时为1时,输出不定值(显示红色)。如下图所示:

4►

设备概述

//

产品型号:TLA7-TEB

处理器类型:Xilinx Artix-7

应用领域:通信、测控、电子

兼容紫光同创国产Logos-2芯片

产品型号:TLPG2L-TEB

处理器类型:紫光同创 Logos-2

应用领域:通信、视频图像处理、工业控制、医疗、消费电子

产品特点:基于紫光同创 Logos-2 系列 FPGA 处理器,逻辑单元 99900 个,DSP Slice 240 个;

-

FPGA教学实验室建设必要性 解决方案概述2024-07-26 932

-

怎么建设Xilinx FPGA Artix-A7教学实验室?山西工学院给您答案2024-07-05 1793

-

力促人才培养,东莞理工学院携手泰克共建微电子创新实验室!2023-10-13 1652

-

常熟理工学院计算机科学与技术嵌入式培养2021-07-16 1616

-

Artix-7 FPGA数据表下载2021-05-21 1313

-

如何减轻SEU对Artix-7 FPGA的影响2020-07-14 2342

-

如何使用Artix-7 FPGA减少功耗2018-11-21 4487

-

Xilinx的Artix-7 FPGA AC701评估套件专门支持高性能系统2018-09-26 2831

-

Artix-7 DSP性能演示2018-06-05 5323

-

面向大批量应用的的Artix-7 FPGA的能耗优势演示2018-06-04 3984

-

Artix-7 50T FPGA开发板接口功能测试实例2016-08-04 3068

-

RS与新家坡共和理工学院共建电子产品设计实验室2014-02-11 1194

全部0条评论

快来发表一下你的评论吧 !