高速PCB设计解决EMI问题的九大规则

PCB

描述

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过高速PCB来解决。以下是九大规则:

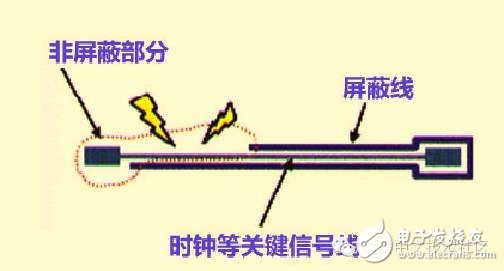

规则一:高速信号走线屏蔽规则

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

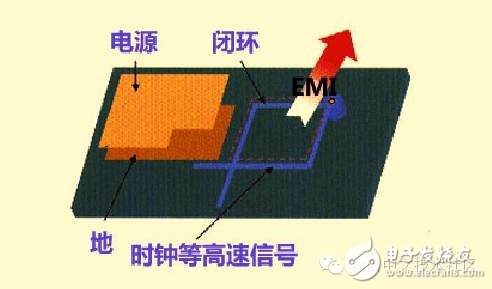

规则二:高速信号的走线闭环规则

由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

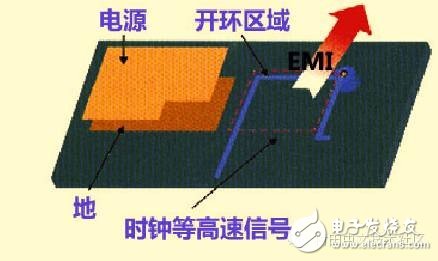

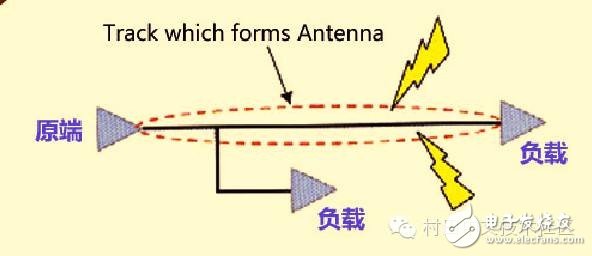

规则三:高速信号的走线开环规则

规则二提到高速信号的闭环会造成EMI辐射,然而开环同样会造成EMI辐射。

时钟信号等高速信号网络,在多层的PCB走线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。

规则四:高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。

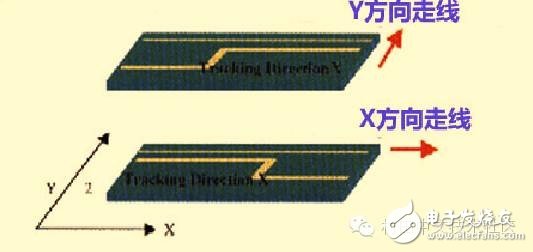

规则五:高速PCB设计的布线方向规则

相邻两层间的走线必须遵循垂直走线的原则,否则会造成线间的串扰,增加EMI辐射。

简而言之,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。

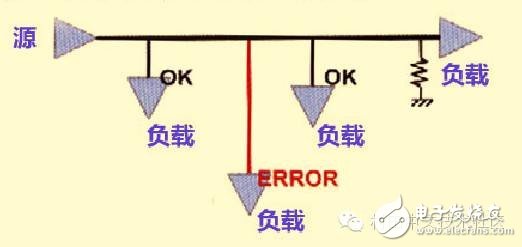

规则六:高速PCB设计中的拓扑结构规则

在高速PCB设计中,线路板特性阻抗的控制和多负载情况下的拓扑结构的设计,直接决定着产品的成功还是失败。

图示为菊花链式拓扑结构,一般用于几Mhz的情况下为益。高速PCB设计中建议使用后端的星形对称结构。

规则七:走线长度的谐振规则

检查信号线的长度和信号的频率是否构成谐振,即当布线长度为信号波长1/4的时候的整数倍时,此布线将产生谐振,而谐振就会辐射电磁波,产生干扰。

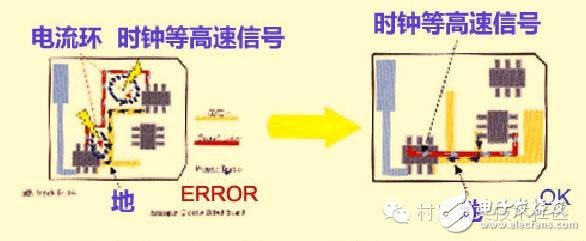

规则八:回流路径规则

所有的高速信号必须有良好的回流路径。尽可能地保证时钟等高速信号的回流路径最小。否则会极大的增加辐射,并且辐射的大小和信号路径和回流路径所包围的面积成正比。

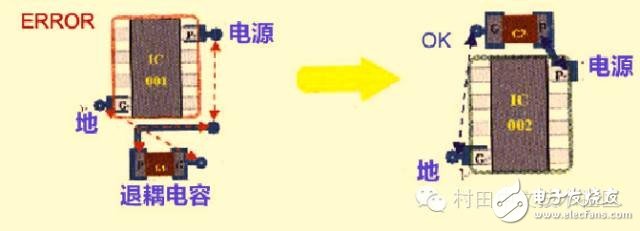

规则九:器件的退耦电容摆放规则

退耦电容的摆放的位置非常的重要。摆放不合理根本起不到退耦的效果。其原则是:靠近电源的管脚,并且电容的电源走线和地线所包围的面积最小。

-

高速PCB设计EMI避坑指南:5个实战技巧2025-11-10 793

-

高速PCB设计EMI防控手册:九大关键步骤详解2024-12-24 1253

-

高速PCB设计EMI之九大规则2022-11-04 1273

-

高速PCB布线技巧、EMI问题、设计规则2021-03-31 8038

-

高速PCB设计EMI有什么规则2019-08-21 1466

-

高速PCB设计EMI的九大规则概述2019-07-25 2421

-

PCB设计EMI的高速信号走线规则2019-05-06 5209

-

硬件工程师谈高速PCB信号走线的九个规则2018-09-20 3302

-

PCB设计高速模拟输入信号走线方法及规则2018-05-25 10217

-

高速PCB设计抗EMI干扰的九大规则,你都知道吗?2018-04-13 2250

-

解决高速PCB设计EMI(电磁干扰)的九大规则2017-11-02 2956

-

高速PCB设计解决EMI问题的九大规则2016-01-19 4199

-

高速PCB设计时应从哪些方面考虑EMC、EMI的规则2009-03-20 1581

全部0条评论

快来发表一下你的评论吧 !