ADI时钟抖动衰减器优化JESD204B串行接口功能

处理器/DSP

描述

中国,北京—Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,最近推出一款高性能时钟抖动衰减器HMC7044,其支持JESD204B串行接口标准,适用于连接基站设计中的高速数据转换器和现场可编程门阵列(FPGA)。JESD204B接口专门针对高数据速率系统设计需求而开发,3.2 GHz HMC7044时钟抖动衰减器内置可以支持和增强该接口标准特性的独特功能。HMC7044提供50 fs抖动性能,可改善高速数据转换器的信噪比和动态范围。该器件提供14路低噪声且可配置的输出,可以灵活地与许多不同的器件接口。HMC7044还具有各种时钟管理和分配特性,使得基站设计人员利用单个器件就能构建完整的时钟设计。

基站应用中有许多串行JESD204B数据转换器通道需要将其数据帧与FPGA对齐。HMC7044时钟抖动衰减器可在数据转换器系统中产生源同步且可调的样本和帧对齐(SYSREF)时钟,使JESD204B系统设计得以简化。该器件具有两个锁相环(PLL)和重叠的片内压控振荡器(VCO)。第一PLL将一个低噪声、本地压控时钟振荡器(VCXO)锁定至噪声相对较高的参考,而第二PLL将VCXO信号倍频至VCO频率,仅增加非常小的噪声。对于蜂窝基础设施JESD204B时钟产生、无线基础设施、数据转换器时钟、微波基带卡和其它高速通信应用,HMC7044架构可提供出色的频率产生性能,相位噪声和积分抖动均很低。

HMC7044时钟抖动衰减器主要特性

支持JEDEC JESD204B

超低均方根抖动:50 fs(12 KHz至20 MHz,典型值)

噪底:-162 dBc/Hz (245.76 MHz)

低相位噪声:《-142 dBc/Hz(800 kHz至983.04 MHz输出频率)

PLL2提供多达14路差分器件时钟

支持最高5 GHz的外部VCO输入

片内稳压器提供出色的PSRR

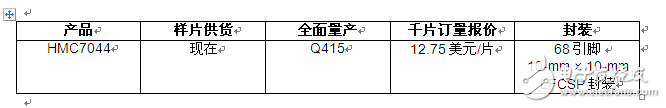

报价与供货

关于ADI公司

Analog Devices, Inc.(简称ADI)始终致力于设计与制造先进的半导体产品和优秀解决方案,凭借杰出的传感、测量和连接技术,搭建连接真实世界和数字世界的智能化桥梁,从而帮助客户重新认识周围的世界。

-

JESD204B的优势2022-11-23 767

-

JESD204B协议介绍2022-11-21 945

-

如何采用系统参考模式设计JESD204B时钟2022-11-18 779

-

宽带数据转换器应用的JESD204B与串行LVDS接口考量2021-11-01 6491

-

如何去实现JESD204B时钟?2021-05-18 3131

-

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?2021-04-06 3069

-

HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路输出抖动衰减器2021-03-21 1694

-

JESD204B串行接口时钟的优势2019-06-19 3734

-

串行LVDS和JESD204B的对比2019-05-29 3169

-

在Xilinx FPGA上快速实现JESD204B2018-10-16 3709

-

JESD204B的系统级优势2018-09-18 2404

-

简述Arria10接口JESD204B的与ADI9144性能2018-06-20 5477

-

JESD204B在时钟方面的设计及其验证实现2017-11-18 2565

-

JESD204B 串行接口时钟需要及其实现2016-12-21 1890

全部0条评论

快来发表一下你的评论吧 !