GPMC并口多通道AD采集案例,基于TI AM62x四核处理器平台!

电子说

描述

GPMC并口简介

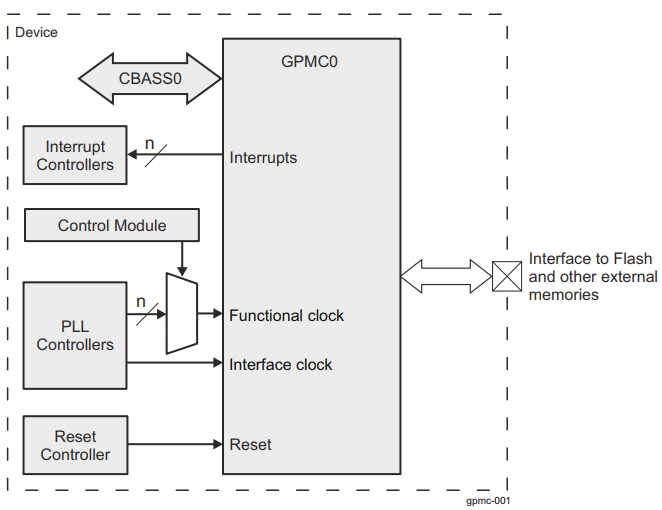

GPMC(General Purpose Memory Controller)是TI处理器特有的通用存储器控制器接口,是AM62x、AM64x、AM437x、AM335x、AM57x等处理器专用于与外部存储器设备的接口,如:

(1)FPGA器件

(2)ADC器件

(3)SRAM内存

(4)NOR/NAND闪存

图 1

GPMC并口特点

(1)小数据-低时延

在工业自动化控制领域中,如工业PLC、驱控一体控制器、运动控制器、CNC数控主板、继电保护设备、小电流接地选线等,极其注重精确性与快速性,GPMC并口“小数据-低时延”的特点显得格外耀眼,能够很好地提高数据传输效率,降低传输成本。

(2)大数据-高带宽

大数据时代对能源电力领域的数据量传输、数据处理等方面提出了更高的要求。GPMC提供了最大的灵活性,以支持四个可配置片选中不同的时序参数和位宽配置。可根据外部设备的特点,使用最佳的片选设置。可通过配置GPMC接口的时序参数和不同工作模式,最大速率可超过100MB/s。因此,GPMC“大数据-高带宽”的特点在能源电力领域扮演着重要角色。

(3)低成本-低功耗

“低成本、低功耗、高性能”是如今智能设备发展趋势,GPMC并口相对于PCIe串行接口,成本更低、功耗更低。两者都为常用的通信接口,均可满足高速通信要求,但在与FPGA通信的时候,用户往往更喜欢选用GPMC并口,因为:

1、使用低成本FPGA即可实现高速通信,而具备PCIe接口的FPGA成本则成倍增长。

2、具备PCIe接口的FPGA功耗往往较大,而低成本FPGA功耗较小。一般而言,低功耗器件的使用寿命也将更长。

AM62x典型应用领域

AM62x应用领域十分广泛,涵盖工业PLC、运动控制器、边缘计算网关、工商业储能EMS、汽车充电桩、血液分析仪等领域,可满足多种工业应用要求。

基于GPMC的多通道AD采集案例演示

下文主要介绍基于GPMC的多通道AD采集案例演示,为了简化描述,仅摘录案例功能描述与测试结果,详细产品资料请扫描文末二维码下载。

案例说明

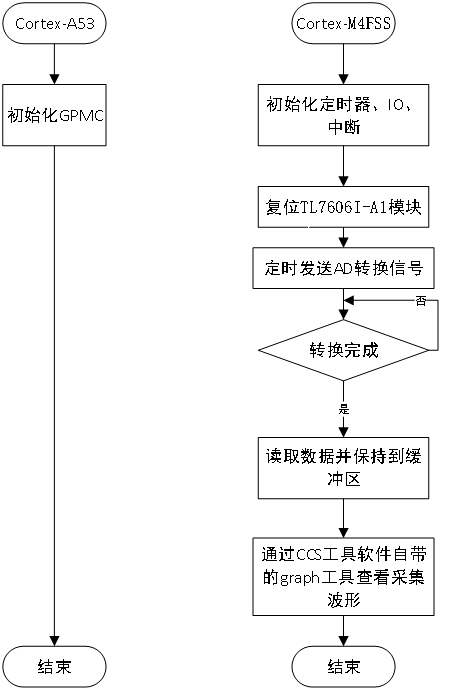

案例功能:AM62x通过Cortex-A53核心启动Linux系统以初始化GPMC接口,Cortex-M4FSS核心通过GPMC接口采集TL7606I-A1模块的8个通道数据,通过仿真器结合CCS软件查看对应通道数据的波形。

系统流程图如下所示:

图 3

原理说明如下:

(1)Cortex-A53核心:

运行Linux系统以初始化GPMC接口,启动Cortex-M4FSS核心。

(2)Cortex-M4FSS核心:

周期性发送AD转换信号,触发TL7606I-A1模块进行AD转换,待转换完成后通过GPMC接口读取、保存TL7606I-A1模块的8个通道数据,结合调试工具、CCS软件将AD转换后的数据转换为可视化的波形。

硬件连接

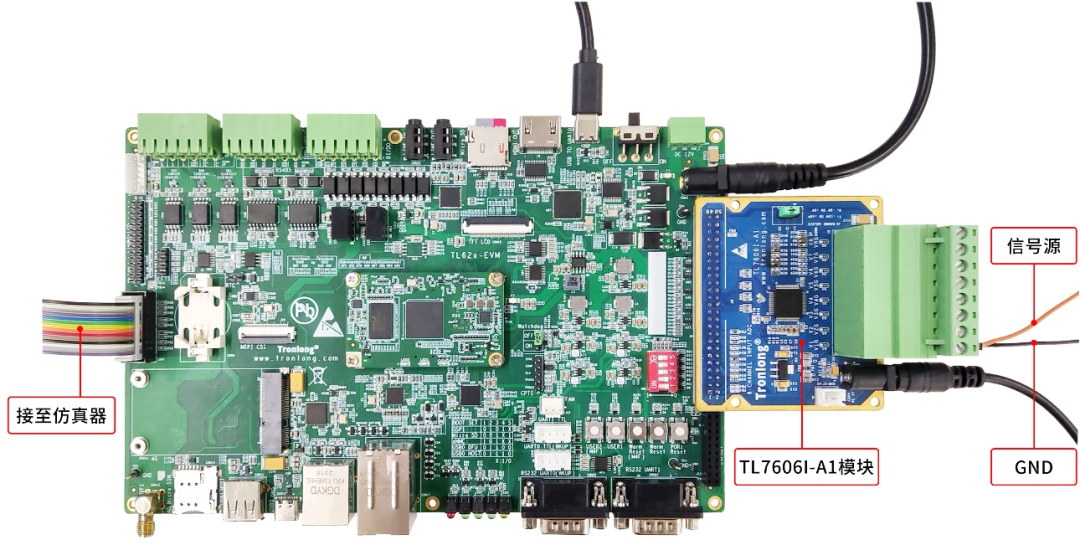

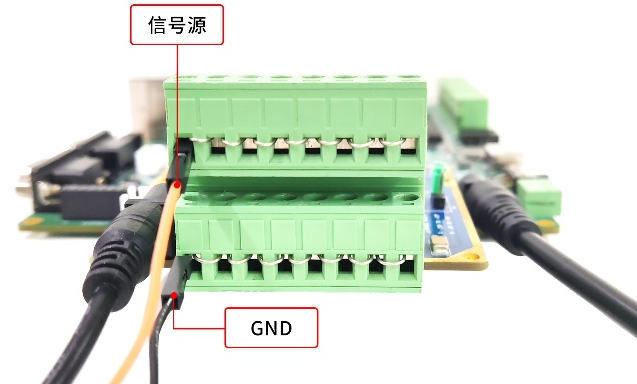

请将创龙科技TL7606I-A1模块插至评估板GPMC(J9)扩展接口,并使用5V电源对模块进行独立供电。

请使用信号发生器输出频率为1KHz、峰峰值为2Vpp(即幅值为1V)的正弦波信号,信号输入至TL7606I-A1模块的8个通道。使用创龙科技TL-XDS200仿真器连接评估板TI Rev B JTAG(CON7)接口至PC端。

备注:信号发生器输出信号请勿超过TL7606I-A1模块量程,否则可能会导致模块损坏。

图 4 TL7606I-A1模块硬件连接示意图

图 5 TL7606I-A1模块硬件连接示意图

为了使评估板兼容TL7606I-A1模块的J6接口,需将评估板J9接口的pin3、pin4、pin6引脚分别连接到评估板J11接口的pin10、pin4、pin6引脚,分别对应TL7606I-A1模块的信号转换、信号复位、信号转换状态功能引脚,请按下表引脚对应关系飞线连接评估板J9接口与J11接口。

表 1

| GPMC(J9)接口 | J11接口 |

| pin3 | pin10 |

| pin4 | pin4 |

| pin6 | pin6 |

案例测试

请参考我司产品资料的用户手册,进行配置运行环境、运行Cortex-M4FSS核心程序等操作,8通道数据采集以及单通道数据采集的测试结果如下所示。

(1)8通道数据采集

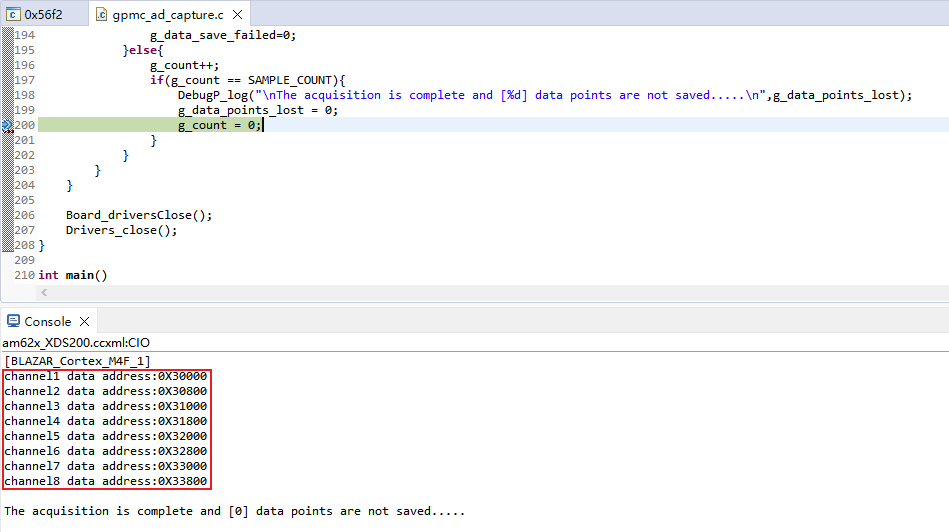

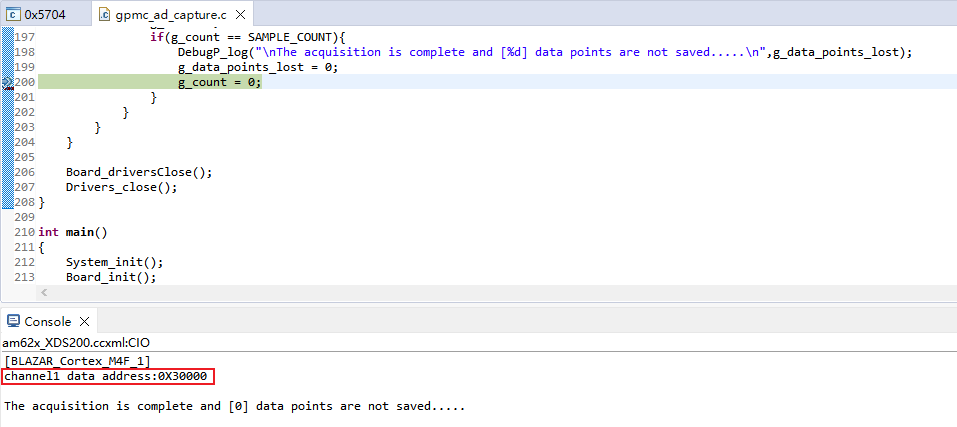

程序运行后在CCS软件的控制台输出8个通道数据保存的首地址以及数据点保存结果。

图 6

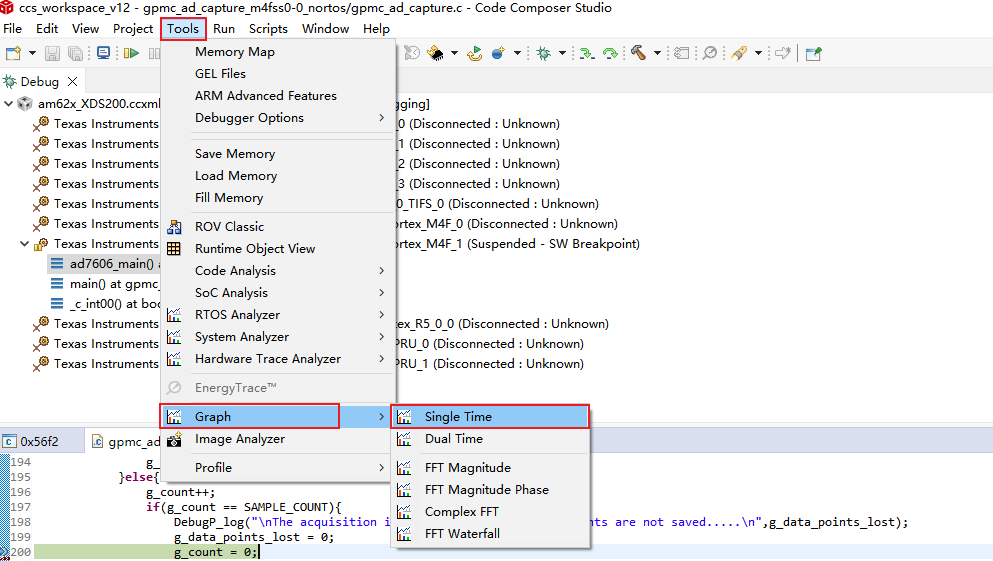

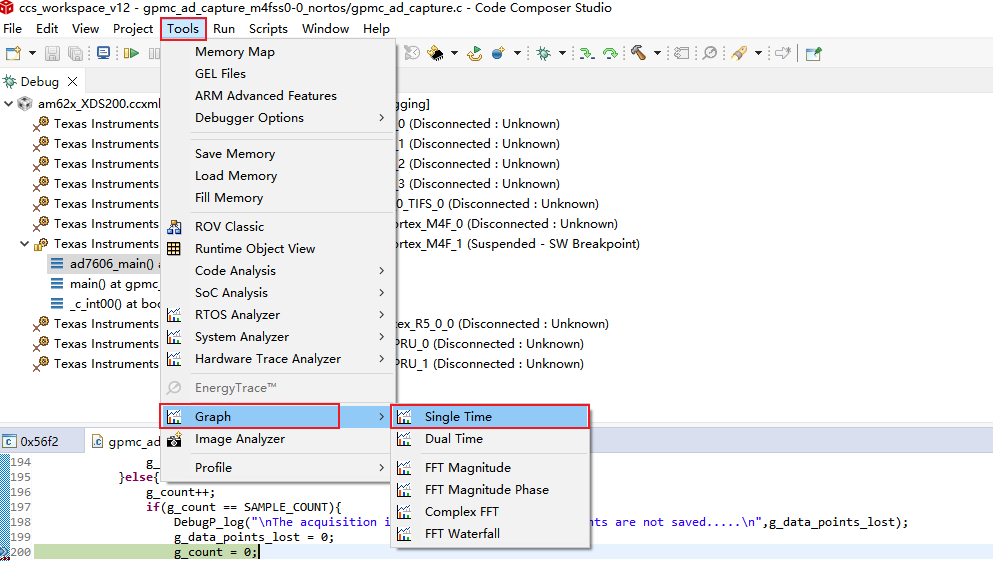

依次点击"Tools -> Graph -> Single Time"查看采集到的波形,以通道1为例进行演示。

图 7

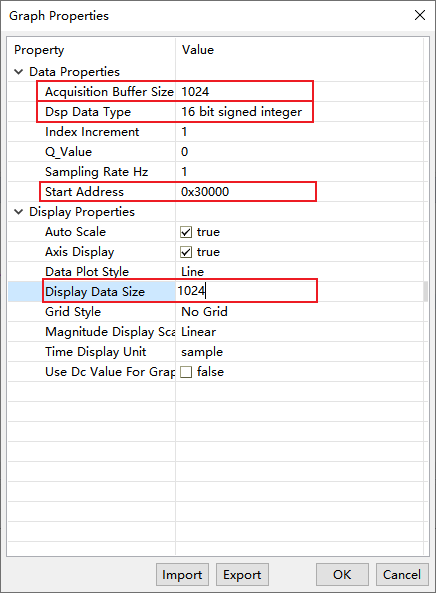

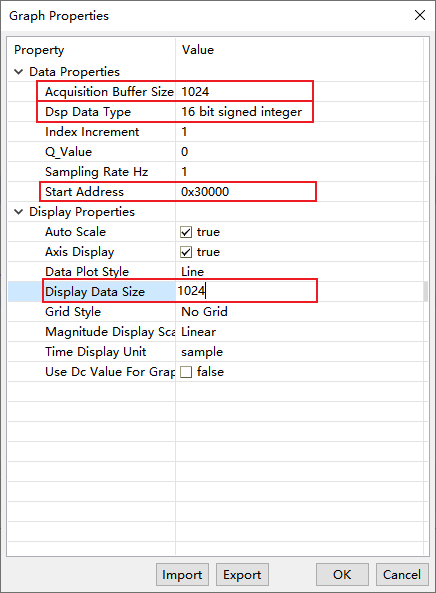

在弹出界面中按照下图内容进行配置,然后点击OK,即可查看AD信号的时域波形。

图 8

表 2

| Acquisition Buffer Size | 从Start Address开始读取的数据长度 |

| Dsp Data Type | 读取的数据类型 |

| Start Address | 从Start Addres开始读取数据 |

| Display Data Size | 显示的数据长度(即将多少个采样点的数据进行显示,该数值不能大于Acquisition Buffer Size) |

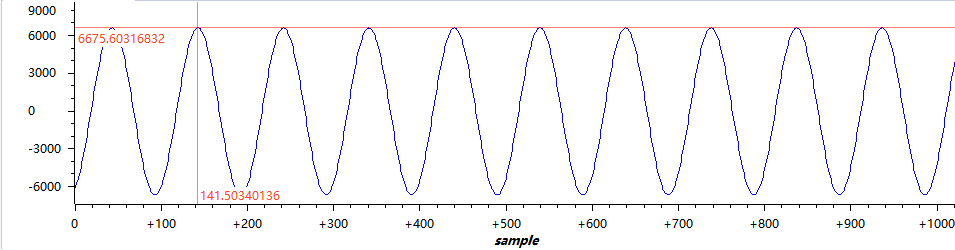

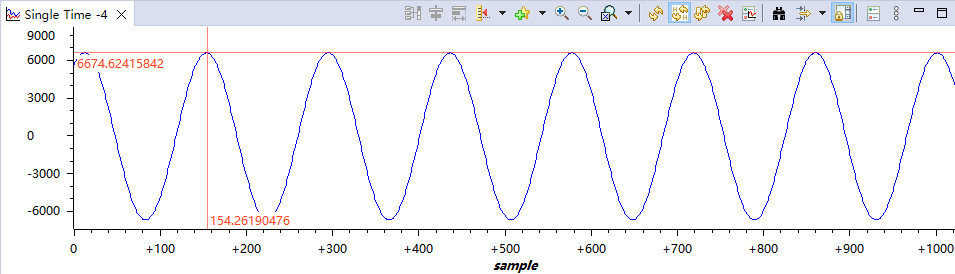

图 9

本次使用TL7606I-A1模块进行测试,在上图中可看到通道1的时域波形,波形的幅值约为6676。从CCS看到的波形值为AD芯片内部寄存器保存的数字量,从AD7606的芯片数据手册得到的换算公式均为:数字量 = 峰值 / 量程 x 32768,则AD信号实际幅值=数字量 x 量程 / 32768 = 6676 x 5V / 32768 = 1.02V,与信号发生器的1V标称值接近。

(2)单通道数据采集

程序运行后在CCS软件的控制台输出1个通道数据保存的首地址以及数据点保存结果。

图 10

依次点击"Tools -> Graph -> Single Time"查看采集到的波形。

图 11

在弹出界面中按照下图内容进行配置,然后点击OK,即可查看AD信号的时域波形。

图 12

图 13

本次使用TL7606I-A1模块进行测试,在上图中可看到通道1的时域波形,波形的幅值约为6675。从CCS看到的波形值为AD芯片内部寄存器保存的数字量,从AD7606的芯片数据手册得到的换算公式均为:数字量 = 峰值 / 量程 x 32768,则AD信号实际幅值=数字量 x 量程 / 32768 = 6675 x 5V / 32768 = 1.02V,与信号发生器的1V标称值接近。

审核编辑 黄宇

-

基于TI AM62x的Debian系统正式发布,丰富的软件生态,让您的应用开发更便利!2024-10-29 1839

-

AM62x Sitara™处理器数据表2024-08-03 763

-

GPMC并口多通道AD采集案例,基于TI AM62x四核处理器平台!2024-07-10 6999

-

没抢到?米尔AM62x开发板限量5折又来了2024-05-17 1563

-

AM62x基于GPMC的ARM+FPGA通信方案2023-09-25 2221

-

AM62x GPMC并口如何实现“小数据-低时延,大数据-高带宽”—ARM+FPGA低成本通信方案2023-08-17 1959

-

TI AM62x接替AM335x,米尔核心板开发板2023-08-08 2356

-

再续AM335x经典,米尔TI AM62x核心板上市,赋能新一代HMI2023-08-03 1468

-

专用M4F+四核A53,异构多核AM62x让工业控制“更实时、更安全”2023-06-15 5754

-

【正式发售】TI AM335x升级平台-AM62x,强势来袭!主频1.4GHz2023-05-04 1913

-

AM62x相比AM335x,到底升级了什么?2023-05-03 962

-

TI Sitara系列AM62x开发板(4核ARM)规格书2022-09-21 1258

-

搭载TI AM62x处理器,飞凌FET6254-C核心板震撼发布2022-06-24 2428

全部0条评论

快来发表一下你的评论吧 !