为空间飞行器量身打造:可自修复的空间电子系统设计

FPGA/ASIC技术

描述

设计摘要:

空间飞行 器的电子系 统设计面 临着一些 问题。首先 ,太空飞行器执行任 务时会经历复 杂的空间环 境,包括 温度数百度 的巨变, 很强的电磁 干扰和宇 宙高能粒子辐射 等。这对可 靠性提出 了很高的要 求。第二 ,深空探测 的航天器 的目标离地通常 较远,飞行 时间越来 越长,甚至 长达数年 。迫切需要 航天器的 硬件系统能够升级更新,实现功能扩展。第三,空间电子系统本身复杂 度越来越高,当 系统出现故障时,需要进行自主修复功能。

我们计划采用 Xilinx 的 Virtex FPGA 实现一个能解决以 上问题的空间电子系 统。利用 部分可重配 置特性实 现系统的远 程更新, 并利用可重 构计算加 上加速 航天器姿 态确定,姿 态轨道控 制等算法的 运算。当 系统受到高 能粒子轰 击,发生单粒子事件翻转故障时,利用 FPGA 的配置回读特性实现故 障检测与自我修复。

系统原理及技术特点

2.1 系统原理

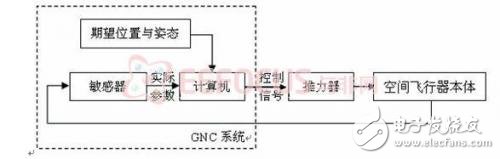

在本项目中,我 们以空间飞行器导航、制导与控制(GNC)系统 为具体实现对象,来设计 可自修复空 间电子系 统。导航、 制导与控 制系统在飞 行器中的 作用和工作原理如下图所示。

图表 1 导航制导与控制系统工作原理

首先,空间飞行器的 GNC 系统从地面站或导航算法得到执 行本次任务的期望位置与姿态信息。接着,GNC 系统通过飞行器上转载的敏感 元件获得飞行器本体目前真 实的轨道位 置与姿态 信息。敏感 元件包括 陀螺、加速 度计、星 敏感器、红外地平敏感 区等。这些信号 经过 AD 采用数字化、数字滤波、信号调理等处理后,经 过制导和控 制算法解 算,得到飞 行器推力 器控制信号 。由控制 信号驱动推力器 的开关为飞 行器的航 行或姿态调 整提供合 适的力或力 矩。当这 些力和力矩作用 于空间飞行 器本体上 时,其轨道 位置和姿 态会发生改 变。而位 置和姿态的改变 立即被敏感 元件测量 到,从形成 一个闭环 的控制系统 ,到 达期望的控制结果。

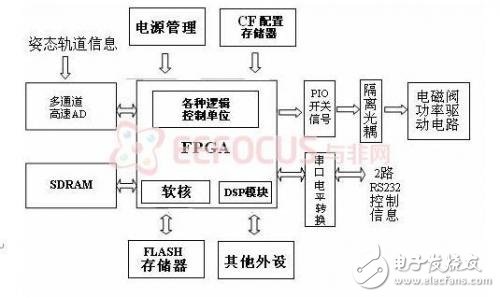

图表 2 GNC 系统硬件实现组件框图

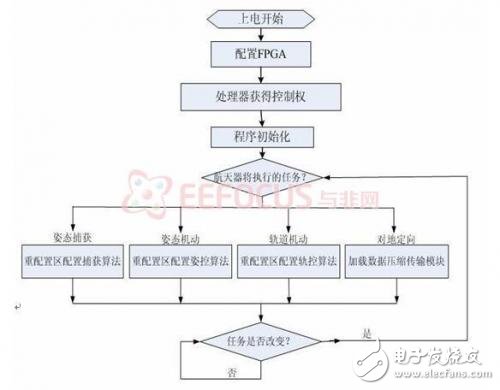

2.2 可重构加速计算

在空间飞 行器不同的 时间阶段 要执行不 同的任务算 法。比如 ,当飞行器 刚刚到达预定 轨道时,首 先要执行 姿态确定任 务,主要 算法有扩展 卡尔曼滤 波算法等。之后 要进行姿态 调整控制 ,执行姿态 控制算法 。再运行轨 道导航制 导算法等等。可以看出在不 同的任务阶段,执行的算 法是不同的。对此,我们在 FPGA内部规划了 2 块独立的部分可重配置区域,在不同的任务阶段, 对其配置合适的算法硬件加速模块,从而大大提供系统的运 算性能。由于部分重配置时,FPGA的其他区域 任然正常的 工作运行 ,从而可以 在不同任 务阶段平滑 的切换硬 件算法模块,而不会对整个系统的运行造成中断。FPGA 内部规划架构图如 下。

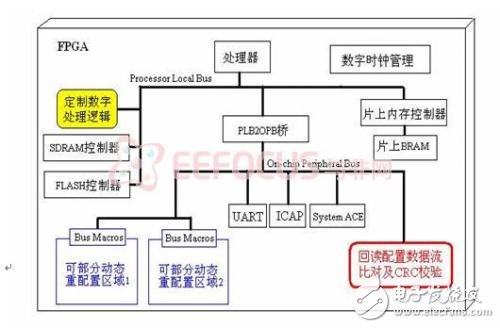

图表 3 FPGA 片上系统组件架构图

部分重配置设计流程

第一步:用 HDL 描述设计并综合计可以用 VHDL 或 Verilog 语言描述,任何一种 ISE 支持的 综合工具都可 以用来综 合。在综合 时,必须 把其设置为 在不同的 设计层次间 没有优化 。另外 应该禁止 I/O 插入以防止 I/O buffers 插入到低层模块中。每个 部分重配置区域的模块都必须分别综合。

第二步:设置设计的约束

为布局布线设置约束。除了时序约束外( PERIOD,etc)还必须设置 AREAGROUP, AREA GROUP RANGE, MODE 和 LOC 约束。

第三步:实现非部分重配置区域的设计

第四步:时序/布局分析

第五步:实现基础设计

第六步:实现各个重配置模块

第七步:融合顶层,基础及部分配置模块设计,并生成最 终的配置 bit 文件在两个部 分重配置区 域中,我 们将在不 同的任务阶 段根据其 算法特点配 置不同的算法 硬件加速模 块。在航 天器姿态轨 道控制系 统中要实现 对系统参 数的估计,最常用的技术 就是基于扩展卡尔曼滤波(EKF)技术的姿态确定算法。该方法 除了可以 估计航天器 的姿态参 数外,还可 以估计矢 量观测中的 一些不确 定性参 数。因此,该方法能够获得很高的姿态确定精 度。

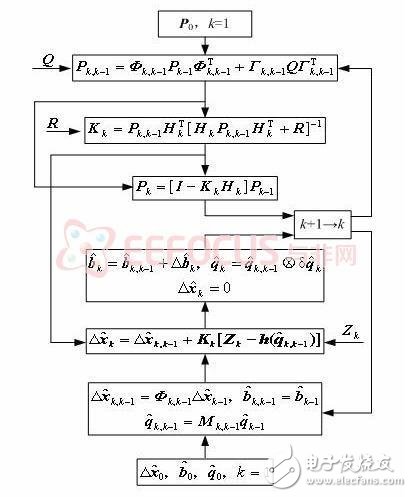

图表 4 卡尔曼滤波算法流程

其中,姿态四元 数q=[q13 q4]T=[q1 q2 q3 q4],其 中q13 为矢量部分,q4 为标 量部分。u(t)为三个陀螺的测量输出值 ,ω(t)为沿三个陀螺输入轴的真实姿态角 速率,b(t)为三个 陀螺的常值漂移,d(t)为三个陀螺的相关漂移,n1 为三个陀螺 的测量白噪声,且n1 的三个分量服从N(0,σgi ),(i=x,y,z)。我 们将把此算法用HDL语言编制 成硬件并行 执行模块。当航 天器当前任 务阶段需要执 行此算法时,将其加载入部分重构模块。为此,我 们将在航天 器姿态确 定任务阶 段时,在其 中一个可 重配置区域 载入其算法硬件加速模块。其工作流程图如下:

图表 5 算法部分重配置工作流程图

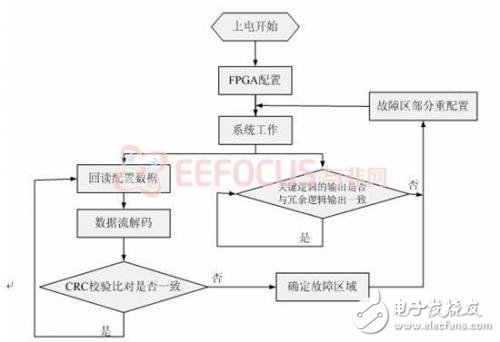

2.3 硬件故障检测与修复

在太空中 恶劣的环境 下,电子 系统在高 能带电粒子 的轰击下 很能会发生 状态翻转,导 致功能出错 ,甚至发 生致命的控 制错误。 为此,我们 设计模块 来回读 FPGA 中的配置数据 并进行 CRC 校验,发现数据错误后重新配置出错区域 ,及 时修复系统。

Virtex 系列 FPGA 系列包含了一个叫做回读的特性。它最 初是设计来方便芯 片生产时的测试。它提供了一种非侵入式的 读取 FPGA 中的每 个锁存器和配置 存储器状态的方法。要利用这个特性,需要在 设计中例化回读组件。这个功能实在后台运行的,不会影响 FPGA 的运行性能。FPGA 的设计可以 全速运行而同时运行回读功能。

在所有的读出的比特之上会产生一个 CRC 校验和,并把这个 校验和插入到回读序列流 的末尾。这 个校验和 通过和当前 配置下期 望的校验和 比对。如 果不匹配,一个 SEU 很可能就发生了。

我们将设计控制逻辑来运行和获取回读。 这个过程需要执行下面的步骤:

1,开始回读:把 RT 置高并保持住直 到回读结束。

2,从回读的开始到结束都不能打断 CLOCK。CLOCK 信号必须 在 1Mhz

和 2Mhz 之间。

3,把回读数据输入一个 6 位的解码器,以便 寻找数据头《111110》。

4,当字头被找到时,开始计数时钟周期,当达到前面表 格所示的计数值时,

接下来就是一个 0,接着就是 11bit 的 CRC。

5,把这个 CRC 与期望的 CRC 比对。

图表 6 故障检测与修复流程图

-

电子系统中电源如何搞定EMI电磁干扰2023-03-24 1519

-

电气与电子系统实验指导书2008-09-24 3769

-

电子系统设计实例PDF格式2009-09-25 35849

-

四轴飞行器的结构原理2016-01-15 6476

-

电子系统仿真与MATLAB2016-05-04 5311

-

FPGA在车载电子系统的应用2019-07-25 3357

-

汽车电子系统面临的状况2020-06-24 3305

-

电源 IC 应用在汽车电子系统有什么样的要求?2021-03-06 1868

-

如何利用FPGA设计航空电子系统?2021-05-06 1950

-

天线的发展及其对电子系统的影响是什么?2021-05-27 1832

-

航空电子系统检测2018-02-06 1064

-

如何使用MATLAB进行的自修复飞控系统的仿真2018-11-05 1488

-

汽车电子常见的电子系统盘点分析2018-12-24 7146

-

如何减少电子系统的电磁干扰?2023-09-18 2429

-

30%空间压缩奇迹:组合泵如何重塑飞行器动力系统布局逻辑2025-09-25 534

全部0条评论

快来发表一下你的评论吧 !