GaN FET与硅FET的比较

功率器件

描述

功率GaN落后于RF GaN的主要原因在于需要花时间执行数个供货商所使用的成本缩减策略。最知名的就是改用6英寸的硅基板,以及更低成本的塑料封装。对于电源设计人员来说,理解GaN有可能带来的性能提升,以及某些会随时间影响到最终产品性能的退化机制很重要。

联合电子设备工程委员会 (JEDEC) 针对硅器件的认证标准经证明是产品使用寿命的很好预测指标,不过目前还没有针对GaN的同等标准。要使用全新的技术来减轻风险,比较谨慎的做法是看一看特定的用例,以及新技术在应用方面的环境限制,并且建立能够针对环境变化进行应力测试和监视的原型机。对于大量原型机的实时监视会提出一些有意思的挑战,特别是在GaN器件电压接近1000V,并且dv/dts大于200V/ns时更是如此。

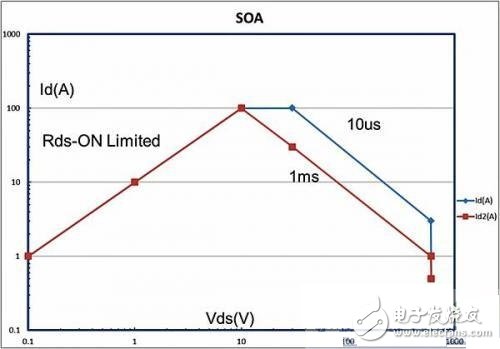

一个经常用来确定功率FET是否能够满足目标应用要求的图表是安全工作区域 (SOA) 曲线。图1中显示了一个示例。

图1:GaN FET SOA曲线示例,此时Rds-On =毫欧

硬开关设计

功率GaN FET被用在硬开关和数MHz的谐振设计中。上面展示的零电压 (ZVS) 或者零电流 (ZCS) 拓扑为数千瓦。SOA曲线的应力最大的区域是右上角的电压和电流最高的区域。在这个硬开关区域内运行一个功率GaN FET会导致由数个机制而造成的应力增加。最容易理解的就是热应力。例如,在使用一个电感开关测试电路时,有可能使器件从关闭时的电流几乎为零、汲取电压为几百伏,切换到接通时的电流几乎瞬时达到10A。

器件上的电压乘以流经的电流可以获得瞬时功率耗散,对于这个示例来说,在转换中期可以达到500W以上。对于尺寸为5mm x 2mm的典型功率GaN器件,这个值可以达到每mm2 50W。所以用户也就无需对SOA曲线显示的这个区域只支持短脉冲这一点而感到惊讶了。由于器件的热限值和封装的原因,SOA曲线的右上部被看成是一个脉宽的函数。由于曲线中所见的热时间常数,更短的脉冲会导致更少的散热。增强型封装技术可被用来将结至环境的热阻从大约15°C/W减小到1.2°C/W。由于减少了器件散热,这一方法可以扩大SOA。

SOA曲线

TI有一个系列的标准占板面积的功率MOSFET、 DualCool? 和NexFETs?。这些MOSFET通过它们封装顶部和底部散热,并且能够提供比传统占板面积封装高50%的电流。这使得设计人员能够灵活地使用更高电流,而又无需增加终端设备尺寸。与硅FET相比,GaN FET的一个巨大优势就是可以实现的极短开关时间。此外,减少的电容值和可以忽略不计的Qrr使得开关损耗低很多。在器件开关时,电压乘以电流所得值的整数部分是器件必须消耗的功率。更低的损耗意味着更低的器件温度和更大的SOA。

SOA曲线所圈出的另外一个重要区域受到Rds-On的限制。在这个区域内,器件上的电压就是流经器件的电流乘以导通电阻。在图1所示的SOA曲线示例中,Rds-On为100毫欧。硅MOSFET的温度取决于它们的Rds-On,这一点众所周知。在器件温度从25oC升高至大约100oC时,它们的Rds-On几乎会加倍。

动态Rds-On

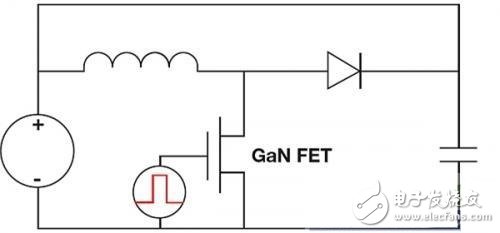

GaN FET具有一个复杂的Rds-On,它是温度,以及电压和时间的函数。GaN FET的Rds-On对电压和时间的函数依赖性被称为动态Rds-On。为了预测一个GaN器件针对目标使用的运行方式,很有必要监视这些动态Rds- On所带来的影响。与SOA曲线的温度引入应力相类似,电感硬开关应力电路比较适合于监视Rds-On。这是因为很多潜在的器件退化是与高频开关和电场相关的。

图2是一个简单开关电路,这个电路中给出了一种在SOA右上象限内实现循环电流,并对器件施加应力的方法。

图2:电感硬开关测试电路

宽带隙

GaN 是一种宽带隙材料,与硅材料的1.12eV的带隙相比,它的带隙达到3.4eV。这个宽带隙使得器件在被击穿前,能够支持比同样大小的硅器件高很多的电场。某些器件设计人员常用来帮助确定器件可靠性的测试有高温反向偏置 (HTRB)、高温栅极偏置 (HTGB) 和经时电介质击穿 (TDDB)。这些都是静态测试,虽然在验证器件设计有效性方面是好方法,但是在高频开关动态效应占主导地位时,就不能代表典型使用情况。高温工作寿命 (HTOL) 是器件开关过程中的动态测试。特定的工作条件由制造商确定,但是这些工作条件通常处于某些标称频率、电压和电流下。

早期对于 GaN针对RF放大器的使用研究发现了一个性能退化效应,此时器件能够传送的最大电流被减少为漏极电压偏置的函数。这个随电压变化的(捕获引入)效应被称为“电流崩塌”。在缓冲器和顶层捕获的负电荷导致电流崩塌或动态Rds-On增加。在施加高压时,电荷可被捕获,并且在器件接通时也许无法立即消散。已经采用了几个器件设计技巧(电场板)来减少大多数灵敏GaN FET区域中的电场强度。电场板已经表现出能够最大限度地减小RF GaN FET和开关功率GaN FET中的这种影响。

GaN是一种压电材料。GaN器件设计人员通过添加一个晶格稍微不匹配的AIGaN缓冲层来利用这个压电效应。这样做增加了器件的应力,从而导致由自发和压电效应引起的极化场。这个二维电子气 (2DEG) 通道就是这个极化场的产物。具有2DEG通道的器件被称为高电子迁移晶体管 (HEMT)。不幸的是,在器件运行时,高外加电场也会导致有害的压电应力,从而导致另外一种形式的可能的器件退化。对于诸如GaN的新技术来说,拥有一个证明可靠性的综合性方法很重要。如需了解与TI计划相关的进一步细节,请参考Sandeep Bahl的白皮书,一个限定GaN产品的综合方法。

为了降低成本,功率GaN目前采用的是6英寸硅基板。由于硅和GaN晶格不匹配,会出现线程脱位。这会导致晶格缺陷,并增加捕获的可能性。这些捕获的影响取决于它们的数量和在器件中的位置。捕获状态,占据或非占据,也是施加的电场和时间的一个函数。捕获充放电可能在最短100ns到最长数分钟的时间范围分布。最接近栅极区域的捕获充电和放电会调制器件的转导。所有这些效应是GaN FET的Rds-On的复杂电压和时间相关性的基础。在限定期间,工程师通常在延长的期间内对器件施加DC应力,并且定期移除这一应力,以描述单个半导体测试的情况。移除器件电压偏置,即使只有几秒钟的时间,也可以实现某些捕获放电,这样的话,就不会影响到与实际运行相关的动态Rds-On值了。

总结

与硅FET相比,功率GaN FET具有很多优势,比如说更低的开关损耗和更高的频率切换能力。更高的开关频率可被用来增加系统的电源转换密度。要限定一个正在使用功率GaN FET的系统,设计人员应该了解可能的退化源,并随时监视它们在温度变化时的影响。一个监视动态Rds-ON增加的简单方法就是测量时间和电压变化过程中的转换过程的效率。为了更好地了解损耗出现的位置,系统被设计成能够实时监视漏极、栅极、源极和器件电流波形。此系统能够通过它们的SOA,以1MHz以上的频率,在电压高达1000V和电流高达15A时,硬开关FET。

捕捉和分析实时波形可以帮助我们更好地理解高频效应,比如说 dv/dt、栅极驱动器电感和电路板布局布线,这些在基于GaN的设计中都很关键。监视时间和温度范围内趋势变化的实时信息能够为我们提供更好的GaN FET退化信息,并使我们对于更加智能器件和控制器产品的需求有深入的理解。

-

用UCC27611搭建的驱动GaN FET电路,FET的Drain极加电时,UCC27611输出端检测到干扰波,为什么?2024-12-20 453

-

GaN-FET的关键参数和驱动要求2024-09-12 415

-

集成FET与外部FET:电机驱动器的性能比较2024-09-10 667

-

安世推出支持低压和高压应用的E-mode GAN FET GAN FET2023-08-10 1776

-

支持低压和高压应用的E-mode GAN FET2023-05-30 1481

-

MOSFET 和 GaN FET 应用手册-Nexperia_document_bo...2023-02-17 1407

-

Gan FET:为何选择共源共栅2023-02-09 1153

-

GaN FET如何实现下一代工业电源设计2022-11-07 686

-

48V电源系统中的GaN FET应用2022-07-26 2289

-

GaN FET在应用中的可靠性2022-07-18 1491

-

利用开发板实现对eGaN FET电源设计的评估2019-01-24 3842

-

GaN FET重新定义电源电路设计2017-05-03 5138

全部0条评论

快来发表一下你的评论吧 !