Cortex R52内核Cache的具体操作(2)

描述

本节内容主要讲述CortexR52内核Cache的具体操作包括使缓存无效(invalidate)操作,清除(clean)缓存。有的时候客户可能需要对cache做一些清理,比如invalidate,clean等操作。虽然目前在cortex R52内核很少需要操作cache,但是本节依然给一些操作指导和实践,以备以后不时之须。

Cache Line缓存行的概念

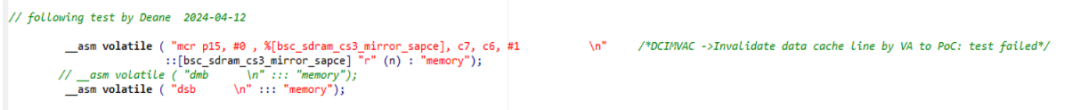

操作cache相关指令需要通过汇编代码来操作,也都是以缓存行(Cache Line)为单位来进行操作。CortexR52缓存行的长度是64字节,比如下面的invalidate指令:

点击可查看大图

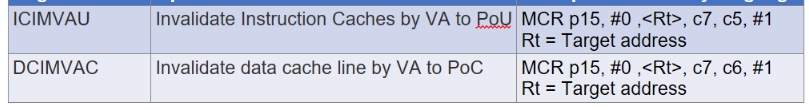

指令的解释如下:

点击可查看大图

1__asm volatile

这表示这是一段内联汇编代码,并且使用volatile关键字告诉编译器不要对这段代码做优化。

2"mcr p15, #0, %[bsc_sdram_cs3_mirror_space], c7, c6, #1 "

这是ARM处理器的指令。mcr是一个协处理器数据操作指令,用于向协处理器(如CP15)中的特定寄存器写入数据。在这里,它将数据写入到CP15寄存器中。p15, #0: 指定了协处理器的编号,这里表示CP15。

3%[bsc_sdram_cs3_mirror_space] "r" (n)

这里使用了内联汇编中的替换字符串(substitution strings),%[bsc_sdram_cs3_mirror_space] 用于指定一个替换占位符,它将在后面的 :: 部分中提供实际的值。"r" (n) 则表示使用寄存器(register)约束,这意味着n是一个变量。通常情况下,使用 "i" 约束表示将一个立即数直接嵌入到汇编指令中,而不是从变量中加载。但在你的代码中,你想要从一个变量中加载一个值传递给汇编指令。因此,你应该使用 "r" 约束来表示将一个寄存器中的值传递给汇编指令,而不是使用 "i"。

4:: 和 : "memory"

这两个部分是内联汇编的修饰符。:: 表示没有输出寄存器,"memory" 则表示该内联汇编代码可能会对内存进行读写操作,因此编译器需要考虑到内存屏障(memory barrier)的影响。

以RZT2M为例对cache作一些操作

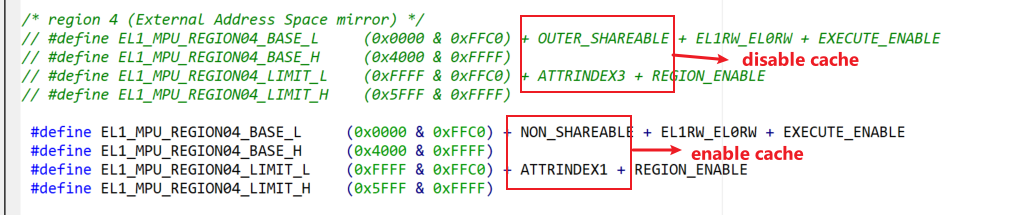

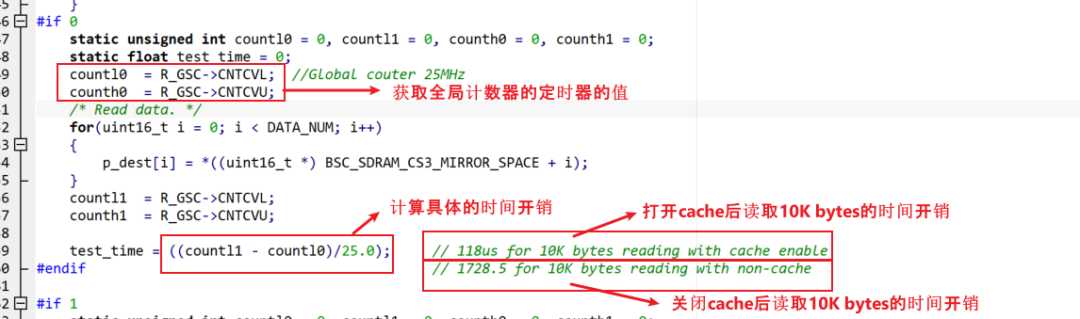

1以rzt2m读取SDRAM为例,做一个打开和关闭cache的性能比较

SDRAM在代码中如果使用external Address sapce mirror的地址空间,那么开启和关闭cache的配置如下图所示:

点击可查看大图

点击可查看大图

从上图可以看出关闭cache后读取数据的时间是打开cache后时间开销的十多倍。所以cache是否使能,性能差别十分显著。

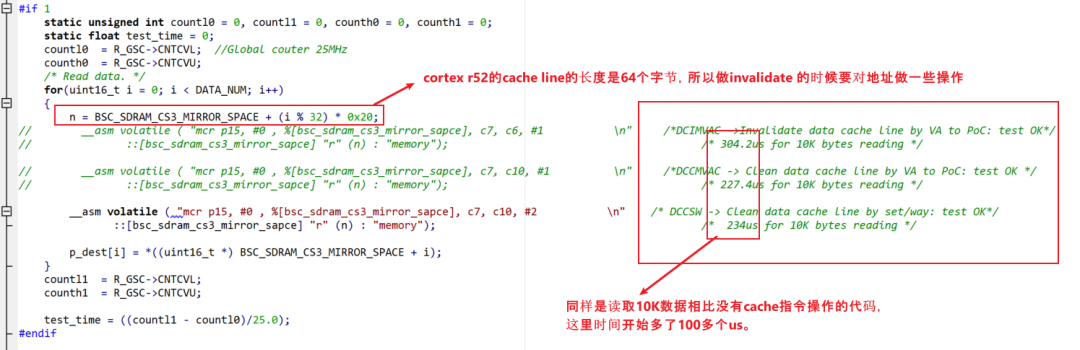

2如果同样是读取10K bytes的数据,加上一起对cache invalidate/clean的操作之后,时间开销如下

点击可查看大图

上面的代码每读取sdram一次,都有对cache做操作。所以时间开销增加了很多,但是实际情况,是否需要频繁的操作cache需要看实际情况而定。注意每次对cache的操作都是以,cache line的长度(64字节)对cache做处理的。比如invalidate某段sdram地址对应的cache, 0x58000000-0x58000040, 那么对这段地址的invalidate操作是:

左右滑动查看完整内容

__asm volatile ( "mcr p15, #0 , %[bsc_sdram_cs3_mirror_sapce], c7, c6, #1 " /*DCIMVAC ->Invalidate data cache line by VA to PoC: test OK*/ ::[bsc_sdram_cs3_mirror_sapce] "i" (0x58000000) : "memory");

注意代码中 "i" 与 "r" 的区别,在上文中已经有提到。

注意对cache的操作需要十分慎重,并且充分验证的情况下进行。

-

请问UART内核在接收数据时有哪些具体操作?2025-12-26 121

-

请问UART内核在接收数据时有哪些具体操作?UART内核在接收数据完成后会进行哪些处理?2025-12-25 129

-

CortexR52内核Cache的具体操作2024-07-15 2915

-

威纶通触摸屏远程上下载程序需要什么工具?具体操作步骤是什么?2024-01-17 9364

-

差分探头的使用具体操作步骤2023-04-03 6342

-

PCB电镀工艺流程及具体操作方法2023-02-07 10482

-

Allegro打过孔的具体操作步骤2022-10-17 9361

-

使用CH340来下载烧录或调试的具体操作步骤有哪些2022-02-24 3963

-

AssistiveTouch的辅助功能锁定屏幕如何具体操作呢2021-12-31 1733

-

移植Miracl库的具体操作步骤2021-12-21 1940

-

看门狗定时器的具体操作2021-11-10 1179

-

求ATmega168看门狗复位的具体操作过程?2020-11-18 1342

-

Protel在线教程:如何在PCB中给PCB补泪滴的具体操作2010-04-22 8214

全部0条评论

快来发表一下你的评论吧 !