如何实现DXF结构格式文件自动识别生成板框

描述

前言

随着科技的不断进步和创新,PCB(印刷电路板)行业正经历着前所未有的高速发展。PCB作为电子设备中不可或缺的基础组件,其重要性日益凸显。现代电子产品对性能和尺寸的要求不断提高,推动了PCB设计和制造技术的持续创新。

PCB的形状已从传统的平面矩形发展到多维立体结构,以适应更紧凑、更复杂的电子系统需求。这些形状的多样化和复杂化,不仅提高了电子产品的性能和可靠性,也极大地丰富了PCB的应用领域。从消费电子到航空航天,从医疗设备再到汽车电子,PCB的身影无处不在。随着新材料、新工艺的不断涌现,PCB的未来发展前景广阔,它将继续扮演着连接现代世界的关键角色。Genesis支持自动识别导入的DXF结构格式,在复杂的结构图中自动识别DXF文件的边界,直接转换成板框,可以帮设计工程师节省时间,缩短了设计的周期。

Genesis平台简介

芯和半导体Genesis是面向封装和PCB板级系统设计的软件平台。它基于“仿真驱动设计”理念,集成芯和自有仿真能力在设计前-中-后不同流程的协同分析,提前将系统电路、电磁,电源和热仿真等问题识别和解决在设计初期,实现系统设计与仿真一体化解决方案,提高产品研发效率。

Genesis自动识别DXF

形成板框流程介绍

1.导入DXF格式结构文件

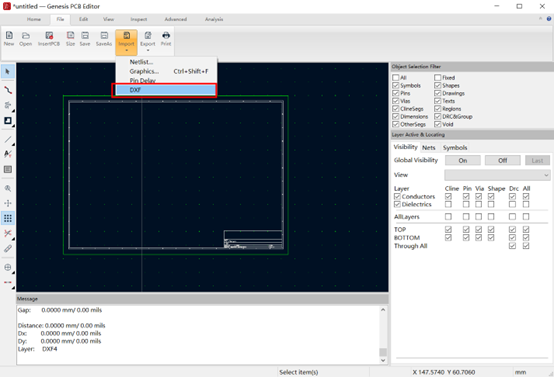

首先,打开Genesis,点击菜单栏中的File->Import->DXF,如图1所示。

图 1

导入DXF命令菜单

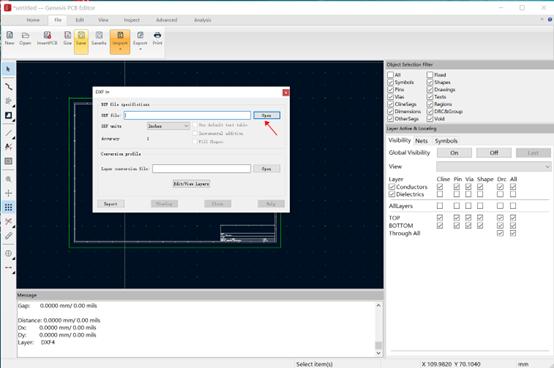

接着,弹出“DXF in”界面,在弹出的窗口File处选择需要导入的DXF文件,如图2所示。

图 2

选择导入的DXF

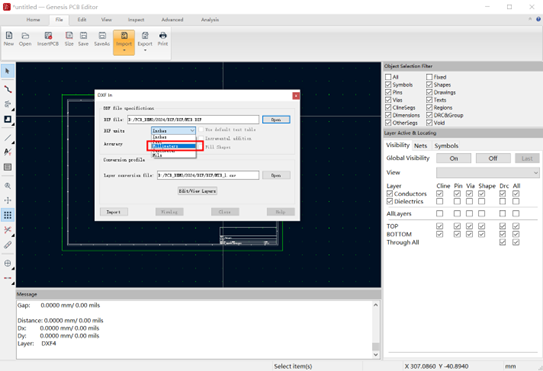

在设置界面“DXF units”位置,设置默认导入的单位,此处选择MM,导入的单位需和结构软件导出的单位保持一致,如图3所示。

图 3

设置导入默认单位

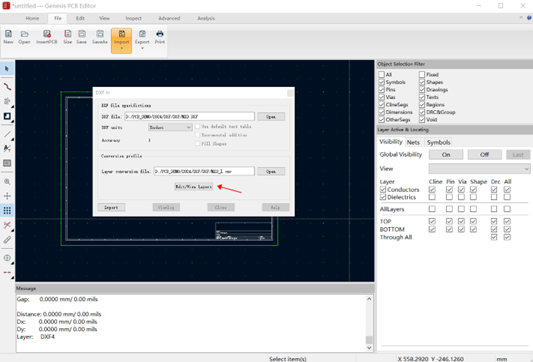

接着,在“DXF in”界面,点击“Edit/View Layers”,设置DXF所要导入的层,如图4所示。备注:此处的层可以是自定义层,也可以是任意层,转换成板框之后,可以删除该层导进来的数据。

图 4

设置导入的DXF对应的层

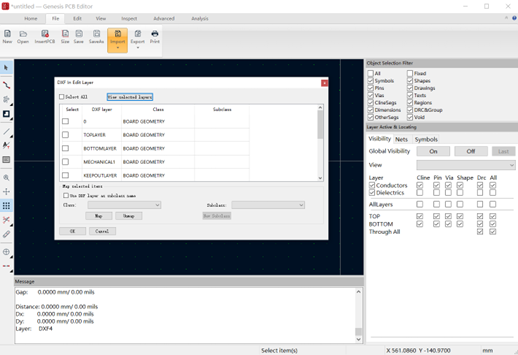

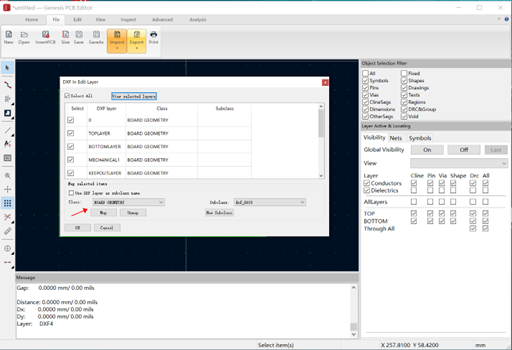

点击完“Edit/View Layers”之后,软件弹出Dxf in Edit Layer界面,如图5所示。

图 5

Dxf in Edit Layer界面

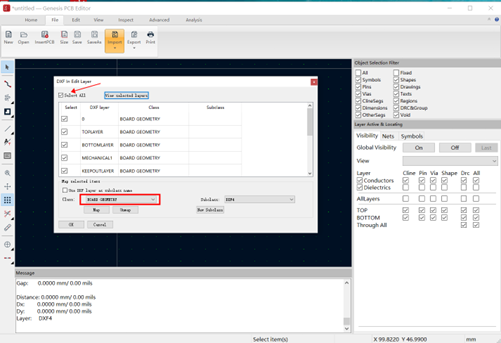

在如下界面,在界面Select All位置点击,Select All位置此时被选中勾上;在Class位置,点击右侧的三角箭头,选择BOARD GEOMETRY,如图6所示。

图 6

设置导入的Class层

在DXF in Edit界面,点击“New Subclass“,软件会弹出来“New SubClass”界面,如图7所示。

图 7

新建Subclass

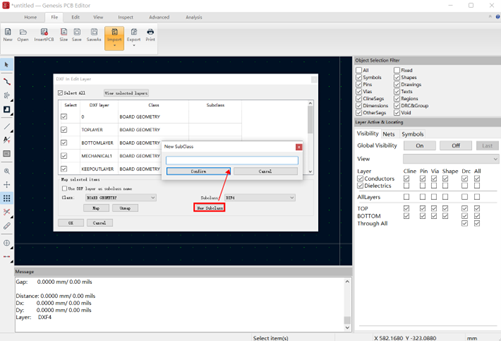

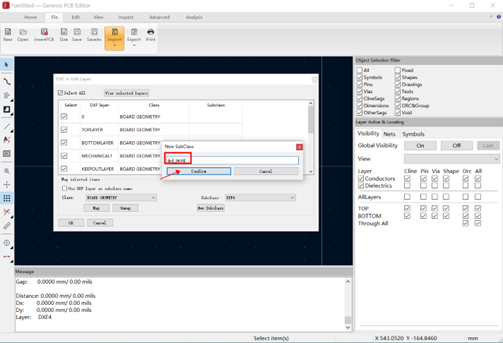

在弹出Subclass界面,输入放置DXF的Subclass层的名称,例如:DXF_0625,注意:输入的名称就是对应的Subclass的层的名称,然后点击“confirm”,如图8所示。

图 8

输入新建Subclass层名称

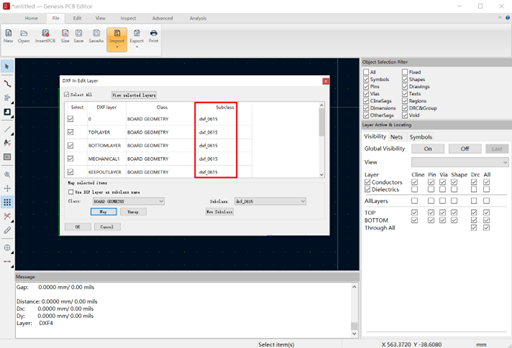

Subclass命名界面关闭后,继续点击DXF in Edit Layer界面下方的“map“,此时软件会自动map好subclass层,继续点击OK关闭界面,如图9、图10所示。

图 9

点击OK关闭DXF in Edit Layer界面

图 10

map完成的subclass界面

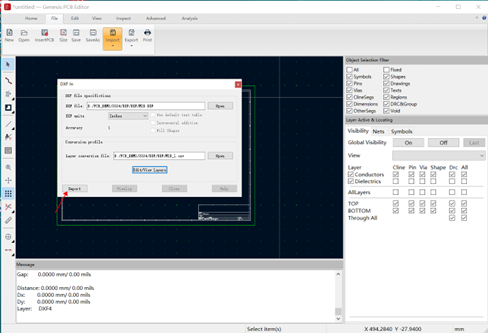

接着上一步骤,继续点击“Import”,如图11所示。

图 11

点击Import导入DXF

2.自动识别DXF边界,

形成闭合形状

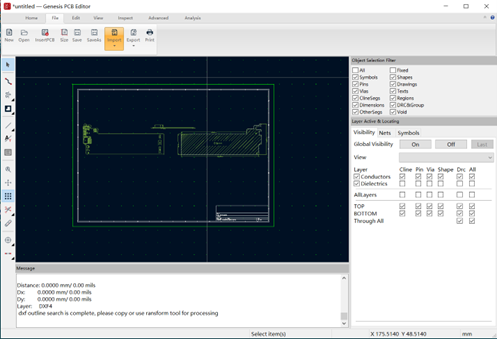

接着上一步,点击OK之后,导入的DXF文件会自动挂在鼠标上,可以通过鼠标点击在PCB layout里的需要放置的位置,备注:可以先放置任意位置,转换成板框后然后按照坐标位置精确放置,如图12所示。

图 12

放置导入的DXF的位置

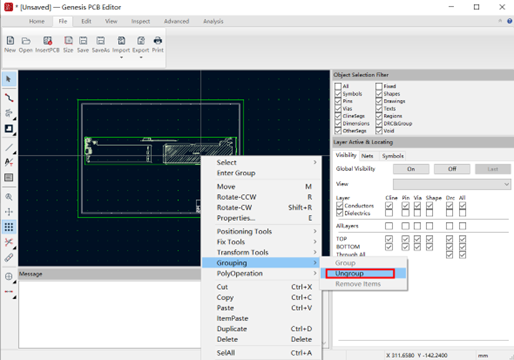

导入到layout里的DXF文件是以组的形式导入的,此时只能全部选中,不能单独选中其中的某以部分,选中导进来的DXF文件,然后鼠标右键:Grouping->Ungroup,如图13所示。

图 13

Ugroup导入DXF文件

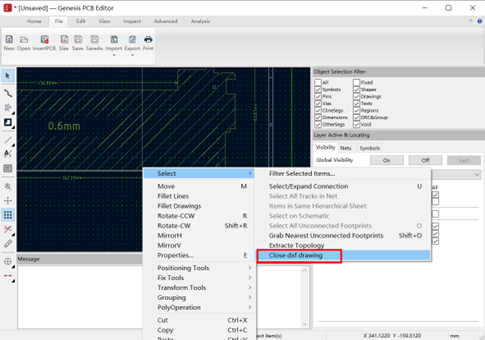

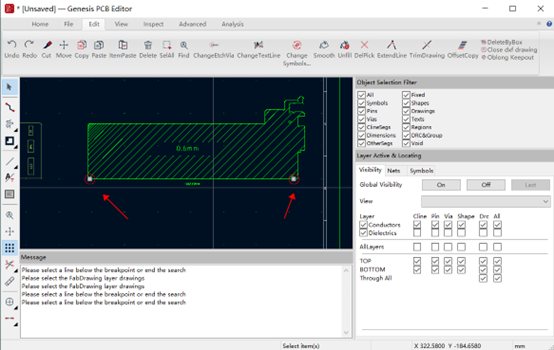

此时,导入进来的DXF文件都是单独的一段一段的不连续的线段,并不是完整的闭合的形状,接着选中是板宽外形上的任意一条线段,鼠标右键Select->Close dxf drawing,如图14所示。

图 14

选中线段鼠标右键

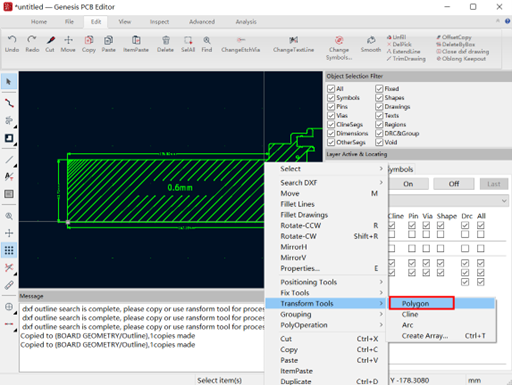

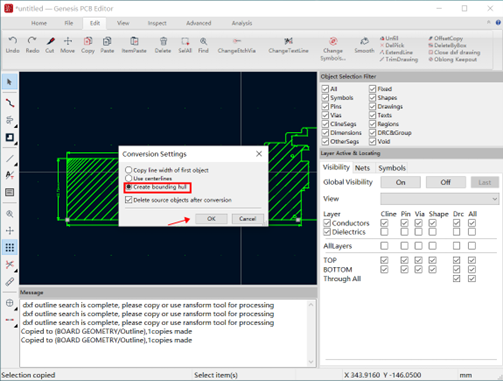

点击完Close dxf drawing命令之后,需要将属性改成对应板框属性,操作步骤如下:

1. 选中闭合形状的任意一条边,鼠标右键:Transform Tools->Polygon,如图15所示;

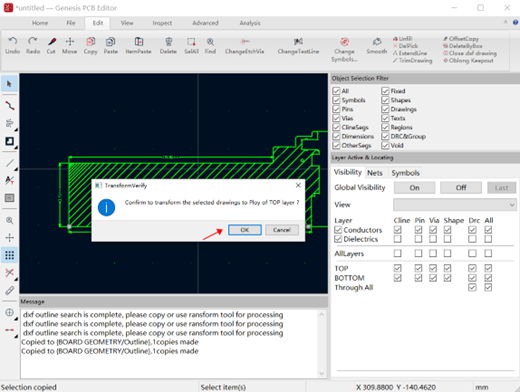

2. 软件自动弹出如图16提示界面,点击OK;

3. 此时跳出Conversion setting界面,选择“Create bounding hull”选项,点击OK,如图17所示。

图 15

转换成Polygon属性

图 16

点击OK

图 17

转换选项设置

3.将形成的闭合形状转换成板框,

放置到板框Outline层

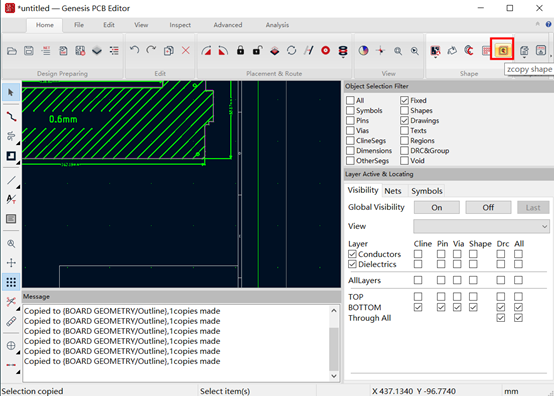

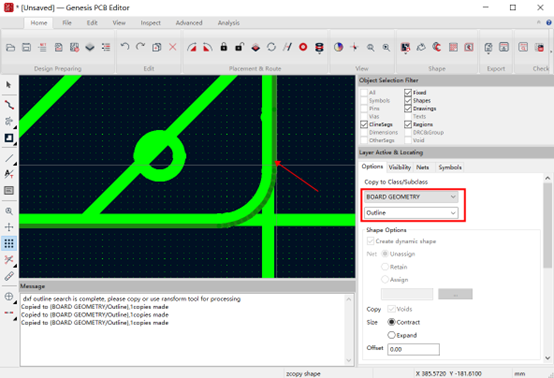

接着上一步,会生成一个板框属性的闭合形状的,当前默认是放置在Top层,需要使用Z-Copy命令复制到板框层即Outline:

1. 打开菜单Home-> Zcopyshape,点击激活Zcopy命令,如图18所示;

2. 在右边Option分别设置:将Class设置为BOARD GEMETRY,Subclass设置为Outline,然后放大显示界面,选中闭合的板框,如图19所示。

图 18

激活ZCOPY命令

图 19

Zcopy命令复制到Outline层

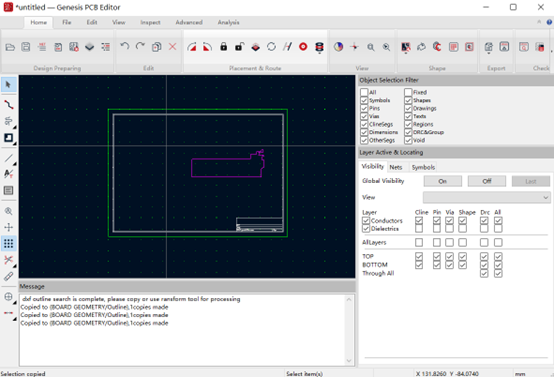

然后,将鼠标放置在空白区域鼠标右键Done结束命令,关闭其它层显示,只打开Outline层即可看到生成板框,也可以设置成不同颜色查看,如图20所示。

图 20

查看生成Outline

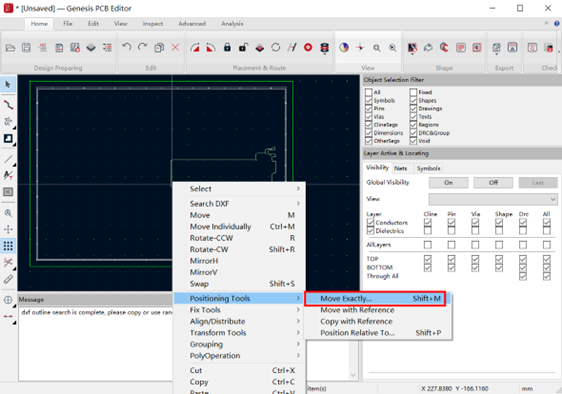

通常情况下,为了准确放置板框的位置准确性,我们放置板框会按照参考坐标来放置,可以选中DXF,鼠标放置在要Snap的点,按键盘快捷键M,然后DXF挂在鼠标上时,直接鼠标右键选择Special Tools->Move Exactly,如图21所示。

图 21

将选中图形转换大Outline层

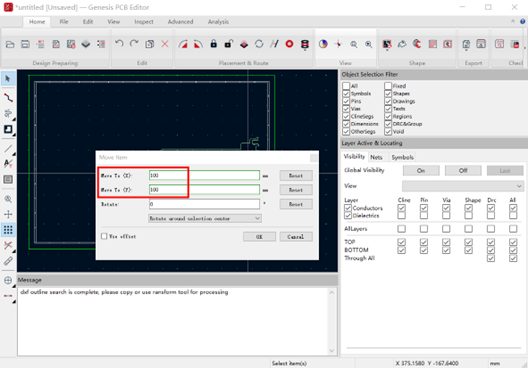

在弹出的界面里分别设置X和Y的坐标值,然后点击OK,即可完成自动按照坐标放置板框位置,如图22所示。

图 22

输入坐标

4.导入DXF断开场景,

可实现软件自动连接、闭合生成板框

在上面介绍的场景是在导入的DXF文件,线与线之间虽然不是完整闭合的线,但是线与线之间都是连接在一起的线,直接通过软件进行识别边界生成闭合板框即可;在设计中,我们也通常会遇到导入的DXF中间某几个线段之间没有完全连接在一起,有断开的小缺口,咱们也可以通过软件自动识别查找出断开的点,然后进行软件自动连接生成板框。

首先,软件会自动识别断开位置,步骤如下:

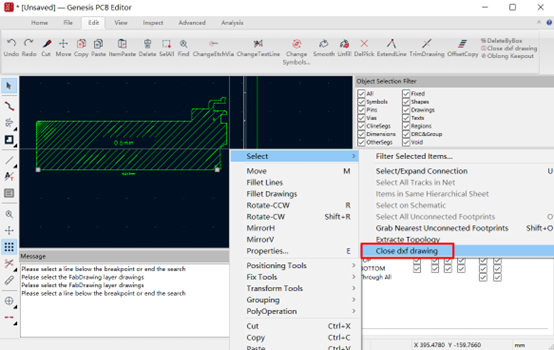

1. 导入DXF之后,选中要生成板框的任意一段线,鼠标右键:Select->Close dxf drawing,如图23所示;

2. 此时如果导入的DXF格式文件线与线之间有断开的点,软件会自动查找并显示红色的圈圈标处具体位置,如图24所示。

图 23

菜单执行Close dxf drawing命令

图 24

自动查找断开的点位置

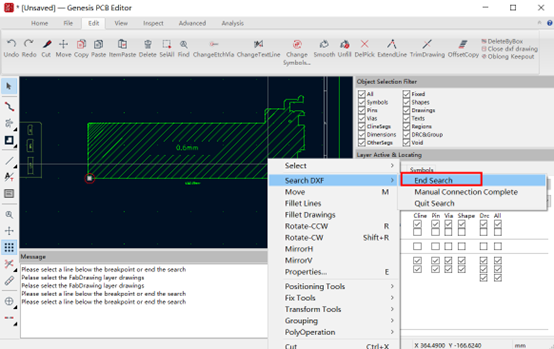

接着,根据断开线首尾相接的原则,交互式点击选中完整的板框Drawing线后,鼠标右键执行:Search DXF->End Search命令,如图25所示。

图 25

输入坐标

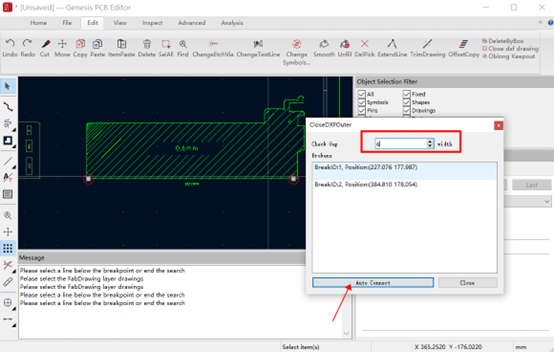

执行上一步命令,会弹出CloseDXFOuter命令界面,在Check Gap输入最大四倍线宽,倍数输入4,然后点击“Auto Connect:命令,软件进行自动连接点开的点,如图26所示;连接之后按照上面DXF无断开场景操作生成板框即可。

图26

输入Gap值自动连接

总结

本文主要介绍了如何在Genesis平台中对导入的DXF结构格式文件自动识别并形成板框的流程:针对复杂的DXF格式结构文件,从导入DXF格式文件到Genesis layout里层设置、单位设置、自动判断DXF是否断开点及位置、自动连接断开点、转换成板框属性,到通过鼠标右键命令软件自动识别成一个闭合形状图形,最后通过ZCOPY命令复制到对应的板框层,快速生成板框。

Genesis是面向封装和PCB板级系统设计的软件平台,支持自动识别导入的DXF结构格式文件,在复杂的结构图中自动识别DXF文件的边界,直接转换成板框,可以帮设计工程师节省时间,缩短设计的周期,提高设计效率。

关于芯和半导体EDA

芯和半导体提供“半导体全产业链仿真EDA解决方案”,是新一代智能电子产品中设计高频/高速电子组件的重要工具,拥有领先的2.5D/3D Chiplet先进封装设计分析全流程的EDA平台。产品涵盖三大领域::

芯片设计:匹配主流晶圆厂工艺节点,支持定制化PDK构建需求,内嵌丰富的片上器件模型,帮助用户快速精准地实现建模与寄生参数提取。

封装设计:集成多类封装库,提供通孔、走线和叠层的全栈电磁场仿真工具,为2.5D/3DIC先进封装打造领先的统一仿真平台,提高产品开发和优化效率。

系统设计:基于完全自主产权的EDA仿真平台,打通整机系统建模-设计-仿真-验证-测试的全流程,助力用户一站式解决高速高频系统中的信号完整性、电源完整性、热和应力等设计问题。

关于芯和半导体

芯和半导体是一家从事电子设计自动化(EDA)软件工具研发的高新技术企业,以仿真驱动设计,提供覆盖IC、封装到系统的具备完全自主知识产权的全产业链 EDA 解决方案,支持SoC先进工艺与Chiplet先进封装,致力于赋能和加速新一代高速高频智能电子产品的设计,已在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体创建于2010年,现已荣获国家级专精特新小巨人企业,上海市科技进步一等奖,运营及研发总部位于上海张江,在苏州、武汉、西安设有研发分中心,在美国硅谷、北京、深圳、成都、西安设有销售和技术支持部门。

-

在MDK中如何生成bin格式的文件2022-09-29 920

-

Cadence-Allegro导出dxf格式CAD文件2022-02-22 4923

-

PCB技术:PADS Layout如何导入DXF板框2020-10-20 19794

-

如何在MDk生成bin格式的文件2019-05-16 1375

-

如何打开heic格式文件2018-08-01 1153

-

Xilinx Vivado .coe格式文件生成步骤2018-07-10 21833

-

谁知道ALLEGEO软件如何把DXF文件弄成PCB板框结构2017-05-24 2810

-

AD从导入DXF文件,并转换成板框2015-01-08 15967

-

求助帖 labview自动识别2013-04-19 2629

-

CAD用到的各种格式文件 你都知道吗?2012-10-19 23312

-

如何打开eip文件,eip格式文件怎么打开2009-05-07 12196

-

orcad转pads格式文件的技术及实现方法2009-03-25 1210

-

DWG格式文件查看器2008-10-12 6080

-

tif格式文件用什么打开(如何打开怎么打开) tif是什么格2008-05-18 276057

全部0条评论

快来发表一下你的评论吧 !