DDR5内存条上的时钟走线

描述

DDR5标准JESD79-5文件中没有明确的控制阻抗建议,DDR4时代基本内存条上时钟阻抗还是跟着芯片、主板走的70-80欧姆。线宽相对而言比较细。不知道你开始使用DDR5没有,你有关注过DDR5内存条上的时钟走线吗?

DDR5内存条上Clock走线突然变粗了,阻抗只有50ohm。旁边细线就是地址控制信号,在DDR4上,时钟走线和地址信号粗细差不多,单根控制阻抗值也是差不多40欧姆的。

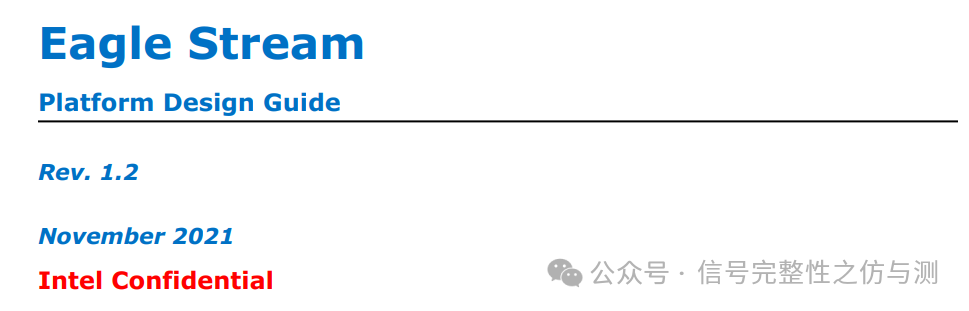

然而,我们看DDR5的平台,以Intel EGS为例,差不多两年前新出的DDR5要求,主板端Clock单根依旧是按照40欧姆,差分差不多75欧姆控制阻抗。

那为什么CPU、主板、甚至内存插槽走势按照75欧及以上的阻抗来控制,而内存条要控制50欧姆呢?而且,内存条本身就是一个很小的尺寸,空间够紧张了,还有把线宽调到8-9mil来控制差分50的阻抗,你想过原因吗?

这个问题也咨询过内存模组厂商,答复是按照高速传输线理论,DDR5信号电压更低、速率更高,使用更低的特征阻抗在信号时延和串扰方面会表现更好。

我有点疑惑,信号时延主要是跟走线长度和板材介电常数关系大。阻抗会影响吗?

下面一起来看看究竟是什么原因。

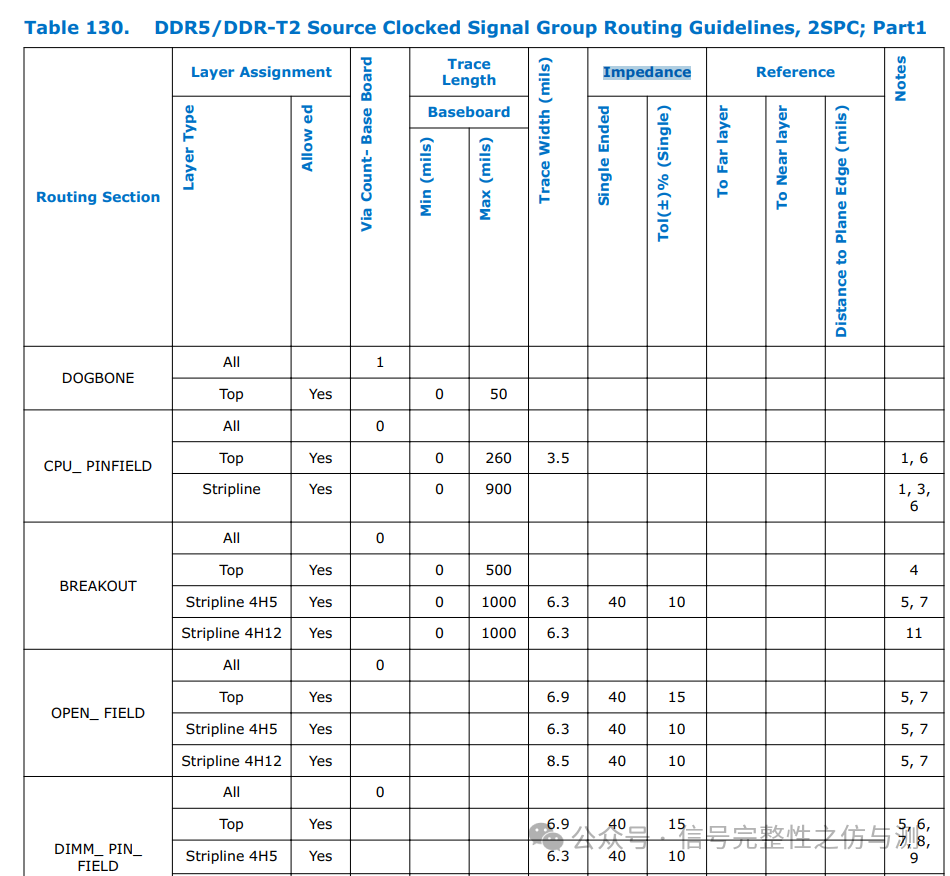

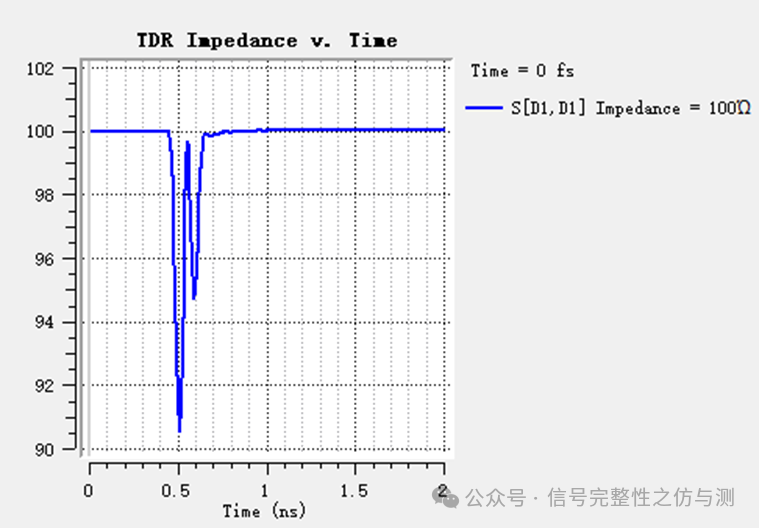

确认一下CPU的Package阻抗,通过TDR显示,确实是75Ω左右。

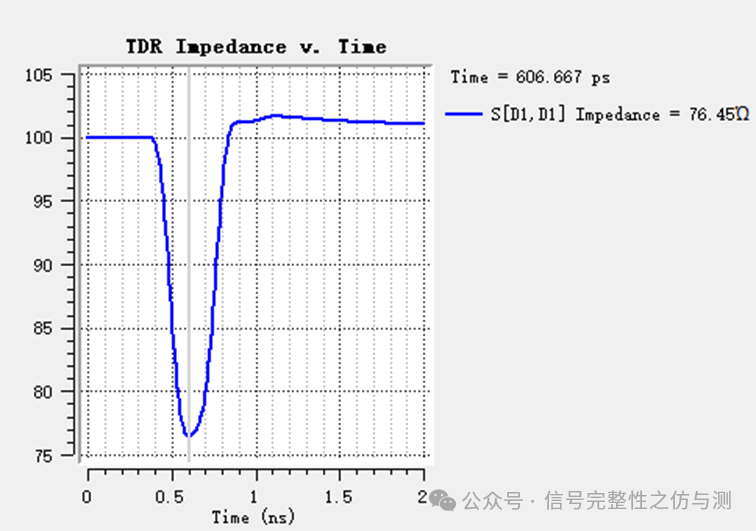

再看看主板走线的阻抗,主板阻抗值73-75ohm。

内存连接器呢?内存连接器的阻抗值是90-100ohm,这是SMT的,没有stub,连接器基本都是按照单根50欧姆来设计。

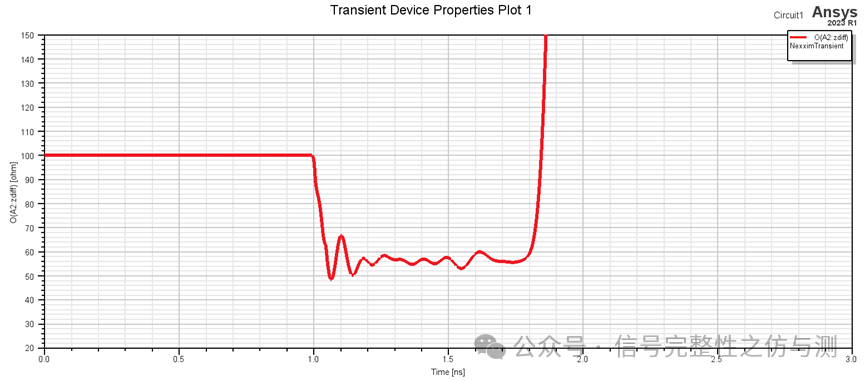

最后,看看内存条上走线的阻抗,内存条走线的阻抗值50-60ohm。

为什么要换软件?大家知道,内存条是多颗粒的,提取的S参数是一个多端口的,此时在ADS里面总是显示不正常,可能我没玩明白,但是Circuit看阻抗肯定是最优选择,那就不折腾了。

另外,我们还做了一个方案,假设内存条还是按照DDR4时代控制阻抗,会是什么结果。

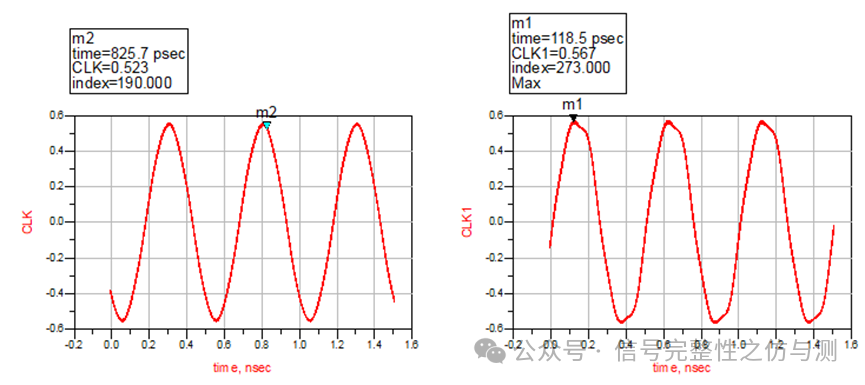

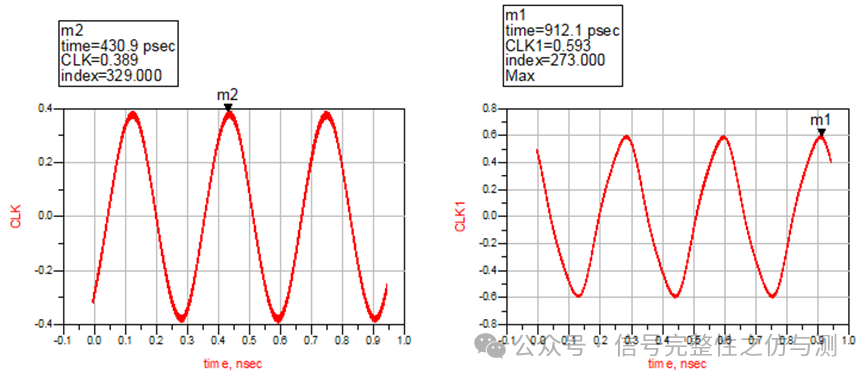

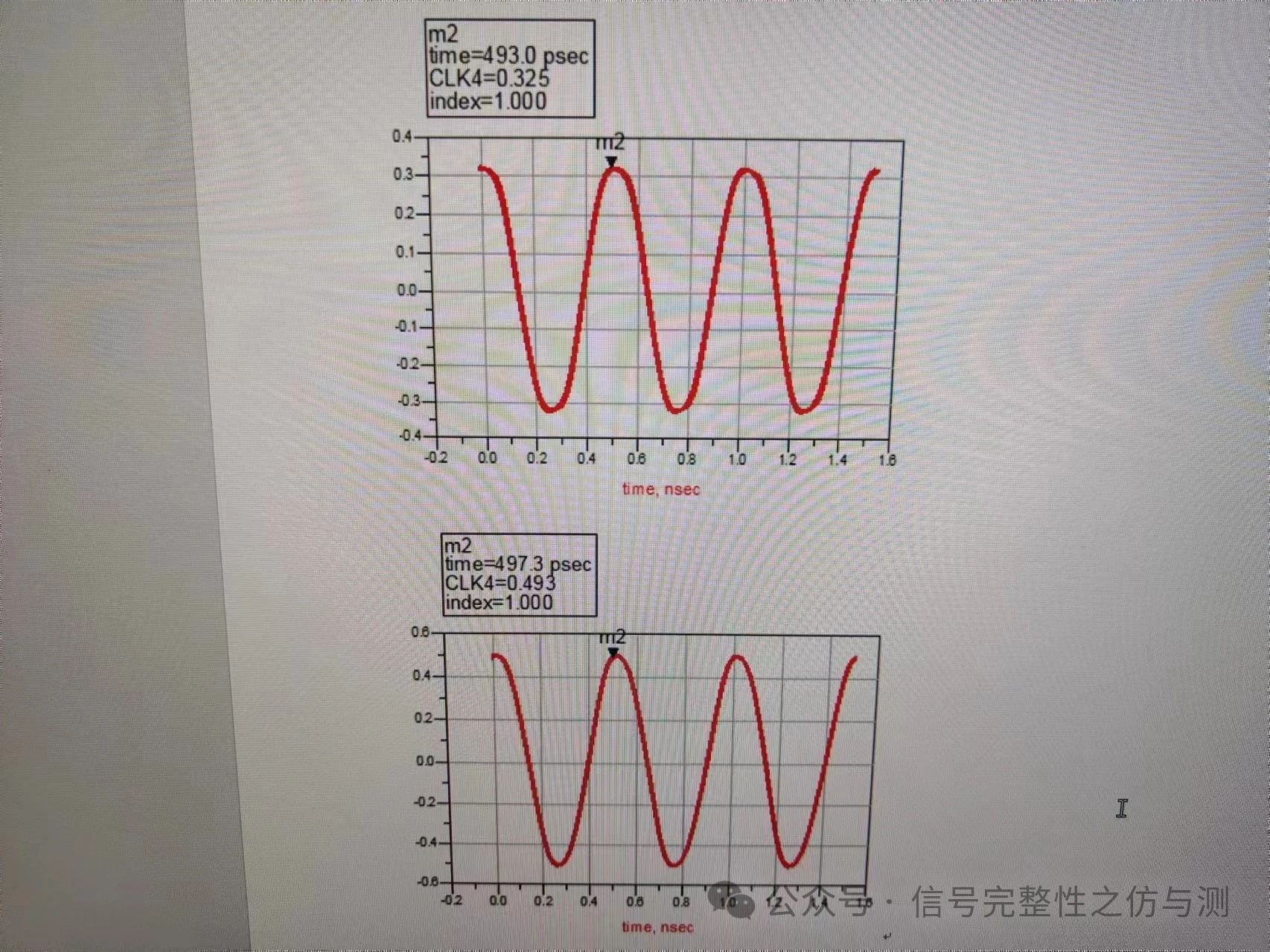

正常4-4.8Gbps的DDR5速率

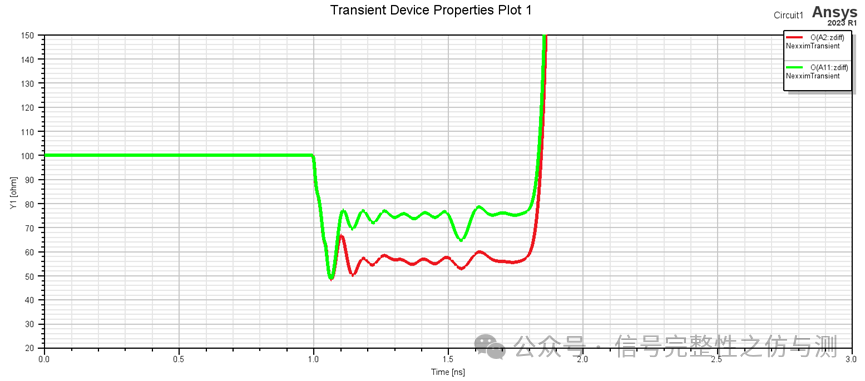

①主板阻抗75ohm,内存阻抗50ohm

②主板阻抗75ohm,内存阻抗75ohm

③主板阻抗50ohm,内存阻抗75ohm

④主板阻抗50ohm,内存阻抗50ohm

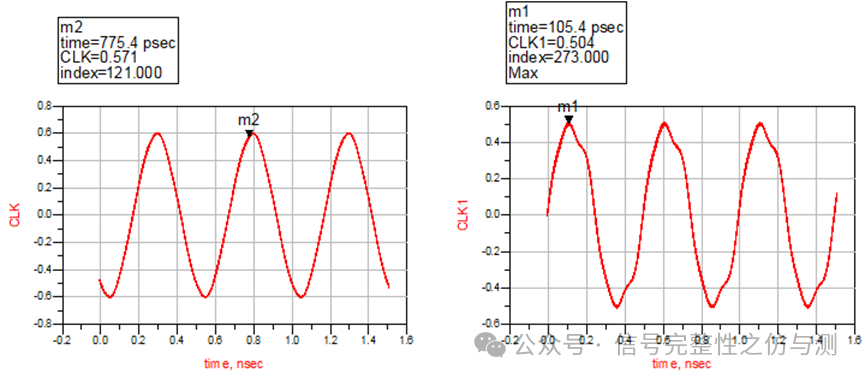

也就是说,在速率比较低时,DDR5的Clock阻抗要求比较宽松。就算与主板不匹配,也没有任何问题。

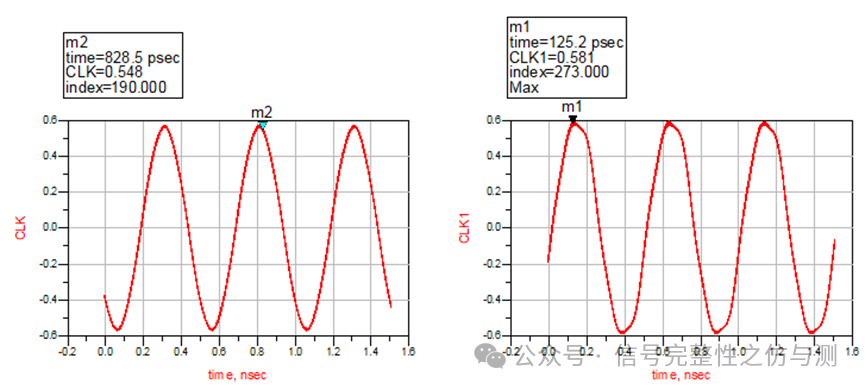

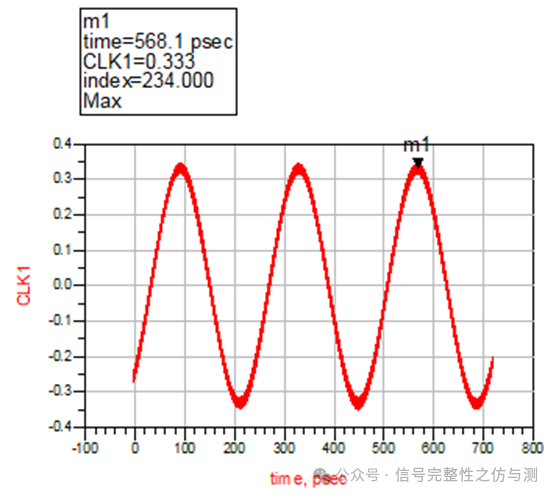

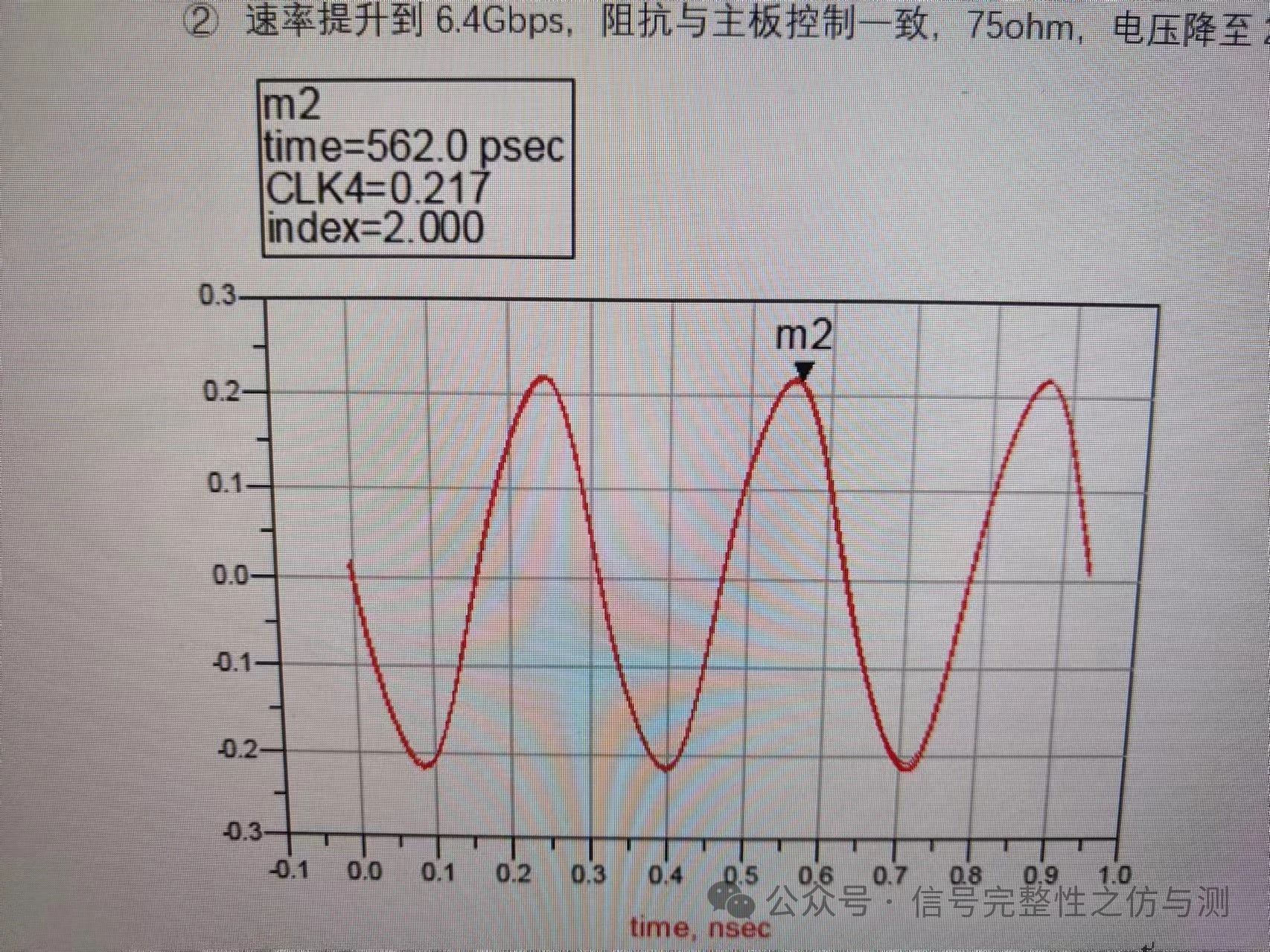

内存速率提升到6.4Gbps

如果内存阻抗使用与主板一致的75ohm,颗粒1的差分电压降至329mV

同等条件下,将内存阻抗降至50ohm,颗粒1和颗粒2电压均能抬升60mV。

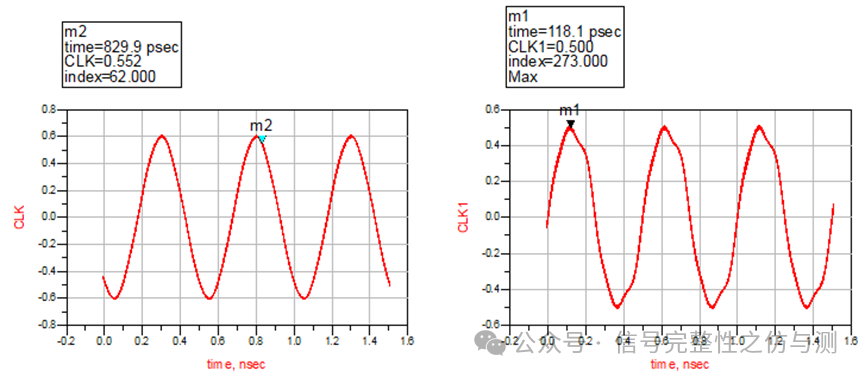

内存速率提升到8.4Gbps

颗粒1的差分电压降至333mV,比较临界。

同等条件下,将内存阻抗降至50ohm,同样电压有提升。

值得注意的是,对于UDIMM,这个设计是不适合8400速率的,这里只是借用这个走线验证不同阻抗对电压的影响。

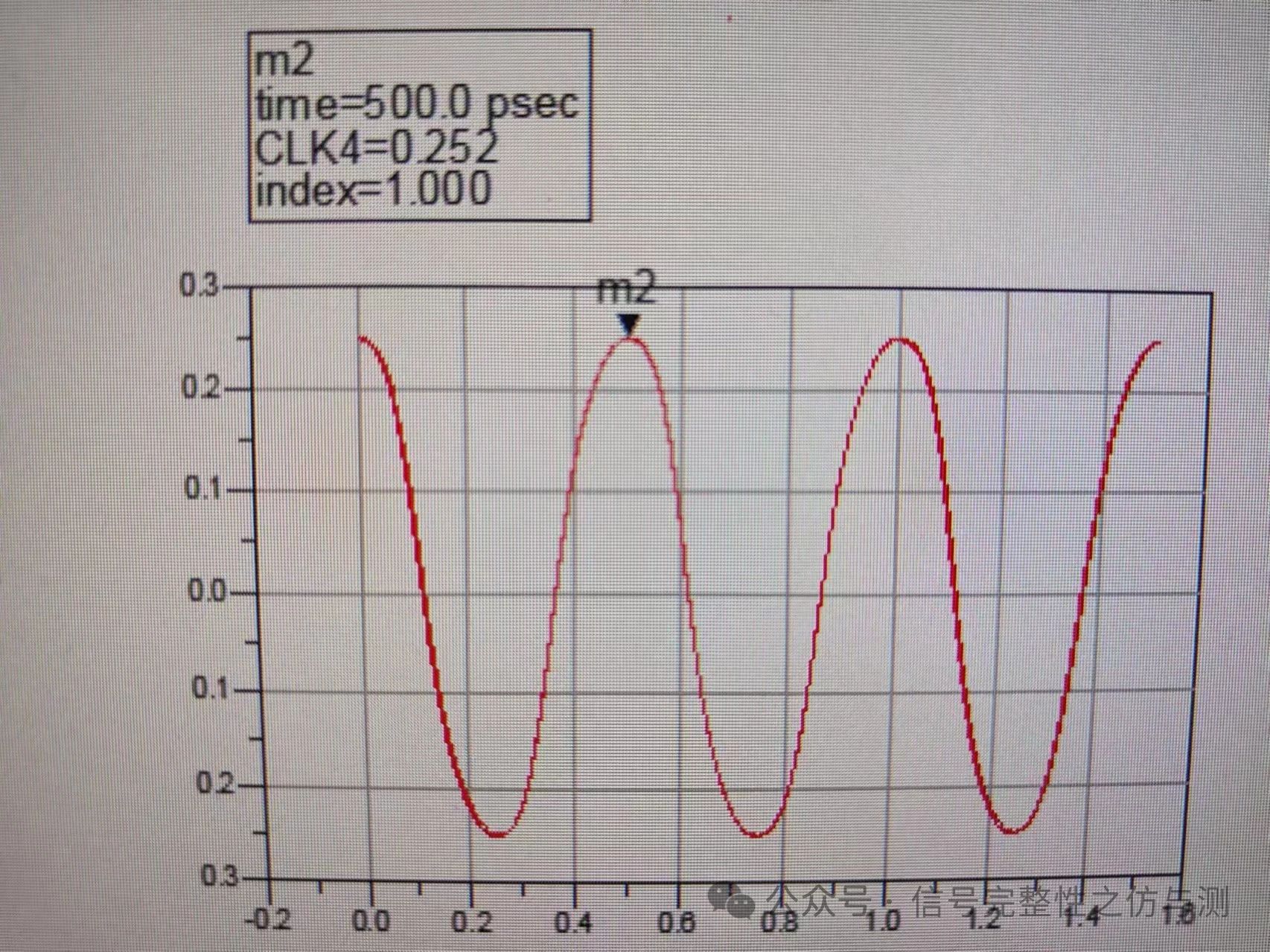

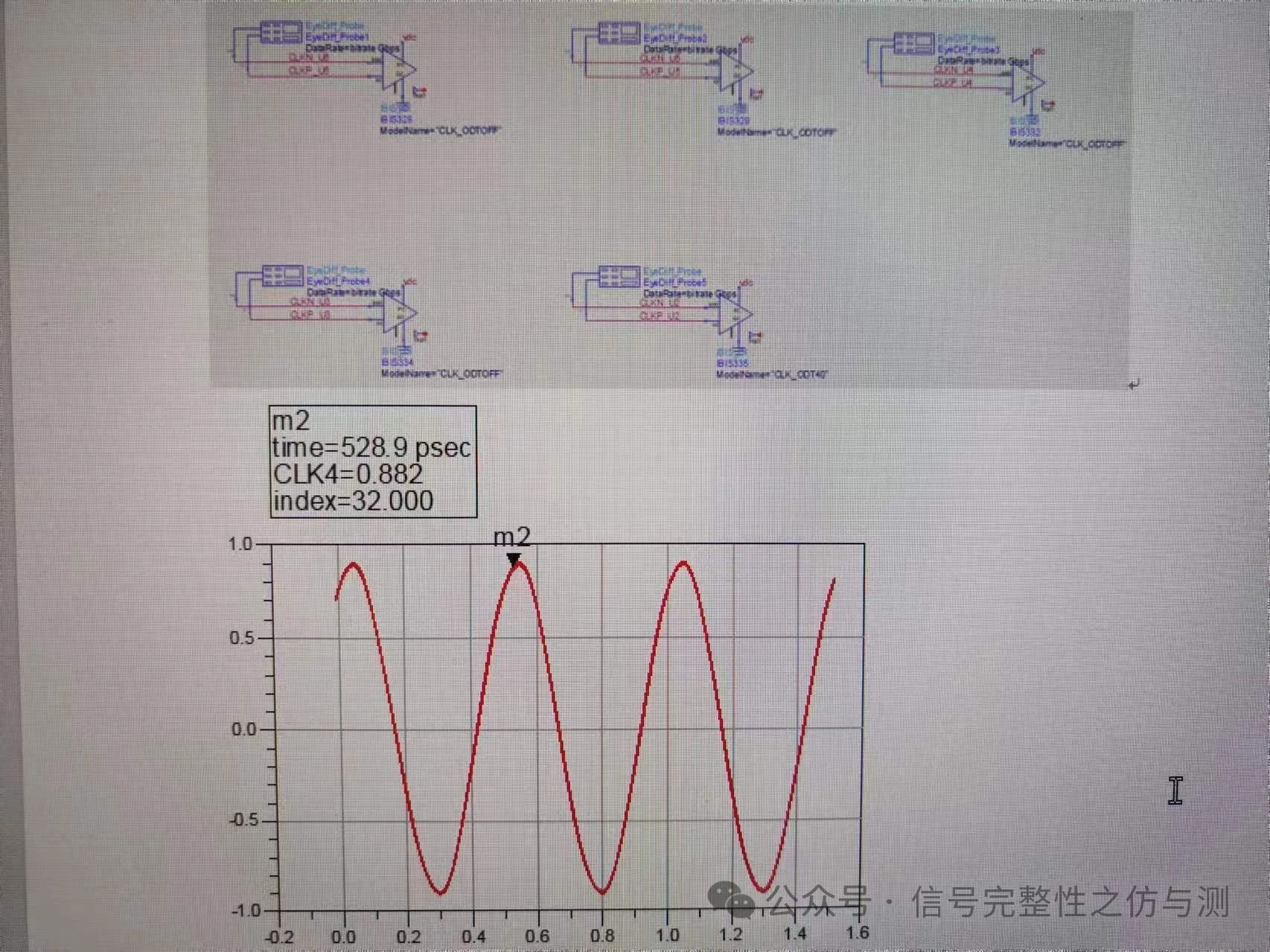

UDIMM如此,那RDIMM呢,RDIMM的时钟已经跟CPU、主板端没什么关系了,是由RCD芯片发出的。RCD出来后再经过5颗颗粒。

末端颗粒CLK电压只有252mV,显然不满足要求。

逐渐顺次关闭颗粒的ODT

只开最后一个颗粒ODT

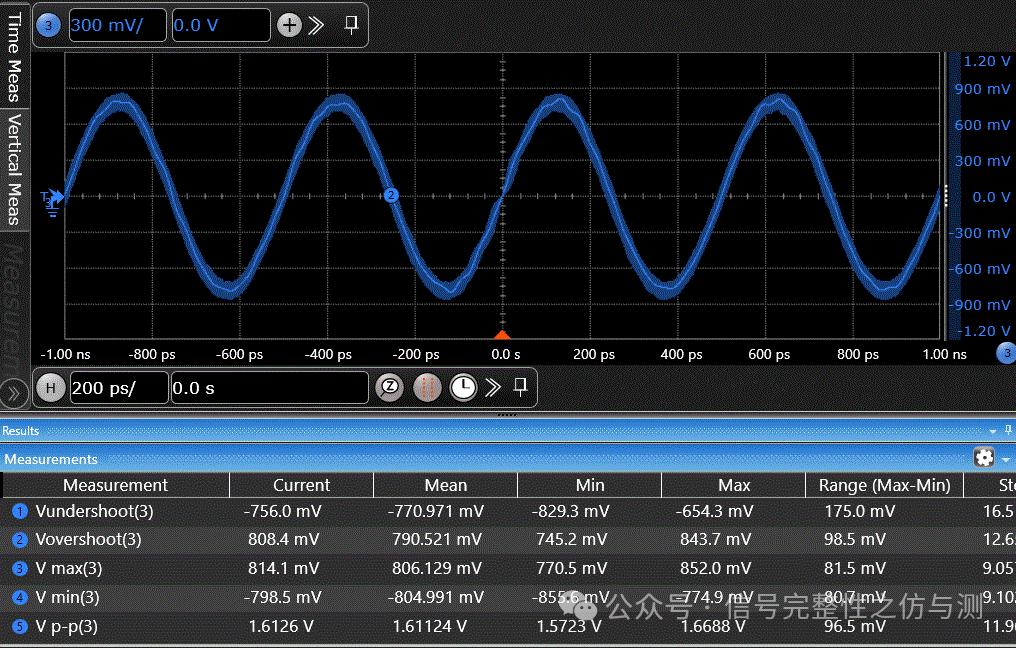

实际上在RDIMM上最后一个颗粒测试的max值也是800多mV,说明仿真设置是对的,后面按照这个配置来设置。

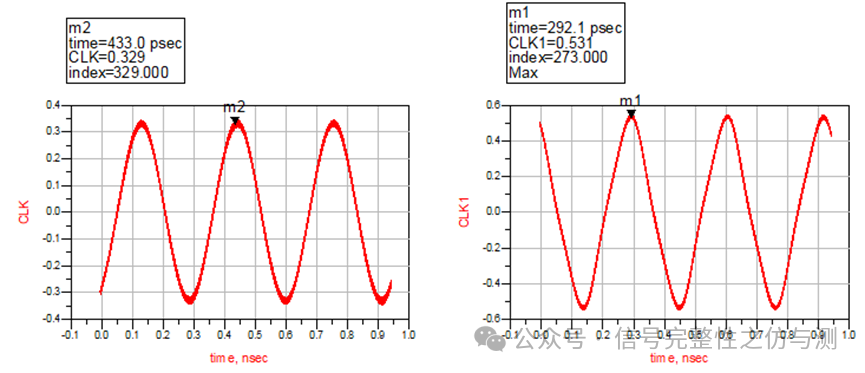

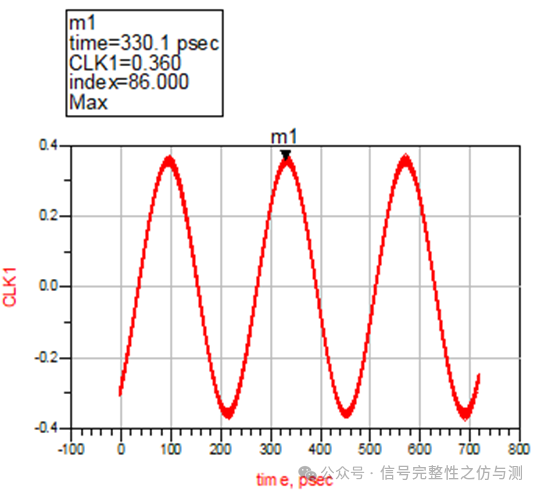

RDIMM内存速率提升到6.4Gbps

电压降至497mV

此时如果阻抗与主板控制一致,75Ω,电压降至217mV

速率恢复以前,内存阻抗与主板控制一致,75Ω

电压值也完全恢复了。

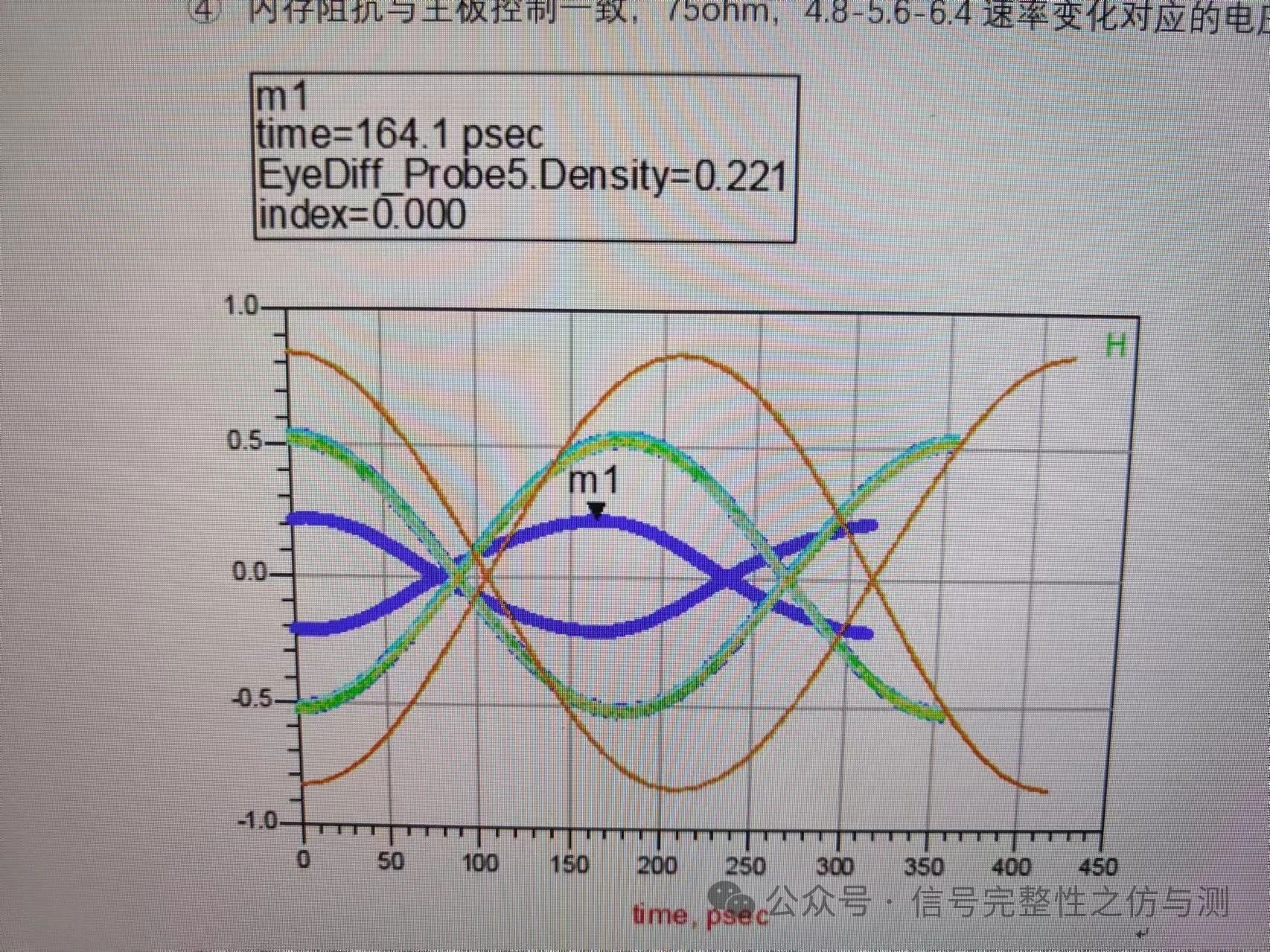

那么,内存阻抗与主板控制一致,75Ω,速率在4.8-5.6-6.4变化时对应的电压变化是什么样呢?

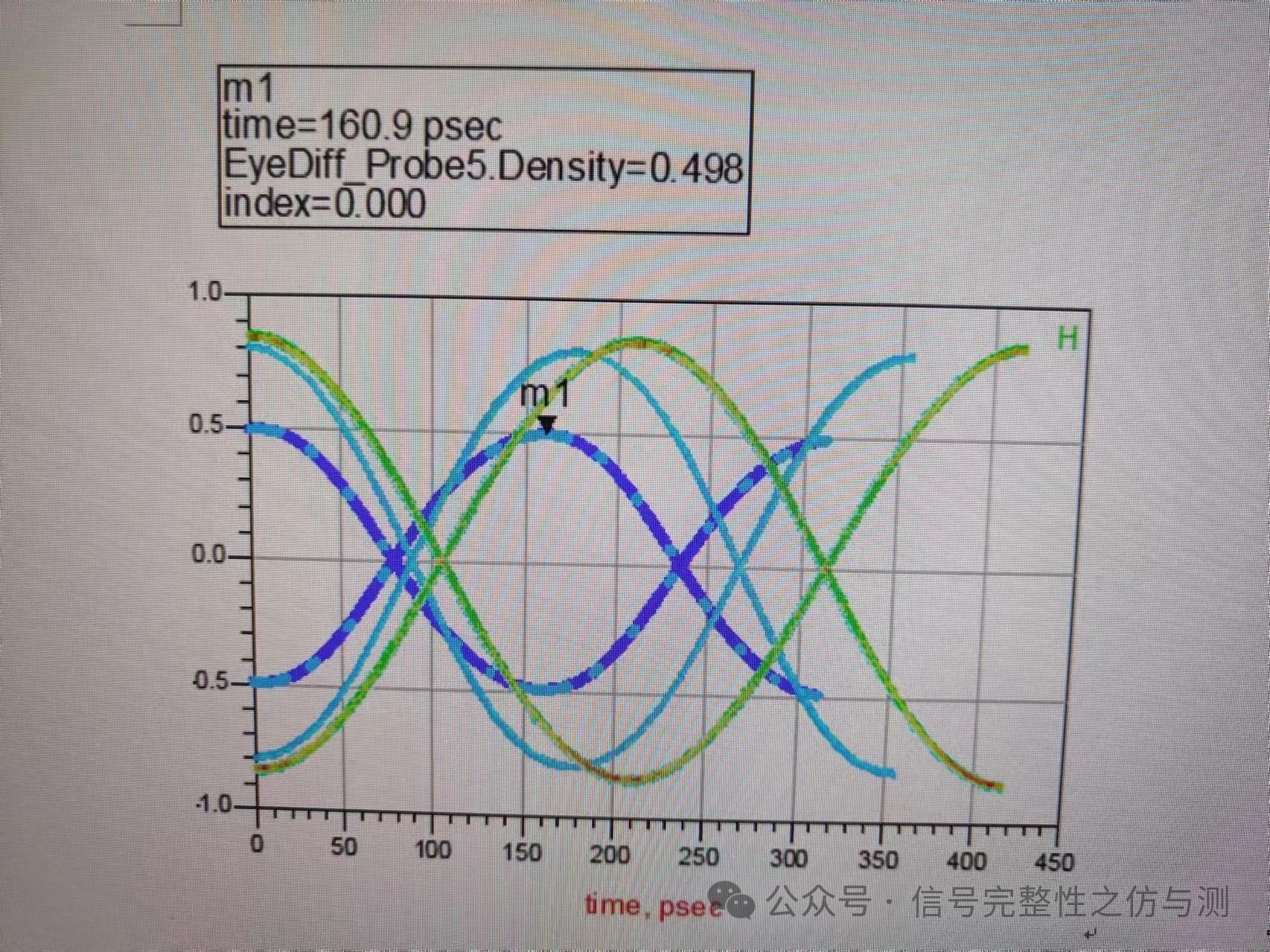

内存阻抗与主板控制不一致,50欧姆,速率在4.8-5.6-6.4变化时对应的电压变化是什么样呢?

结果不言而喻!

因此,为了适应DDR5更高速率,内存的阻抗设计为50ohm,通过更低的阻抗来减少信号的衰减和失真。

-

德明利推出CKD DDR5内存条 为AI PC提供稳定高频内存解决方案2026-04-03 1323

-

创见推出DDR5 6400 CUDIMM内存条2025-01-24 2175

-

雷克沙推出全新战神之翼系列DDR5内存条2024-12-12 1723

-

金士顿发布FURY Renegade DDR5 CUDIMM内存条2024-10-25 1412

-

研华工控机购买指南:DDR3、DDR4、DDR5怎么选?如何选择内存条?2024-06-28 5454

-

台电追风A60 DDR5内存条全面上市2023-12-05 2559

-

DDR内存条的设计.zip2022-12-30 787

-

Longsys DDR5内存条预计在2022年进入量产阶段2021-11-02 4156

-

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!2021-04-27 15850

-

厂商加快DDR5内存条研发速度2021-01-06 2943

-

国内厂商已开始布局DDR5内存明年量产2020-12-08 3684

-

内存条ddr4和显卡ddr52020-07-30 3436

-

SK海力士最新DDR5 EEC内存条,性能有巨大的提升2020-01-09 6527

-

DDR内存条对比分析2011-12-29 4809

全部0条评论

快来发表一下你的评论吧 !