双极型工艺制程技术简介

描述

本章主要介绍了集成电路是如何从双极型工艺技术一步一步发展到CMOS 工艺技术以及为了适应不断变化的应用需求发展出特色工艺技术的。

首先从双极型工艺技术发展到 PMOS 工艺技术,再到 NMOS 工艺技术,但是无论是双极型工艺技术和 NMOS 工艺技术都遇到了功耗问题,最后引出低功耗的CMOS 工艺技术,CMOS 工艺技术是目前工艺技术的主流。但是CMOS工艺技术没有办法满足不断变化的应用需求,所以发展出如 BiCOMS、BCD 和HV-CMOS 等特色工艺技术。

另外还介绍了 MOS集成电路的发展历史,以及 MOS 晶体管的发展和面临的挑战,也就是MOS晶体管按比例缩小的过程中遇到的问题和出现的新技术,为引出先进工艺技术打下基础。

双极型工艺制程技术是最早出现的集成电路工艺制程技术,也是最早应用于实际生产的集成电路工艺制程技术。随着微电子工艺制程技术的不断发展,工艺制程技术日趋先进,其后又出现了 PMOS、NMOS、CMOS、BiCMOS 和BCD等工艺制程技术。

1947年,第一只点接触晶体管在贝尔实验室诞生,它的发明者是 Bardeen、Shockley 和Brattain。1949年,贝尔实验室的 Shockley 提出pn 结和双极型晶体管理论。1951年贝尔实验室制造出第一只锗双极型晶体管,1956年德州仪器制造出第一只硅双极型晶体管,1970年硅平面工艺制程技术成熟,双极型晶体管开始大批量生产。

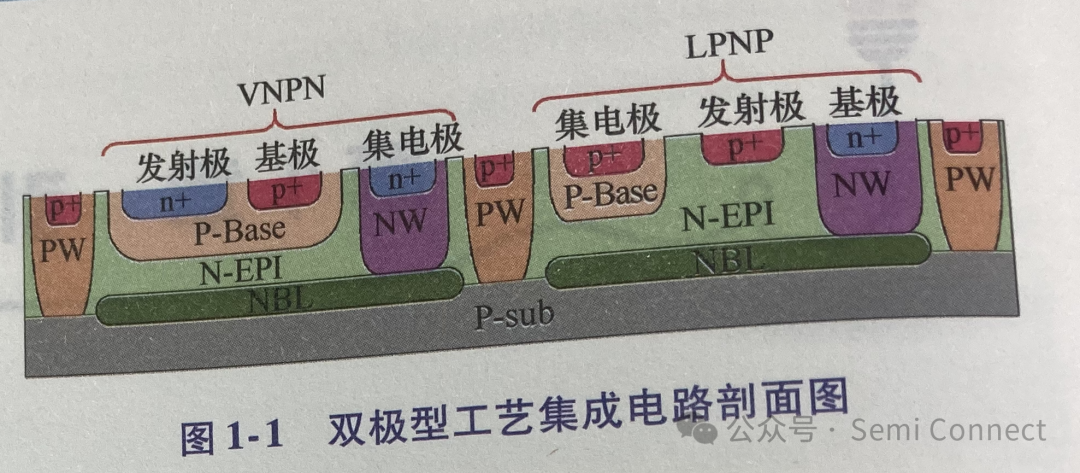

双极型工艺制程技术大致可以分为两大类:一类是需要在器件之间制备电隔离区的双极型工艺制程技术,采用的隔离技术主要有pn 结隔离、全介质隔离以及 pn结-介质混合隔离等。采用这种工艺制程技术的双极型集成电路,如 TTL(Transistor Transistor Logic,晶体管-晶体管逻辑)电路、线性/ECL(Emitter Couple Logic,射极耦合逻辑)电路和 STTL(Schot-tky Transistor Transistor Logic,肖特基晶体管-晶体管逻辑)电路等;另一类是器件之间自然隔离的双极型工艺制程技术,I2L(Integrated Injection Logic,集成注入逻辑)电路采用了这种工艺制程技术。图1-1所示的是属于第一类采用pn结隔离技术的双极型工艺集成电路的剖面图,VNPN 是纵向 NPN (Vertical NPN),LPNP 是横向 PNP (Lateral PNP),n +是n 型重掺杂扩散区,P+是P型重掺杂扩散区,P-Base 是p型基区,PW (P-WELL)是p型阱,NW(N-WELL)是深n型阱,NBL(N type Buried Layer)是n型埋层,P-sub(P-substrate)是P型衬底,N-EPI(N-Epitaxial)是n 型外延层。

由于双极型工艺制程技术制造流程简单,制造成本低和成品率高,另外在电路性能方面它具有高速度、高跨导、低噪声、高模拟精度和强电流驱动能力等方面的优势,它一直受到设计人员的青睐。双极型晶体管是电流控制器件,而且是两种载流子(电子和空穴)同时起作用,它通常用于电流放大型电路、功率放大型电路和高速电路。它一直在高速电路、模拟电路和功率电路中占主导地位,但是它的缺点是集成度低和功耗大,其纵向(结深)尺寸无法跟随横向尺寸成比例缩小,所以在VL-SI(超大规模集成电路)中受到很大限制。在20世纪60年代之前集成电路基本是双极型工艺集成电路,双极型工艺集成电路也是史上最早发明的具有放大功能的集成电路,直到20世纪70年代 NMOS 和CMOS 工艺集成电路开始在逻辑运算领域逐步取代双极型工艺集成电路的统治地位,但是在模拟器件和大功率器件等领域双极型集成电路依然占据重要的地位。

-

BiCMOS工艺制程技术简介2024-07-23 4532

-

HV-CMOS工艺制程技术简介2024-07-22 7469

-

BCD工艺制程技术简介2024-07-19 8153

-

PMOS工艺制程技术简介2024-07-18 5633

-

BGA基板工艺制程简介2022-11-16 1962

-

7.1.3 双极型功率器件优值系数∈《碳化硅技术基本原理——生长、表征、器件和应用》2022-02-09 1280

-

电气装配与工艺实训装置(单面双组型)有哪些技术指标2021-09-27 2843

-

双极型工艺报告的详细资料免费下载2019-10-21 1245

-

COMS工艺制程技术与集成电路设计指南2019-03-15 6554

-

CMOS工艺制程技术的详细资料说明2019-01-08 2538

-

双极型制作工艺2012-08-20 3922

-

X78XX:双极型线性集成电路中文资料简介2012-07-26 6070

全部0条评论

快来发表一下你的评论吧 !