三星电子公布2024年异构集成路线图,LP Wide I/O移动内存即将面世

描述

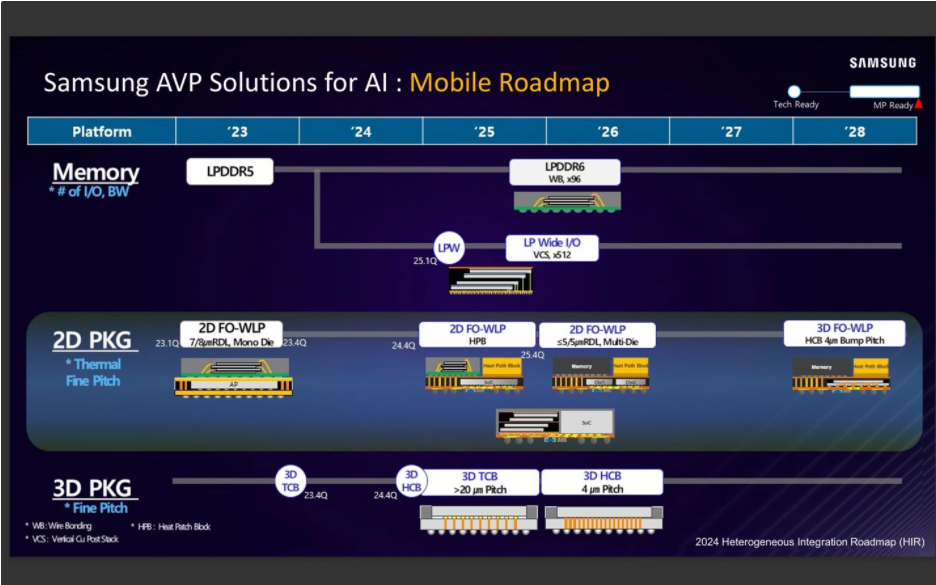

7月17日,三星电子公布了其雄心勃勃的2024年异构集成路线图,其中一项关键研发成果引发了业界广泛关注——一款名为LP Wide I/O的创新型移动内存即将面世。这款内存不仅预示着存储技术的又一次飞跃,还可能与公司此前提及的LLW(Low Latency Wide I/O)内存存在某种关联,尽管两者之间的确切关系尚待揭晓。

据路线图规划,LP Wide I/O内存预计将于2025年第一季度在技术层面达到成熟状态,随后在同年下半年至2026年期间做好量产准备,正式迈向市场。其核心亮点在于其单封装位宽达到了惊人的512bit,这一数字几乎是目前高端HBM内存位宽的一半,远远超出了当前LPDDR5内存的四通道共64bit规格,即便是未来的LPDDR6内存,其位宽也仅规划为96bit。

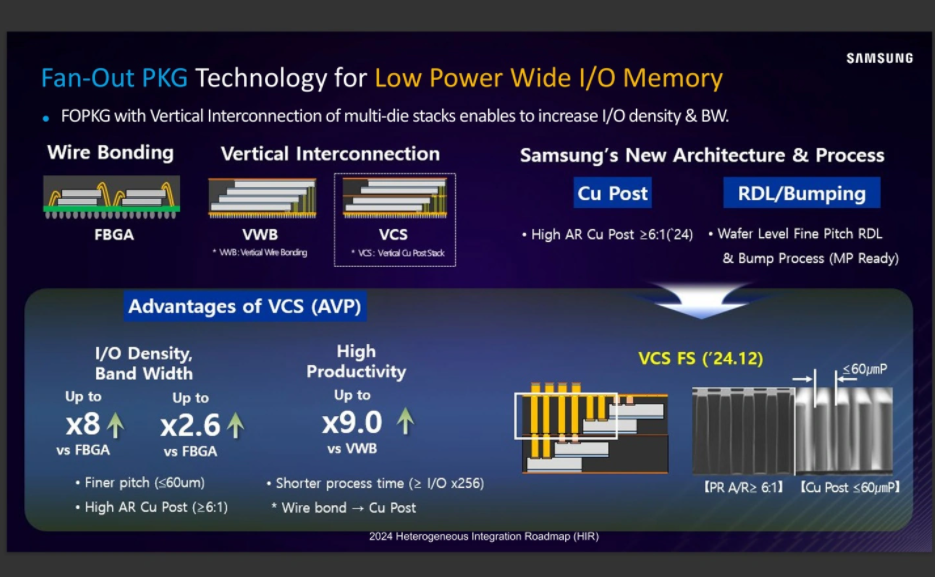

如此巨大的位宽提升,意味着LP Wide I/O内存将能够提供前所未有的内存带宽,这对于日益增长的设备端AI应用等高性能需求场景而言,无疑是巨大的福音。为了实现这一突破性的位宽设计,三星电子不得不面对如何在有限空间内堆叠DRAM芯片的挑战,而传统的HBM所采用的TSV(硅通孔)技术显然并不适合移动内存的场景。

为此,三星电子独创了VCS(Vertical Cu Post Stack)垂直互联技术,这一技术巧妙地结合了扇出封装与垂直通道的概念,与SK海力士的VFO技术有异曲同工之妙,但在生产效率与性能上据称有显著提升。三星电子自豪地宣称,其VCS技术相比传统引线键合技术,在I/O密度和带宽上分别实现了8倍和2.6倍的增长;而与类似的VWB(Vertical Wire Bonding,疑似指代SK海力士的VFO技术)相比,VCS技术的生产效率更是高达9倍,展现出了巨大的技术优势。

值得注意的是,三星电子还透露,作为其内存产品线的另一重要成员,LPDDR6内存同样预计将在2025至2026年期间达到量产就绪状态,进一步丰富了公司的移动内存产品线,为市场带来更多选择。这一系列动作无疑表明了三星电子在推动移动存储技术革新方面的坚定决心与强大实力。

-

靠谱不?分析师自制苹果2013年产品路线图2013-01-19 3208

-

嵌入式学习路线图分享2018-07-13 2899

-

物联网学习路线图2020-04-20 3847

-

Intel公布2021年CPU架构路线图及封装技术2020-11-02 2540

-

威盛公布嵌入式平台发展路线图2006-03-13 619

-

三星SSD路线图更新QLC闪存是重点 三星将于2019年试产QD-OLED2018-10-18 6748

-

三星全新Exynos处理器即将面世2020-12-21 3089

-

超越摩尔,三星的异构集成之路2021-10-10 6659

-

三星晶圆厂最新路线图 2025年推出首个GAA制程先进封装2023-07-06 3158

-

三星目标2025年主导汽车存储市场 公布路线图2023-11-23 1604

-

美国公布3D半导体路线图2024-03-25 1777

-

谷歌将揭晓2024年Google I / O大会三星XR头显功能2024-04-16 1120

-

三星公布最新工艺路线图2024-06-17 1283

-

三星电子计划2025~2026年推出LP Wide I/O内存2024-07-18 2468

-

三星电子计划在2026年推出最后一代10nm级工艺1d nm2024-09-09 1359

全部0条评论

快来发表一下你的评论吧 !