常用代码的逻辑级数预估

描述

一、前言

现在我们知道,想要FPGA的主频跑得高,那么工程的逻辑级数要尽量低才行,但一个大的逻辑工程如此的庞大,代码已经编写完成再来考虑逻辑级数那就有一点晚了,因为很多功能都是时序强相关,改了一个地方可能牵扯到更多的地方要跟着改,工程大了改起来就痛苦了。因此想要FPGA设计的逻辑级数低,从每个代码块就需要开始注意了,因此可以把常见的一些语法块所综合的逻辑级数总结起来。这样我们不仅大致知道逻辑级数的范围,同时优化代码的时候也知道从哪里下手。当然,我们需要通过Vivado来进行综合,逻辑级数的性能也与Vivado的综合策略有很大的关系,一般来说使用默认的Vivado的综合策略就可以了,经过这么数十年的迭代,可以认为Vivado的综合策略已经是最优的了,影响逻辑级数主要变数的就是代码的设计质量了。注意本文的结论是基于K7系列FPGA得到的,其他器件由于资源结构发生变化则需要重新总结。

FPGA设计中常见的逻辑有哪些?虽然一个大型工程很复杂,但实际上分解出来的也基本都是是加法器(减法器、累加器),比较器、条件语句(CASE语句)组成的,其他的例如乘法器和存储器基本都是使用内部专用资源实现的,因此这里不作为分析。如果我们能把这些主要的元素全部综合一遍,大致了解其逻辑级数的范围,对于我们整个设计的逻辑级数控制是很有帮助的。

二、加法器

我们首先分析一个8bit位宽的加法器

module test( input [7:0]a_i, input [7:0]b_i, output [7:0]sum_o ); assign sum_o = a_i + b_i; endmodule

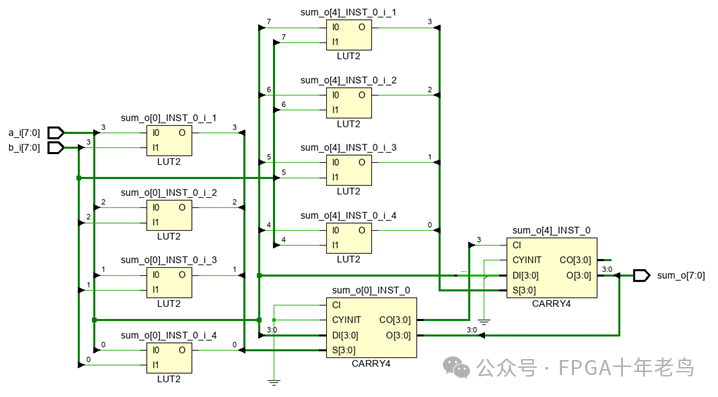

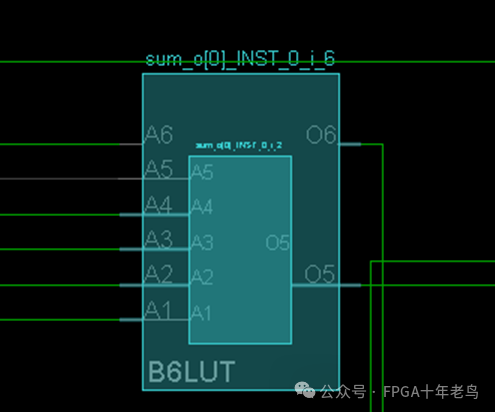

从原理图网表可以看出逻辑级数为3。这里我们探究一下LUT2和CARRY4这些原语的实现细节。在数字电路中,二进制加法器的公式为:

式中 表示异或逻辑,+表示或逻辑,AB表示A和B的与逻辑,O表示和,CO表示进位。下标i表示bit的位数。

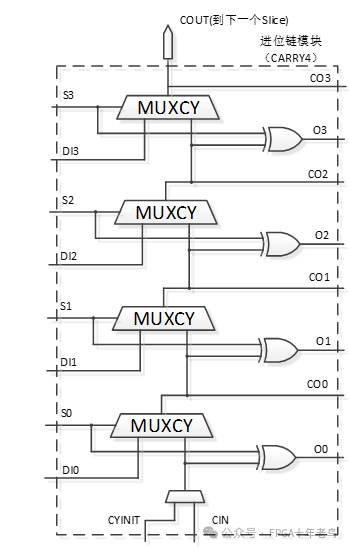

而我们看一下CARRY4的内部结构,如图所示。

当且时,那么就可以得出二进制加法器的公式,如下:

而是通过通过LUT2来实现,CARRY4可以实现4位的二进制加法器,同时CARRY4可以接收来自上一个CARRY4进位,以及将当前第4bit的进位输出到下一级CARRY4,以便组成更高位数的加法运算。

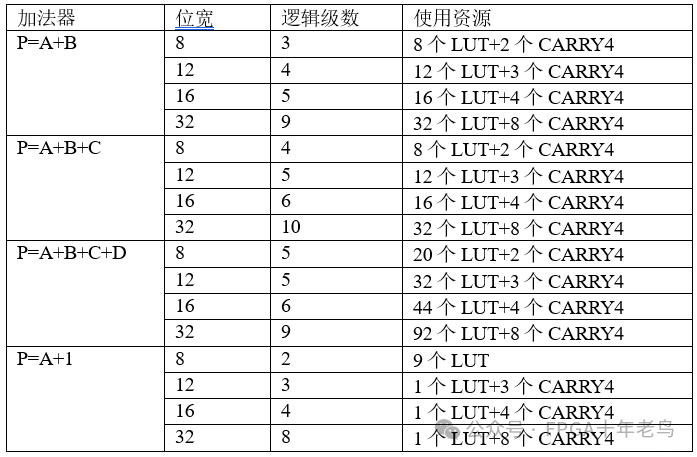

下面是通过调整位宽所测得的逻辑级数,大家可以自己实践来做更细致化的统计,以满足自己设计时对逻辑级数的估计需求。

从表中观察到以下几个现象:

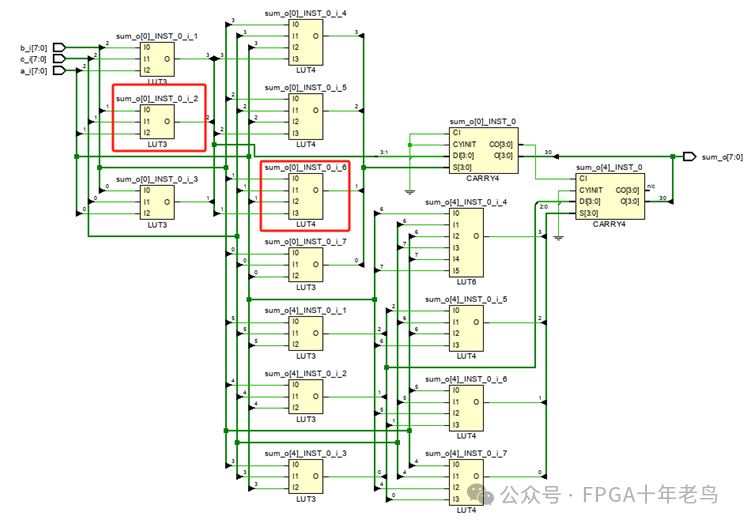

(1)P=A+B+C与P=A+B使用的是相同的LUT和CARRY4资源,相同位宽下逻辑级数只是增加了1级。图9-3是P=A+B+C的综合原理图,是为什么从原理图中明明发现P=A+B+C的8bit加法中有14个LUT,为啥实际使用的资源是8个LUT呢?这里就不得不佩服Xilinx 7系列芯片中的6输入查找表(LUT6)设计了,LUT6内部可以拆分成两个LUT5,因此LUT6设计了两个输出端口。只需要满足两个任意定义的五输入或更少输入的布尔函数(使用LUT6的A1-A5端口),只要这两个函数包含共同的输入,且LUT6的A6端口拉高的时候,就可以实现两个LUT5或更少端口的LUT。例如图9-3其中两个方框中LUT3和LUT4包含相同的输入,因此被综合进了同一个LUT6中,如图所示。

因此做设计,可以综合时序和资源的考虑,如果时序要求没有这么高,则可直接写为P=A+B+C,相比于拆成两部分做两级流水(TEMP = A +B、 TEMP = A + C),能够节省一半以上的逻辑资源。

(2)P=A+B+C+D的32bit加法的最高逻辑级数比P=A+B+C的32bit加法的最高逻辑级数还要小,初一看感觉有点突破认知,按理来说前者的最高逻辑级数会比后者高才对。同时我们看到前者比后者多用了60个LUT,因此逻辑级数除了取决于自己的代码外,还会与综合的实现算法有关系,这点应该是综合工具通过资源和时序(逻辑级数)的性能进行综合判断。

(3)P=A+1型加法或者其变种累加器P=P+1,虽然是一个常数相加,使用的资源比常规的加法运算少很多,但位宽大了之后其逻辑级数也是不容忽视的。

-

常用逻辑门电路符号图2009-04-07 0

-

可编程逻辑芯片 FPGA 速度级数2012-09-13 0

-

常用逻辑电平2016-01-29 0

-

如何对simth滞后系统预估器编程进行matlab仿真呢2021-11-19 0

-

傅立叶级数ppt2008-10-30 522

-

几种常用高速逻辑电平电路的特点及应用2007-08-21 1301

-

常用集成电路逻辑符号对照表2007-11-22 11434

-

常用逻辑门及其符号简介2009-12-03 62754

-

逻辑代数的基本公式和常用公式2010-02-28 21228

-

常用基本逻辑门电路功能测试实验2010-03-08 29936

-

常用的FPGA代码2016-05-26 572

-

如何在C代码中插入寄存器?2021-02-02 2945

-

Verilog常用的循环语句及用途2023-05-12 1743

-

三角级数和傅里叶级数的区别2023-09-07 1334

-

常用的组合逻辑电路有哪些2024-07-30 251

全部0条评论

快来发表一下你的评论吧 !