后摩尔定律时代芯片的出路

半导体新闻

描述

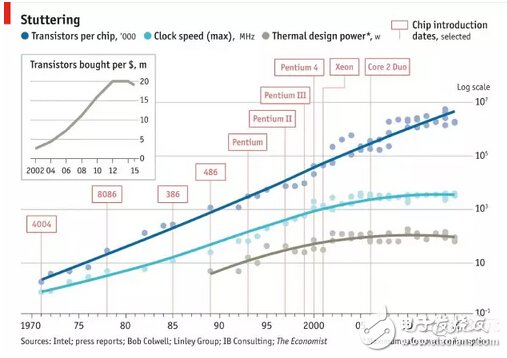

摩尔定律最早由英特尔联合创始人 Gordon Moore 提出,内容是:当价格不变时,集成电路上可容纳的元器件数量约每隔 18-24 个月就会增加一倍,性能也将提升一倍。后面 Moore 修正了模型,变为:单位面积芯片上的晶体管数量每两年能实现翻番。

谁也想不到,这个 1971 年提出的定律,竟能支配计算领域长达 44 年的时间。直到今天,英特尔官方宣布,放弃过去十年坚持的 Tick-Tock 处理器发展模式,通过延长制造工艺的生命周期,将之前的处理器研发周期从“两步”变成“三步”:

制程工艺(PROCESS)

架构更新(ARCHITECTURE)

优化(OPTIMIZATION)。

英特尔 CEO Brian Krzanich 表示,“我们的更新周期已经从 2 年延长到了 2 年半。”

这意味着对于英特尔而言,摩尔定律已经失效。

摩尔定律的失效,并不出乎人们的意料。微软研究院的副总裁 Peter Lee 曾经开玩笑说:“预测摩尔定律将会失效的人数,每 2 年都会翻上一番。”而在英特尔官方宣布放弃追求摩尔定律曲线的时候,这一天也就到来了。

摩尔定律对整个计算产业有着举足轻重的影响。我们最为关心的是,在摩尔定律之后,计算领域会发生什么改变?答案就在以下十大方向,包括:

1、从根本上改变芯片的设计:包括 3D 维度的芯片设计、周围栅极、量子隧穿效应等。

2、寻找硅材料的替代品:包括硅 - 锗(SiGe)、合金隧道、III-V 材料设计、石墨烯、自旋晶体管等。

3、从现有晶体管寻找出路:多核芯片、特制芯片、新品种芯片。

4、计算框架的变革:量子计算框架、光通信、量子阱晶体管、神经形态计算、近似计算。

摩尔定律的黄昏将带来机遇、混乱和大量的摧毁性创意。一个原本依赖于大量设备稳步升级的行业将被撕碎。那么计算的未来,究竟会怎样发展?

摩尔定律背后的物理瓶颈

摩尔定律并不是一套“物理定律”,而是大公司定义的经济规则。在以英特尔为首的芯片公司定义了一套游戏规则,要在两年的时间里把晶体管数量增加一倍,同时成本减少一半。

过去这套经济规则并没有违反物理定律。研究人员发现,当晶体管在体积变小时,性能也会变得更好:

体积较小的晶体管在开启关闭时需要的能量更少、速度也更快。这意味着你可以使用更多更快的晶体管,而无需付出更多能量或产生更多废热,因此芯片可以在越做越大的同时、性能也越来越好。

能做到这一点的公司获得了成功,而做不到的则逐渐被历史淘汰。但当晶体管尺度变小到小型化的极限“原子尺寸”的时候,事情变得和人们期待的有所不同。

在这种原子尺寸下,现代晶体管的源极和漏极非常接近,大约是 20 纳米的量级。这会引起隧道泄露,剩余电流能够在装置关闭的时候通过,浪费了电量和产生不必要的热量。

从这个来源产生的热量会导致严重的问题。许多现代芯片都必须低于最高的速度运行,或者周期性的关闭部分开关以避免过热,这限制了它们的性能表现。

现在的芯片晶体管间距已经在 10 纳米左右的量级了。减小间距会带来非线性的成本增加,根据国际商务战略公司 CEO Handel Jones 的估计,当业界能够生产晶体管间距 5 纳米的芯片时(根据过去的增长率来看可能出现在2020年代早期),晶圆厂的成本可能飙升到超过 160 亿美元,这是英特尔目前年营收的三分之一。

2015 年英特尔的年营收是 554 亿美元,只比 2011 年增长了2%。这种营收的缓慢增长与成本的大幅上涨,带来了显而易见的结论:从经济的角度来看,摩尔定律已经过时了。

摩尔定律的下一步

很显然,传统的芯片设计方案已经到达了瓶颈。要找到下一代芯片,会需要两个广泛的变化。

1、晶体管的设计必须从根本改变;

2、行业必须找到硅的替代品,因为它的电学属性已经被推到了极限。

1、根本改变芯片设计

(1)第三个维度

针对这个问题,一个解决方案是重新设计隧道和栅极。按照惯例,晶体管一直是平面的,但自从 2012 年之后,英特尔给产品增加了第三个维度。要启用它来生产出只有 22 纳米距离的芯片,它切换到了被称为“finFETch”的晶体管。这个产品让一个通道在芯片表面竖起来,栅极围绕着该通道三个裸露的方向(第二张图),这使得它能够更好的处理发生在隧道内部的任务。这些新的晶体管做起来比较棘手,但相比过去相同尺寸的版本,要快 37%,而且仅仅消耗一半的电量。

(2)Gate-All-Around

下一个逻辑步骤,Argonne 国家实验室的 Snir 先生说,是周围栅极(Gate-All-Around)的晶体管,它的通道被四面的栅极环绕。这能提供最大的控制,但它给制造过程增加了额外的步骤,因为栅极必须在多个部分分别构建。大的芯片制造公司,例如三星曾经表示,它可能会使用周围栅极的晶体管来制造 5 纳米分离的芯片,三星以及其他的制造商,希望能做 2020 年代前期达到这个阶段。

(3)量子隧穿效应

除此之外需要更多外部的解决方案。一种想法是利用量子隧穿效应,这对于传统的晶体管来说是很大的烦恼,而当晶体管缩小的时候,事情也总会变得糟糕。这是有可能的,通过施加电场,以控制隧道效应发生的速率。低泄漏率对应状态 0,高泄漏率对应 1。第一个实验隧道晶体管由 IBM 的团队在 2004 年展示。从那之后,研究人员一直致力于商业化。

2015 年,美国加州大学一个由 Kaustav Banerjee 领导的研究小组,在 Nature 上发表了一篇文章,他们已经建立了一个隧道晶体管,工作电压只有 0.1,要远远小于比目前正在使用的 0.7V,这意味着更少的热量。但是在隧道晶体管变得可用之前,还有更多的工作需要完成。ARM 的微芯片设计师 Greg Yeric 说道:“目前它们在打开和关闭开关的速度还不够快,不足以让它们在快速的芯片中使用。Jim Greer 和他在爱尔兰 Tyndall 研究院的同事提出了另一个思路,它们的设备被称为无连接纳米线晶体管(JNT),旨在帮助解决小尺度制作的问题:让掺杂做的足够好。“这些天你正在谈论半导体掺小量的硅杂质,然后会很快来到这个点,即便是一个或两个杂质原子的错误位置,都会激烈的影响晶体管的表现。”Greer 博士说道

相反,他和他的同事提出建立自己的 JNTs,距离一种一致掺杂的硅,只有 3 纳米的跨越。通常来说,这会导致一条电线,而不是一个开关:一个有着均匀导电能力的设备,而且不会被关闭。但是在这种微小的尺度下,栅极的电子影响能够刚好穿透电线,所以单独的栅极能够防止,在晶体管关闭的时候进行电流流动。

传统晶体管的工作原理是,在原本彼此隔离的源极和漏极之间搭建电桥。Greer 博士的设备以其他的方式工作:更像一个软管,栅极充当着避免电流流动。“这是真正的纳米技术,”他说:“我们的设备只能在这个尺度上工作,而最大的好处是,你不需要担心制造这些繁琐的结点。”

2、寻找硅的替代品

芯片制造商也在用超越硅的材料进行试验。去年,一个包括了三星、Gobal Foundries、IBM 和纽约州立大学的研究联盟,公布了一个 7 纳米的微芯片,这个技术被在 2018 年以前,并不被期待来到消费者的手中。它使用了和上一代发布的 FinFET 相同的设计,做了轻微的修改,但尽管大多数的设备都是从通常的硅制作完成的,其晶体管大约一半都是由硅 - 锗(SiGe)合金制成的隧道。

(4)硅 - 锗(SiGe)合金

选择了这种设计,是因为在某些方面,这是比硅更好的导体。再一次,这意味着更低的功率使用,并且允许晶体管更快的打开和关闭,提升芯片的速度。但这不是万能药,IBM 物理科学部门的负责人 Heike Riel 说。现代芯片从两种晶体管构建,一个被设计为传导电子,带着负电荷。其他种类被设计来导入“洞”里,这会放置在可能、但意外没有包含电子的半导体中。这些的出现,表现的就像它们带有正电荷的电子。并且,虽然硅锗擅长输送“洞穴”,但相比硅来说,它不是很擅长移动电子。

沿着这些线路到更高性能的表现,未来的路径可能需要同时把硅锗和其他混合物,让电子能比硅制材料中更好的移动。拥有最好电学性能的材料是一些合金,例如铟,镓和砷化,在元素周期表中统称为 III-V 材料。

麻烦的是,这些材料很难和硅进行融合。它们晶格中原子之间的间隔距离,和硅原子之间有很大的不同。所以将它们的一层增加到硅基片中,从中所有芯片的制作都会导致压力,这会带来芯片断裂的压力。

(5)石墨烯

最著名的替代方法是石墨烯,它是单原子厚的碳形式(二维)。石墨烯在操作电子和空穴的时候表现的非常好,但难点在于如何使它停止下来。研究人员一直试图通过掺杂、压碎、挤压石墨烯,或者使用电场来改变电学的性能。现在已经有了一些进展:曼彻斯特大学 2008 年报告了一个正在工作的石墨烯晶体管;加州大学 Guanxiong Liu 带领的研究小组,2013 年使用了一种有“负电阻”特性的材料以制作设备。但对石墨烯真正的影响,Yeric 博士说道,是刺激对其他二维材料的兴趣。“石墨烯是一个打开的盒子,”他说道:“我们现在正在寻找像二硫化钼的物质,或黑色磷、磷硼的混合物。”重要的是,所有的这些都像硅一样,可以很容易打开和关闭。

如果一切都按照计划进行,Yeric 博士说,新型的晶体管设计和新材料,可能让事情在 5 年或 6 年里还滴答作响,到了那个时候可能会有 5 纳米的晶体管。但除此之外,“我们已经用尽了一切方法,避开真正根本性的需求。”

6)自旋晶体管

对于这方面来说,他最倾向的候选对象是所谓的“自旋电子学”。电子系使用一个电子的电荷来代表信息,自旋电子学使用“旋转”,这是电子的另一个固有属性,并且和物体拥有的转动能量相关联。它很有用,旋转有两个变化:向上和向下,它可以用来表示 1 和 0。计算机行业对自旋电子学已经有了一些经验:例如它是硬盘里的应用。

对自旋晶体管的研究已经超过了 15 年,但是迄今为止还没有投入生产。难做的是,驱动它所需的电压是非常微小的:10-20 毫伏,相比常规的晶体管要少数百倍,这可以解决热量的问题。但是这也带来了设计的问题, Yeric 说道。有着这种分钟电压,在电子噪音中区分 1 和 0,变得非常棘手。

“在实验室里建造一个新奇的晶体管,是相对而言比较容易的事情,”分析师 Linley Gwennap 说道。。“但是要取代我们今天正在做的事情,你需要在一个芯片上投入数十亿美元,需要有合理的成本,以及非常高的可靠性,而且几乎要没有任何缺陷。我不会说着无法做到,但这是非常困难的。”这也让寻找其他的办法制作更好的计算机,变得十分重要。

3、从现有晶体管寻找出路

严格的说,摩尔定律是关于越来越多数目的组件,可以被整合进一个给定的设备中。更一般的说,计算机总是变得越来越好。随着晶体管变得越来越难以缩小,计算公司开始考虑更好的利用已有的晶体管设备。“过去管理者们不希望在密集设计上投入过多,”ARM 的 Greg Yeric 说道:“我认为这将会开始发生变化。”

一种方法是:让现有的芯片工作强度更大。电脑芯片有一个主时钟,每次它滴答的时候,里面的晶体管就会进行开、关动作。更快的时钟,意味着更快的执行指令。提高时钟速率已经使得芯片在过去的 40 年里变得更快的主要途径。但是,在过去的 10 年里,时钟速率几乎没有变化。

(7)多核芯片

芯片制造商通过使用额外的晶体管,压缩以复制芯片已有的线路作为回应。这种“多核心”芯片,把一些比较慢的处理器捆绑起来,要比单纯依靠单一的快速处理器表现的要更好。大多数现代的台式计算机是 4 到 8 核,有的甚至有 16 个核。

但是,正如业内人士发现的,多核芯片的速度达到了限制。“大家一致认为,如果我们继续这样做,如果我们的芯片有 1000 个核,那么一切都会好起来的。”微软芯片设计专家 Doug Burger 说道。但是,要获得最佳的芯片,程序员们不得不把任务人分解成小块,让它们可以同时工作。“事实证明,这真的很难。”Burger 博士说。实际上,对于一些数学任务而言,这是不可能的事。

(8)特制芯片

另一种方法是专攻。使用最广泛的芯片,例如 Intel’s Core 产品线,或者那些基于 ARM’s Cortex 设计的芯片(在地球上几乎所有的手机都能找到)都是多面手,它们具有很强的灵活性。不过这是有代价的:它们可以做一切事情,但没有一件事情能做的完美。调整硬件,让它更好的适用于特别的数学任务,可以让你在解决一般性的任务时,有着 100 到 1000 倍的提升。Intel’s Pentium 芯片的设计者 Bob Colwell 说。

专门特制的芯片已经在计算行业的一些领域中得到使用。最著名的例子是用来提高视频游戏视觉效果的显卡,由Nvidia和AMD之类的公司所设计,在1990年代中期崭露头角。英特尔后来的奔腾芯片也有为一些任务(比如视频解码)设计内置的特制逻辑。但这正也有缺点。

设计新的芯片需要数年的时间,研发成本可能高达数千万甚至数亿美元。特制芯片也比通用用途的芯片更难编程。并且,由于天性使然,它们只能提升某些任务上的性能表现。

特制逻辑更好的目标对象——至少在一开始的时候——可能是数据中心,这些需要庞大计算力的仓库为运行互联网的服务器提供着动力。

由于数据中心处理着海量的数据,它们可能永远都需要一块只能做一件事、但做得非常好的芯片。

基于这个原因,微软——全球最大的软件公司和云计算服务供应商之一——正在投资芯片设计业务。2014年,微软公布了一台名为Catapult的新设备,它使用了一种叫做现场可编程逻辑门阵列(FPGA)的特殊芯片,这种芯片的设置可以随心所欲地进行调整。FPGA提供了一种介于特制和灵活之间的折中,非常实用,带领Catapult研发团队的Burger说道:“这是想要在可编程的软件以外也有可编程的硬件”。当一个任务结束以后,FPGA可以在不到1秒内被重新调整到符合另一个任务的设置。

这种芯片已经被微软的搜索引擎Bing所使用,微软表示,FPGA使服务器在给定时间里能处理的请求数量翻了一倍。除此之外,也有许多其他的潜在应用,Peter Lee这样说道,他是Burger在微软的顶头上司。当某种特定的算法需要被反复应用在数据流上时,FPGA脱颖而出。一种可能性是用Catapult来加密计算机之间的数据流以确保它们的安全性。另一种可能性是将它用在云端互联手机的语音识别和图像识别任务上。

这种技术不是全新的,但是直到现在才找到使用它的理由。全新的是“云端正在以让人瞠目的速度增长,”Burger说道,“现在摩尔定律正在不断放缓,这使得越来越难以增加足够的计算力来与云端相匹配。所以这类后摩尔时代的项目开始变得有经济意义。”

(9)3D 芯片

撇开鳍形晶体管(finned transistors)不谈,现代芯片都是非常扁平的。但是也有一些公司,包括IBM,正在研究将芯片互相叠加——就像一层一层叠高楼房一样——来让设计师们能够在给定区域里安置更多晶体管。三星已经在销售用垂直堆叠的闪存制作的存储系统了。去年,英特尔和Micron(一家大型内存制造商)宣布研发出了一种名为3D Xpoint的新型内存技术,能够利用堆叠的内存。

IBM的研究人员们则致力于研究某种稍有不同的东西:将内存层(slices of memory)叠在处理逻辑层(slices of processing logic)之间,像三明治一样的芯片。这将能让工程师们把大量的计算封装到非常小体积的芯片上,同时带来很大的性能提升。传统计算机的主存储器(main memory)位于距离处理器几厘米远的地方。从硅晶的传递速度(silicon speeds)来说,一厘米已经是非常长的距离了。在这样的距离上传递信号也很浪费能量。将内存移至芯片中以后,就把这些距离从厘米级降到了微米级,使数据传输更快速。

但是3D芯片面对着2个大问题。第一个就是热量。扁平的芯片在这方面已经够糟糕了,在传统数据中心里有数以千计的风扇为服务器散热,轰鸣声不绝于耳。增加叠加层数以后,芯片内部——也就是热量产生的地方——热量增加速度会超过散热速度。

第二个问题是如何接入电力。芯片通过其背面数以百计的金属“针(pins)”与外界相连。现代芯片对电力的需求高到多达80%的金属针都被设置为用来传输电力,只剩下非常少的数量用来处理数据输入和输出。在3D形态下,这种局限被放得更大,因为同样数量的金属针必须要满足比原先复杂得多的芯片。

IBM希望能通过在3D芯片中置入微型内部管道来一箭双雕地解决这2个问题。微流控通道(microfluidic channels)可以将冷却液运往芯片的核心部分,一下子将内部空间中的热量都带走。这家公司已经在传统的扁平芯片上测试了这种液体冷却技术。微流控系统可以最终从1立方厘米的空间里带走大约1千瓦的热量——差不多和电加热器上一片加热器的输出差不多,这个团队的负责人Bruno Michel说道。

而液体能做的不只是冷却芯片,它也能传递能量。受到自己生物学背景的启发,Michel将这种液体命名为“电子血液”。如果他能顺利完成的话,这种液体之于计算机芯片就会像生物血液之于生物体:在提供能量的同时保持体温恒定。Michel的想法是液流电池(flow battery)的一种变体:在液流电池中,两种液体在膜的两侧相遇并产生电流。

液流电池非常简单易懂。电力行业一直在研究液流电池,想将它作为储存来自可再生能源的能量的一种方式。Michel的系统距离商业应用来说还有许多年要走,但是原理已经确立:当Ruch打开液流开关,管道连接到的芯片就会“苏醒”——而你在视线范围内根本看不到插头或是电线。

4、计算框架变革

(10)量子计算

量子技术可以实现速度上的大飞跃,但是只是在特定的应用上。

THE D-Wave 2X 是一个黑色的盒子,看起来有点像电影《2001:太空漫游》中神秘的黑石板的缩小版。它不是一般的机器,它是世界上第一台在商业上可用的量子计算机。目前已经和惠普、微软、IBM 和谷歌建立了合作。

量子计算是一种完全不同的处理信息的方法。在一些普通机器难以处理的问题上,它拥有巨大的速度优势。即使摩尔定律得以无限地延伸下去,这些问题也会持续的困扰普通机器。

而量子计算常常是被误解,有时是过分吹嘘的。其中部分原因是该领域本身还很新,所以其理论基础依然还在搭建中。在一些任务的完成上,量子机器毫无疑问要比最好的非量子机器要快。但是在其它的大部分任务上,这一优势就没那么明显了。“在许多情况下,我们不能确定某个量子计算机会比大家熟知的经典计算机快”,麻省理工学院的计算机科学家 Scott Araronson 说。可用的量子计算机将会是一个福利,但是没人能确定这个福利会有多大。

一个例子是,找到一个很大的数字中的质数因子:这个问题中,随着目标数字变大,难度会呈指数式的递增。换句话说,摩尔定律中,每一次芯片工艺的升级,都只能再影响到稍微大一点的数字。确定质数因子组成了大多数密码的数学支柱,这能在数据游走在互联网上时起到保护作用,恰好是因为这很困难。

两个非常规的量子现象,量子比特,或者说是量子位,在运行是完全不一样的。第一是“叠加”态,指一种持续不确定性的状态,能让原子同时能在不同的状态存在。比如,一个量子粒子是没有具体的位置的,只有说是有出现在某个地方的可能性。在计算层面,这意味着,一个量子位,不是特定的1或特定的0,而是以二者混合的方式存在。第二个量子现象是“牵连”态,不同粒子的发展绑被在一起,所以其中某一个粒子受到影响的话,会立刻在其它粒子上有所反映。 这能让量子计算机在同一时间处理所有的量子位。

结果便是,一台机器能够一次性地呈现并处理海量的数据。例如,一个300量子位的机器,能够同时描绘2300个不同的1和0串,这一数字几乎等同于可见宇宙中所有的原子数量。并且,由于量子位是牵连的,所以要同时处理所有的这些数字也是可能的。

2、其他技术

光通信:使用光来代替电,在电脑,甚至芯片间进行沟通。这将能降低能源消耗,促进发展。惠普、麻省理工学院。

更好的存储技术:建造新的快速、密集和便宜的内存,解决在计算机性能上遇到的瓶颈。英特网,美光(Micron)。

量子阱晶体管:使用量子现象来改变晶体管中的电池的表现,提升性能,使得摩尔定律能够再反复,提升速度,降低能源消耗。

开发新的芯片和软件:在从专门化的芯片串建立的机器上实现代码编写的自动化。已经证明,这在Soft Machines上尤为困难。

近似计算:让计算机的内部表征数字更加精确,以减少每次计算时的比特数量,进而节省能源;允许计算机在计算中发生随机的小失误,能够释放配对的其它比特,这也能节约能源。华盛顿大学,微软。

神经形态计算:以动物大脑中处理信息的缠结和紧密联结的神经束为模型开发设备。这可能会降低能源消耗,想识别模式和其它的AI相关的任务也被证明是有用的。IBM,高通。

碳纳米管晶体管:这些卷起的石墨片材保证了低的能力消耗和高的速度,正如石墨烯那样。和石墨烯不同,它们也能够轻松的关闭。但是很难进行量化生产。IBM,斯坦福大学。

5、总结

摩尔定律的终结将会让计算机行业变得更加的复杂。在摩尔定律处于巅峰时期时,行业是很简单的。计算机的以可预测的方式和速度升级。随着节拍被打乱,计算机行业将成为一个更加复杂的地方。类似智能设计和狡猾的编程是有用的,奔腾的芯片设计师Bob Colwell说:“但是许多一次性的创意的集合不能弥补潜在指数上的不足。”

跟此前相比,发展将变得更不可预测,受到的局限会增多,速度会减慢。“随着摩尔定律消退,我们被迫在三个方面,即力量、表现和成本上作出艰难的选择”,ARM的芯片设计师Greg Yeric说,“一个特定的答案不能完美地服务于所有的终端使用。”

摩尔定律的黄昏将带来机遇、混乱和大量的摧毁性创意。一个原本依赖于大量设备稳步升级的行业将被撕碎。

软件公司将开始进入硬件生产;硬件制造商需要改进自己的产品,更贴近用户越来越多样化的需求。但是,正如Colwell所说,要记得,消费者并不会在乎摩尔定律:“大多数买计算机的人甚至根本胡知道晶体管有什么用”。他们仅仅是想要这个产品,他们购买,是想要更好、更有用。过去,这意味着大多数都是在速度上获得指数式的增长。这条道路已经走到尽头。但是依然有很多别的方法来制造更好的计算机。

-

摩尔定律_摩尔定律是什么2012-05-21 2792

-

Intel在10nm找到了摩尔定律的出路2017-01-03 910

-

小芯片能否“续写”摩尔定律?电子学习 2023-02-08

-

根据“后摩尔时代”芯片行业如何发展?2017-06-27 0

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?2021-07-22 0

-

摩尔定律,摩尔定律是什么意思2010-02-26 1595

-

“虚拟”摩尔定律时代来临?2016-12-07 936

-

所谓的后摩尔定律时代,IC业者面临什么挑战?2017-02-06 6553

-

后摩尔定律时代,国产EDA如何“从0到1”做创新?2022-08-16 2398

-

后摩尔定律时代新赛道—硅光子芯片技术2023-06-15 1162

-

后摩尔定律时代,Chiplet落地进展和重点企业布局2023-12-21 1574

全部0条评论

快来发表一下你的评论吧 !