FPGA和ASIC有什么不同之处

描述

FPGA是“可重构逻辑”器件。先制造的芯片,再次设计时“重新配置”。

ASIC 不需要“重新配置”。你先设计,把它交给代工厂,然后制造芯片。

现在让我们看看这些芯片的结构是什么样的,以及它们的不同之处。

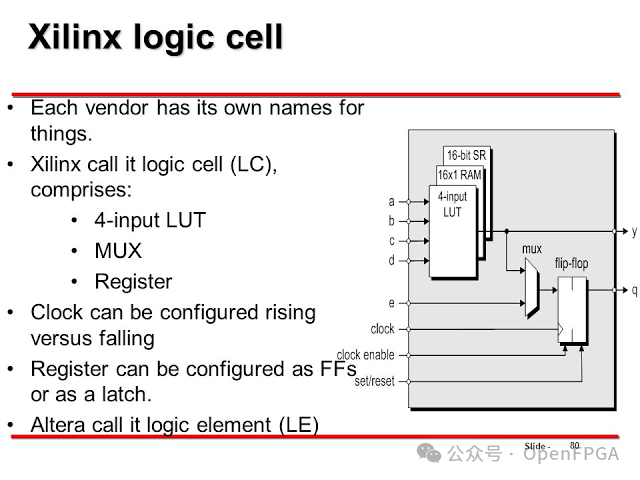

● 逻辑单元:FPGA的基础模块

这是最小的逻辑块。LUT 充当组合逻辑。在DFF的帮助下,可以形成时序逻辑。

它可以构建逻辑门、多路复用器、编码器、加法器;任何真值表都可以作为布尔表达式存储在 LUT 中。

一个 LUT 可以保存有限数量的数据。逻辑单元的 LUT 也是有限的。

具有许多项的布尔表达式需要更多的内存空间,工具在布局布线的时候会将剩余项放入另一个逻辑单元中。这就需要在两个逻辑单元之间有路由信号。

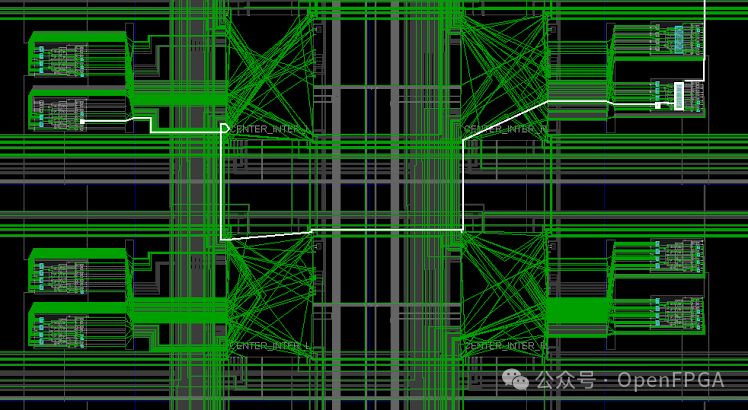

● FPGA路由信号

白线是从一个逻辑单元路由到另一个逻辑单元的信号。可以想象如果实现更大逻辑时候这个导线长度会增加多大。这增加了额外的延迟,降低了时钟频率,消耗了更多的面积和功耗。

所有这一切都只是为了“重构”。

即使设计不需要其他单元或路由信号,它们仍然存在于FPGA芯片路由区域和静态功率中,从而降低了效率。

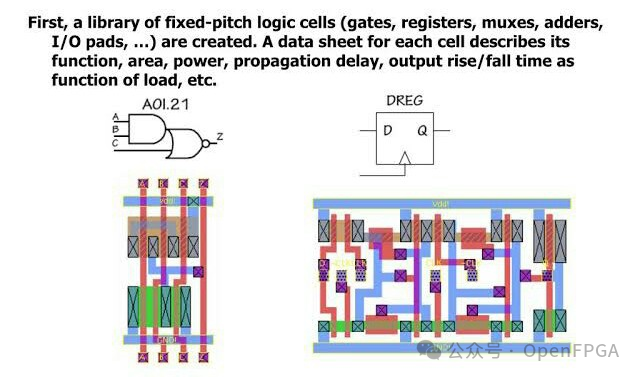

● 标准单元:ASIC的构建模块

标准单元库可以具有小至 NAND 门的组件和 IP,例如加法器、FF、BRAM、多路复用器等。

所有标准单元库都针对面积和功率进行了优化。

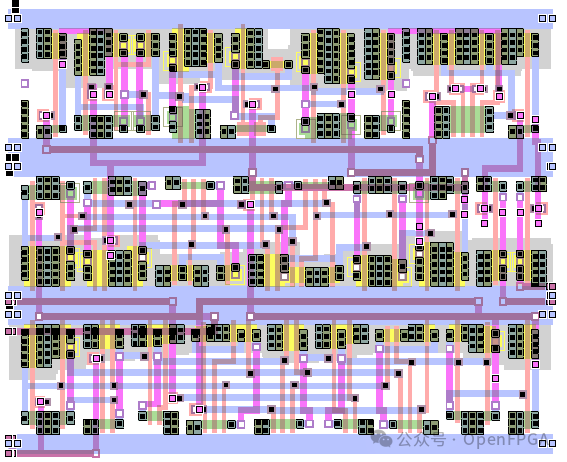

● ASIC布局:

单个单元彼此紧密连接,形成更大的逻辑功能。位置也针对信号传播进行了优化。与FPGA相比,ASIC没有不必要的逻辑和路由开销。这样可以节省更少的面积和功率。还可以实现更快的时钟。

以上这些ASIC会比FPGA具有更高的效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

线性与开关电源有何不同之处?2021-03-11 1854

-

数字舵机与模拟舵机有哪些不同之处2021-08-23 3142

-

伺服电机和闭环步进电机有哪些不同之处2021-09-27 3507

-

低压伺服电机和高压伺服电机有哪些不同之处2021-09-30 3131

-

STM32板与FPGA有哪些不同之处呢2021-10-09 1865

-

GD32和STM32有哪些不同之处2021-10-19 2597

-

PCIe总线和PCI总线有哪些不同之处呢2021-10-26 3055

-

FPGA、ARM和DSP之间的不同之处2021-11-02 5057

-

USART与USAR有哪些不同之处呢2021-12-13 2614

-

嵌入式和单片机有哪些不同之处呢2022-01-19 1374

-

音频拨号和脉冲拨号有哪些不同之处呢2022-01-26 4198

-

Flutter Web有什么不同之处2022-07-08 2029

-

PLC控制系统与电器控制系统有哪些不同之处2022-12-19 2172

-

普通HDMI线和光纤HDMI线有什么不同之处2022-12-23 6454

-

噪音抑制与主动降噪:有何不同之处?2023-11-30 1742

全部0条评论

快来发表一下你的评论吧 !