利用Artix-7 FPGA设计高性能USB器件

参考设计

描述

作者:Tom Myers 高级硬件工程师,Anritsu 公司 tom.myers@anritsu.com

低功耗的赛灵思 FPGA 系列使总线供电的 USB 器件设计垂手可得

凭借在市场中数十亿的端口数量,通用串行总线 (USB) 成为实现主机与外设之间千兆位以下连接的首选接口。不过,由于 USB 规范有着严格的浪涌电流和稳态工作电流限值要求,因此由总线供电的器件应用经常忽视FPGA,而是更愿意采用性能和灵活性都不及 FPGA 的微控制器解决方案。

随着赛灵思低功耗系列器件中最新成员Artix-7 的问世,这种情况将不复存在。通过严加注意系统级功率转换效率和排序,并使用 VivadoDesign Suite 中的功耗估算和优化工具,设计人员能够克服这些挑战性限制,从而实现高性能、紧密集成的并由总线供电的定制器件。

让我们来看一下如何以 Artix-7 MicroBlaze平台为基础构建由总线供电的 USB 2.0 高速器件。在 Anritsu 公司,我们成功利用该方案开发出一款最新的微波功率测量产品。该新产品设计采用USB 2.0 高速接口,相比前一代采用 USB 全速微控制器解决方案的产品而言,显著提高了测量吞吐量。更高的测量吞吐量可缩短制造生产测试应用的测试时间。最终可帮助客户节约成本

系统设计

Anritsu项目中,我们必须要克服的主要障碍是 500 毫安(额定 5V)的稳态电流消耗限值。因此,我们的系统设计方案以功耗预算为中心。我们将数据手册上电流消耗的典型值和最大值制成功率预算电子数据表。

功率预算中的大部分是针对200MB 的最小片外存储器需求。最适合此需求的是标准 4Gb LPDDR2 器件。我们利用厂商应用指南提供的详细方法生成该器件的电流消耗估算,并应用估算的数据流配置文件。我们还利用Xilinx Power Estimator (XPE) 等工具,通过假设功能、时钟速率和触发率,对各种可编程器件及其它解决方案进行了评估。

我们确定了几款备选器件,并且利用MicroBlaze、存储器控制器(使用存储器接口生成器 (MIG))构建出完整系统的子系统,再使用 Vivado 的 IP Integrator 工具添加各种外设的接口模块,以精确功耗、尺寸和I/O 估算值。我们快速获得可综合目标,并利用 Vivado 功耗报告精算功耗大小。

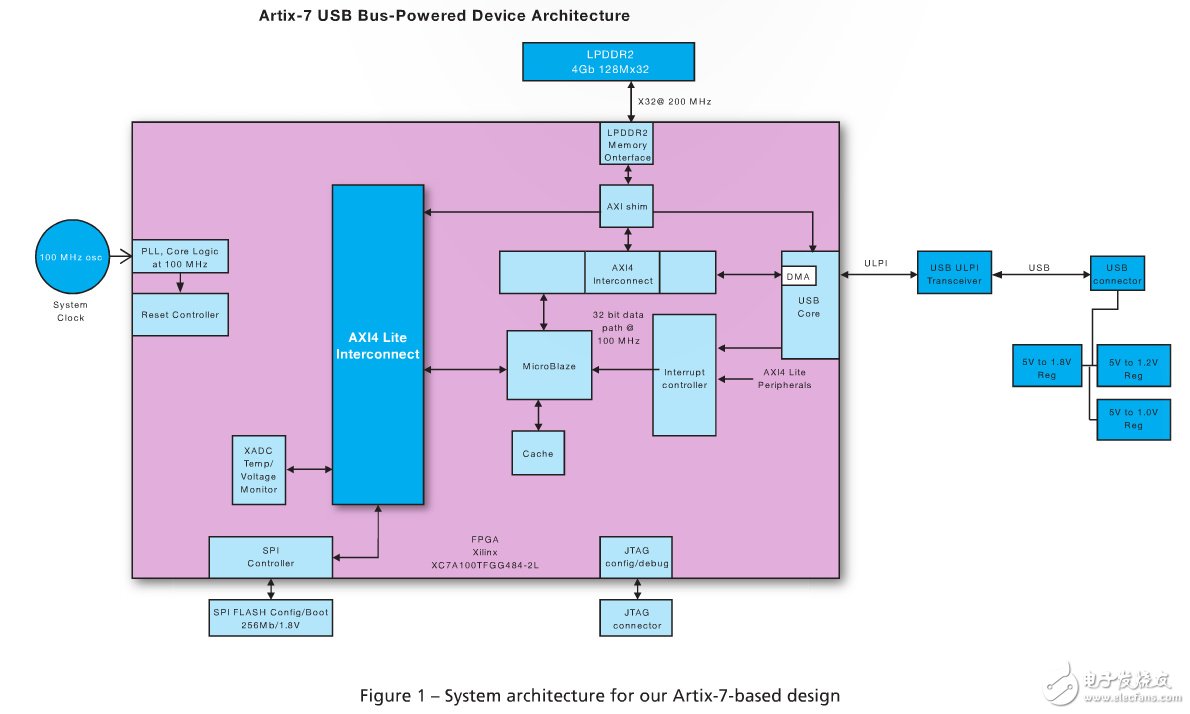

由于MIG 本身不提供到LPDDR2 器件的 AXI 本地连接,因此我们过后自己开发该链路。在我们的AXI层(shim) 做好之前,我们使用 MIG 生成的 LPDDR2 实例设计进行初步的功耗估算和尺寸调整。图1 给出了得到的系统架构。

降低器件的晶片温度能减少漏电流功耗。

策略包括尽可能减小器件晶片尺寸并选择尽可能大的封装

正如“Vivado DesignSuite 用户指南:赛灵思功耗分析与优化”(UG907) 中介绍的那样,降低器件的晶片温度能够减少漏电流功耗。我们使用的策略包括根据应用严格的板级空间约束,尽可能缩小器件晶片尺寸并选择尽可能大的器件封装。

我们通过减少电源数量来最大程度降低转换损耗和稳压器电路成本。在确定器件功耗要求后,我们设计了电压转换电路,用以将额定的USB 5V 总线电压降至电轨电压。目前为止,我们一直在关注稳态电流消耗。不过,还必须考虑到浪涌电流消耗。最小化浪涌电流的方法之一是选择具有软启动功能的稳压器控制上电排序。您必须将FPGA 的上电顺序和斜坡时间要求与 USB 要求进行权衡。

从容应对意料之外的情况

尽管提供各种机制用以正确地关闭和移除USB 设备,但现实中很多用户会不顾警告鲁莽地拔下设备。如果固件更新过程不够稳健可靠,就会出现问题,导致无响应的“砖头”设备,客户不悦,以及成本不菲的设备返厂以进行固件恢复。Anritsu凭借大批量制造测试的可靠性和速度,在竞争中脱颖而出。因此,我们的主要要求包括快速启动时间和快速固件升级时间。

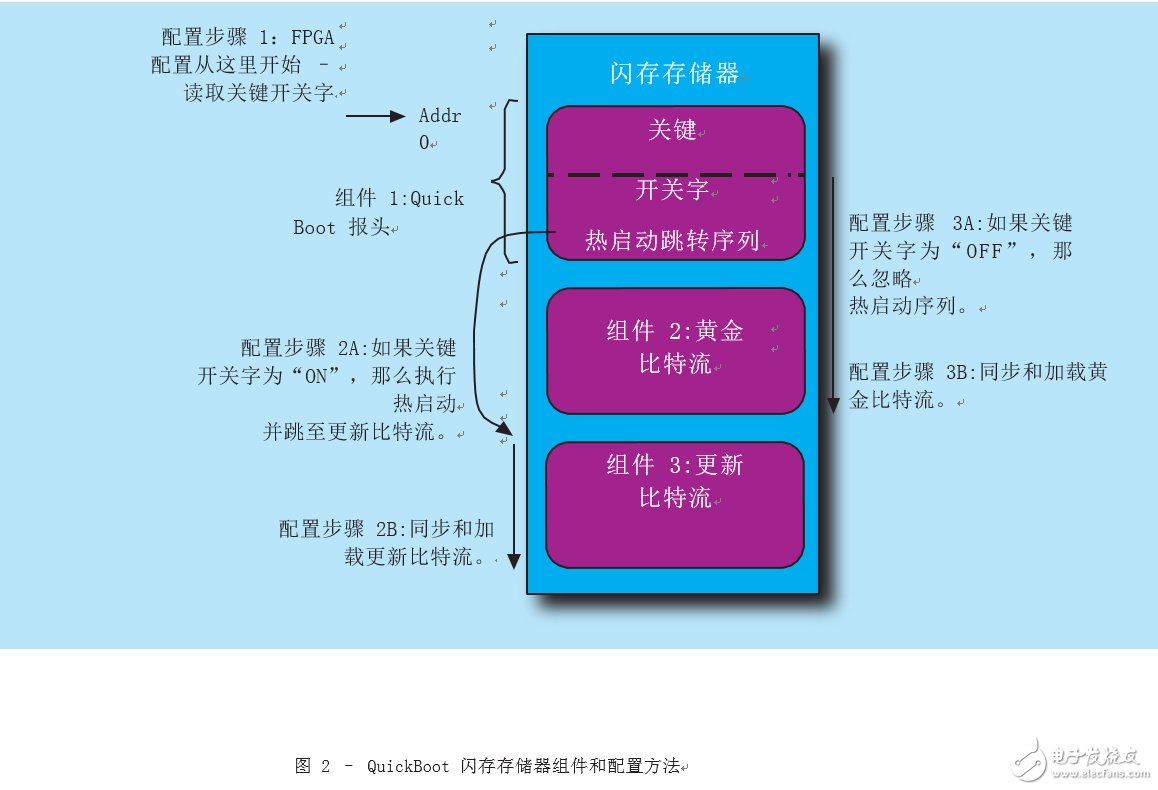

我们通过实现赛灵思应用指南 XAPP1081介绍的和图 2 中总结的 QuickBoot 黄金镜像固件升级架构与流程,解决了这个问题。传统7 系列回读多重启动解决方案采用的启动过程可保持已知正确的“黄金”镜像,在配置闪存存储器中包含比特流。在更新过程中,更新的“工作”镜像在“黄金”镜像之后载入存储器。如果更新过程失败或者“工作”镜像损坏,FPGA会自动检测错误并回读至“黄金”镜像。XAPP1081 Quick-Boot 方法进一步扩展该过程,使其具备更完善的配置时间和“黄金”镜像更新特性。

在该项目成功的基础之上,我们进一步展望下一代赛灵思器件将如何为Anritsu 产品实现更多功能。例如,大量的功耗预算被片外 SDRAM 互联占用。我们期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 来减少或消除该负载,或许可以在应用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 产品线。

如需了解更多信息,敬请联系:更新过程中,更新的“工作”镜像在“黄金”镜像之后载入存储器。如果更新过程失败或者“工作”镜像损坏,FPGA会自动检测错误并回读至“黄金”镜像。XAPP1081 Quick-Boot 方法进一步扩展该过程,使其具备更完善的配置时间和“黄金”镜像更新特性。

在该项目成功的基础之上,我们进一步展望下一代赛灵思器件将如何为Anritsu 产品实现更多功能。例如,大量的功耗预算被片外 SDRAM 互联占用。我们期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 来减少或消除该负载,或许可以在应用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 产品线。

如需了解更多信息,敬请联系作者:更新过程中,更新的“工作”镜像在“黄金”镜像之后载入存储器。如果更新过程失败或者“工作”镜像损坏,FPGA会自动检测错误并回读至“黄金”镜像。XAPP1081 Quick-Boot 方法进一步扩展该过程,使其具备更完善的配置时间和“黄金”镜像更新特性。

在该项目成功的基础之上,我们进一步展望下一代赛灵思器件将如何为Anritsu 产品实现更多功能。例如,大量的功耗预算被片外 SDRAM 互联占用。我们期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 来减少或消除该负载,或许可以在应用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 产品线。

-

Artix-7 FPGA:成本优化器件中的性能和带宽2023-09-18 678

-

Artix-7 FPGA数据表下载2021-05-21 1312

-

如何减轻SEU对Artix-7 FPGA的影响2020-07-14 2342

-

digilent Nexys 4:Artix-7 FPGA训练板介绍2019-11-14 9836

-

Artix-7 FPGA AC701 评估套件产品描述2019-07-31 3639

-

Artix-7 ARTY FPGA评估套件的演示2018-11-29 3560

-

有着最高DSP带宽的Artix-7 A100T FPGA器件介绍2018-11-27 5595

-

如何使用Artix-7 FPGA减少功耗2018-11-21 4482

-

Xilinx的Artix-7 FPGA AC701评估套件专门支持高性能系统2018-09-26 2830

-

Artix-7 DSP性能演示2018-06-05 5320

-

Artix-7 功耗优势演示2018-06-04 5528

-

【Artix-7 50T FPGA试用体验】xilxin Artix-7 系列FPGA相关特性2016-11-01 7452

-

Xilinx Artix-7系列FPGA教程资料及设计实例_Artix 7开发板电路图和例程2016-08-04 23387

-

利用 Artix-7 FPGA 设计高性能 USB 器件2016-07-27 3447

全部0条评论

快来发表一下你的评论吧 !