DRAM芯片的基本结构

描述

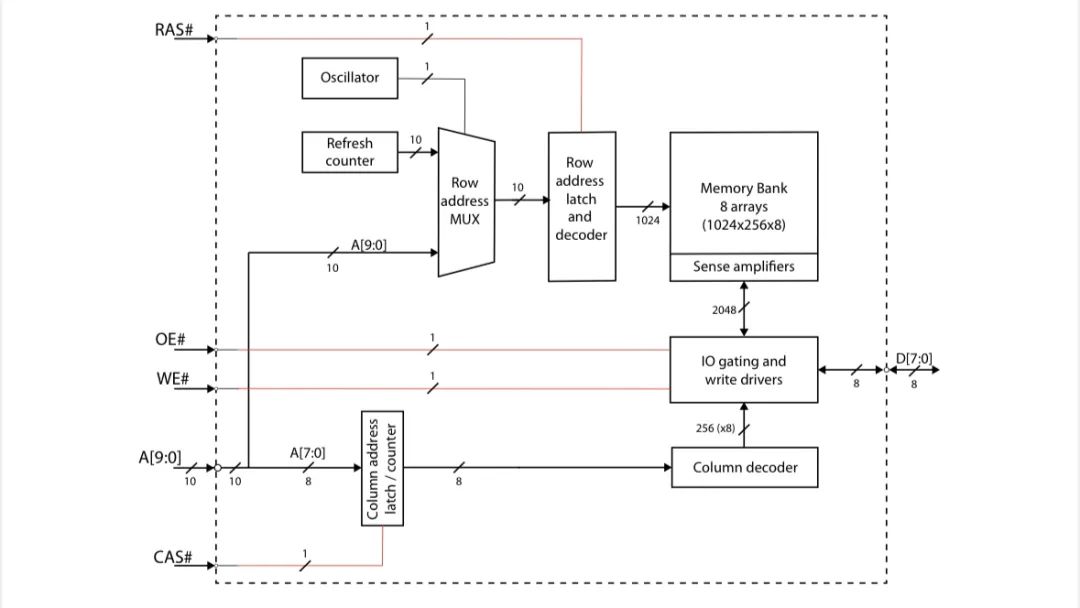

如果内存是一个巨大的矩阵,那么DRAM芯片就是这个矩阵的实体化。如下图所示,一个DRAM芯片包含了8个array,每个array拥有1024行和256列的存储单元。

当访问这些存储单元时,芯片可以一次性读取或传输8个比特(D0到D7)。这个过程涉及到两个关键的组件:行地址解码器和列选择器。行地址解码器负责激活与给定行地址对应的字线,而列选择器则用于从给定的列地址中选择正确的列。

地址线的复用

由于DRAM的容量巨大,如果直接为每一行和每一列分配地址线,那么所需的地址线数量将会非常庞大。例如,在一个32256行1024列的array中,我们需要15位来选择一个字,10位来选择一个列。为了解决这个问题,地址线采用了复用技术。首先,行地址被应用到地址线上,然后是列地址。这样,所需的地址引脚数量几乎减半。

控制信号的作用

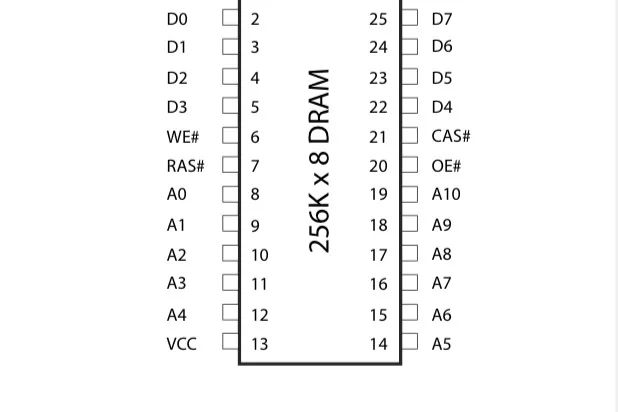

在数据传输过程中,还需要两个额外的控制信号来指示当前总线上是哪种地址:行访问选通row access strobe(RAS)和列访问选通column access strobe(CAS)。当RAS信号被激活时,地址位A0到A9被锁存到行地址锁存器中。类似地,当CAS信号被激活时,地址位A0到A7被锁存到列地址锁存器中。

此外,还需要两个控制信号来正确地将数据传输到DRAM芯片或从芯片中读取数据。写使能(WE)信号用于选择读或写操作。低电平表示需要写操作;高电平则用于选择读操作。

在读操作期间,输出使能(OE)信号用于防止数据在需要之前出现在输出端。当OE为低时,数据一旦可用就会出现在数据输出上。在写操作期间,OE则需要一直保持高电平。

最后,让我们来澄清一个常见的误解:许多人认为内存在物理上是可以以线性向量的形式组织的,而不是以行和列的矩形阵列。实际上,这种组织方式在理论上可能是理想的,但在物理上却是不可能的。因为如果内存以这种方式组织,位线会非常长,电容也会非常大,这将使得检测微小的电压变化变得不可能,也就是无法判断电容存储的是0还是1。

-

DRAM芯片选型,DRAM工作原理2026-01-30 842

-

堆叠式DRAM存储节点相关部分的结构分析2023-09-08 4760

-

DRAM原理 - 1.存储单元阵列#DRAMEE_Voky 2022-06-28

-

DRAM芯片中的记忆单元分析2022-03-02 2538

-

LPDDR5 DRAM芯片的性能及应用是什么?2021-06-26 2005

-

DRAM:产业结构变化孕育中国玩家进场良机2021-03-17 1216

-

DRAM存储原理和特点2020-12-10 5342

-

DRAM 原理 2 :DRAM Memory Organization2017-03-17 5784

-

【内存知识】DRAM芯片工作原理2010-07-15 9555

-

基于SRAM和DRAM结构的大容量FIFO的设计与实现2010-02-06 954

-

DRAM的总体结构框图2009-12-04 3963

全部0条评论

快来发表一下你的评论吧 !