FL60D2GF225及demo板介绍

描述

FL60F225D2G器件简介

FL60F225D2G 采用 System in Package(SiP)封装方式,相对于Ti60F225内部增加了一颗DDR3L。基于易灵思 Quantum架构的 16nm Ti60 FPGA 芯片,FL60F225D2G FPGA 具有高密度、低功耗特点; FL60F225D2G 支持易灵思 MIPI CSI-2 和 DSI控制器一起使用,支持多路摄像头,高带宽视频应用,边缘计算和硬加速系统等。同时 FL60F225D2G 支持 DDR3L IP 接口和集成了 DDR3L 颗粒。使用FL60F225D2G 低功耗产品,设计者可以构建持续不断的产品,为视觉系统、边缘计算、硬加速和机器学习等应用程序提供增强的功能。

特性

● 高密度、低功耗的 Quantum 架构;

● 台积电 16nm 工艺;

● 10Kbit 高速嵌入式 SRAM,可配置为单端 RAM、伪双端 RAM、真双端RAM 或者 ROM;

● DDR3L SDRAM 支持 2Gbit,800Mbps,16bit 位宽的应用(F225 封装);

● 高性能的 DSP 块,用于乘法、加法、减法、累积以及 15 位可变右移寄存器;

● 多功能芯片时钟性能:-支持 32 个时钟或控制信号的低偏斜全时钟网络-支持局部和本地时钟网络-PLL 支持

● FPGA 接口模块:

-DDR3L PHY(支持 16bit DQ 位宽)软控制器 IP

-高压 IO(HVIO)(1.8V、2.5、3.3V)-高速 IO (HSIO)可以配置为:

--LVDS、subLVDS、Mini-LVDS 和 RSDS(RX、TX 和双向),高达 1.5 Gbps

--高速(HS)低功率(LP)模式下的MIPI lane I/O(DSI和CSI),高达1.5 Gbps--单端I/O和差分I/O-PLL-振荡器

● 灵活的设备配置:-标准 SPI 接口(主动、被动和菊花链)

-JTAG 接口-支持内部重新配置(多镜像)

● 单事件干扰(SEU)检测功能

● Efinity 软件(RTL 到比特流编译器)全程支持

● 可选的安全功能:-使用 RSA-4096 进行的非对称位流认证

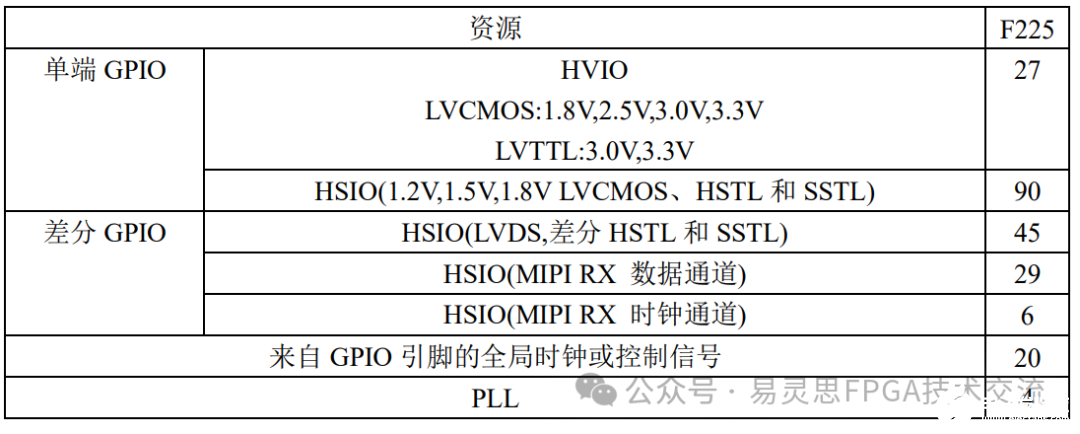

FL60F225D2G 封装相关资源:

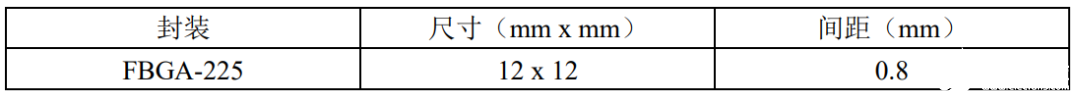

封装信息如下:

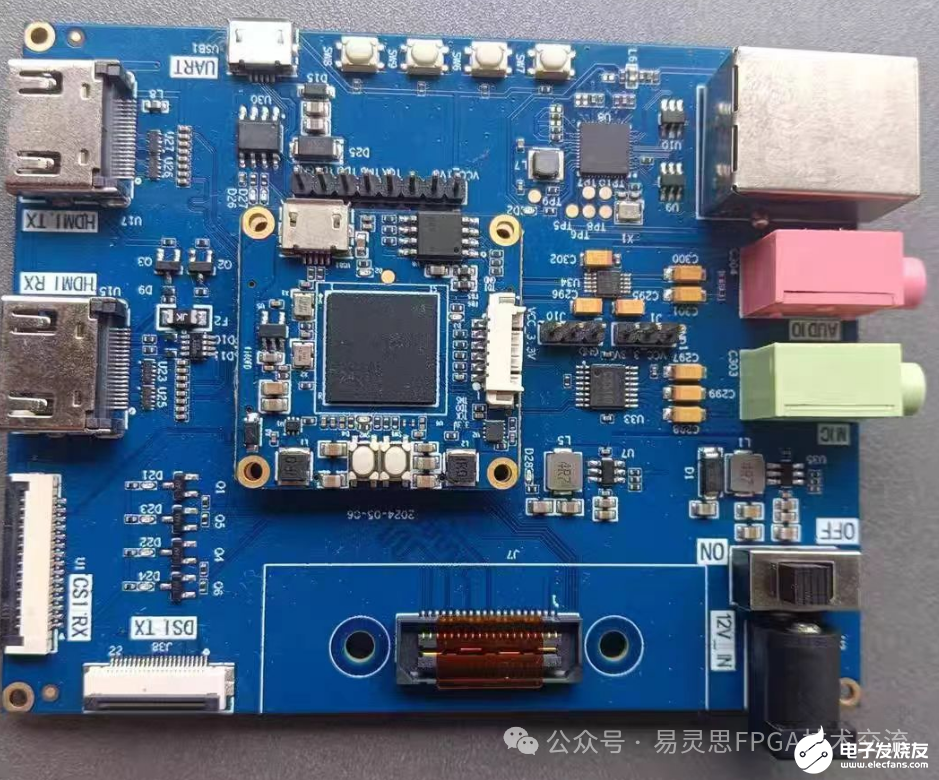

demo板概述

FL60D2GF225-DK采用的是易灵思的FPGA为核心的开发验证平台。它采用核心板与底板分离的方式。核心板主要是FL60D2GF225加flash。

支持接口:

(1)HDMI收发,HDMI通过FPGA高速IO实现,最高可达到1080@60Hz;

(2)GE口、GE口都可以实现3速

(3)音频处理接口及

(4)MIPI CSI接收及DSI显示。

(5)并预留了一个QSE座子用于扩展IO和验证MIPI接口。

(6)板上的flash是16MB,采用的是W25Q64JWSSIQ,用于存储FPGA镜像,也可以存储用户数据。

(7)串口;

(8)6个用户按键,6个用户指示灯;

审核编辑 黄宇

-

ISL8117DEMO2Z 演示板:高效电源解决方案的详细剖析2026-04-13 89

-

请问谁知道TPA3138D2这款功放有EVM板(Demo)吗2024-10-09 400

-

创智辉无线充DEMO板jf_63984471 2023-10-31

-

KUU 肖特基 KDFLS260-7 SOD-123FL2022-09-23 452

-

【Si24R2F+ Demo板】介绍说明与使用建议2022-04-22 3957

-

直流屏充电模块GF22007-2电源模块介绍2021-12-29 1491

-

优势供应申泰物料QMS-026-05.75-H-D-A-RT1、QTS-050-01-F-D-LC、S1SDT-05-28-GF-14.00-L12021-02-18 1054

-

AMLOGIC A311D开发板demo板2020-04-08 16187

-

适用于MC9S08DZ60微控制器的DEMO9S08DZ60,S08D系列演示板2019-04-11 2854

-

Flash-Net Demo演示板的资料介绍和入门实验教程2018-09-26 1221

-

GD32F105VCT6 Demo板资料2017-11-22 2534

-

GD32F103ZET6 Demo板资料2017-11-21 1714

-

GD32F403VKT6_Demo板资料包2017-11-17 978

-

ZLG I2C及UART器件DEMO板简介2010-03-09 867

全部0条评论

快来发表一下你的评论吧 !