接触刻蚀阻挡层应变技术介绍

描述

SMT仅仅是用来提高NMOS 的速度,当工艺技术发展到45nm 以下时,半导体业界迫切需要另一种表面薄膜层应力技术来提升PMOS 的速度。在SMT技术的基础上开发出的接触刻蚀阻挡层应变技术(Contact Etch Stop Layer,CESL),它是利用Si3N4产生单轴张应力来提升 NMOS 速度和单轴压应力来提升[110]晶向上PMOS速度的应变技术。该应变技术仅适用于45nm 及其以下工艺的短沟道器件,长沟道几乎不会获得好处。

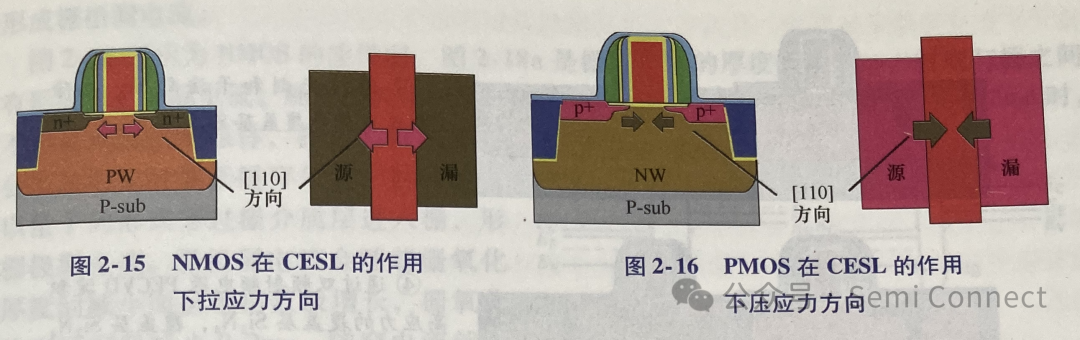

如图2-15所示,与应力记忆技术类似,接触刻蚀阻挡层应变技术也是利用覆盖层 Si3N4会在沟道[110]方向产生单轴的张应力,从而减小沟道方向的电子电导有效质量和散射概率,提高 NMOS的速度。

如图2-16所示,对于PMOS,接触刻蚀阻挡层应变技术是利用覆盖层 Si3N4在PMOS沟道[110]方向产生单轴的压应力,该方向上的压应力可以使价带能带发生分裂,重空穴带离开价带顶,轻空穴带占据价带顶,从而减小沟道方向的空穴的电导有效质量,提高PMOS的速度。

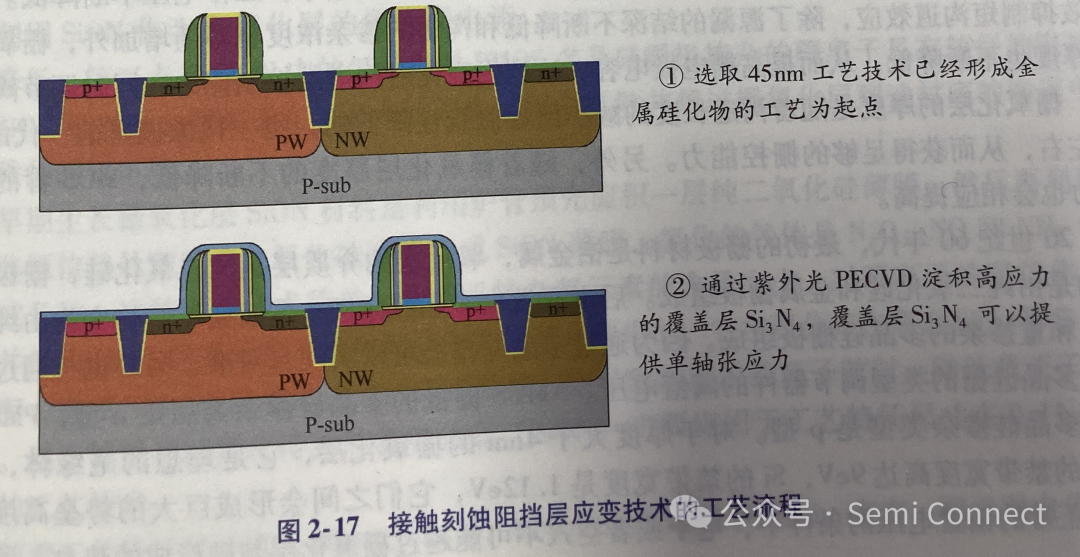

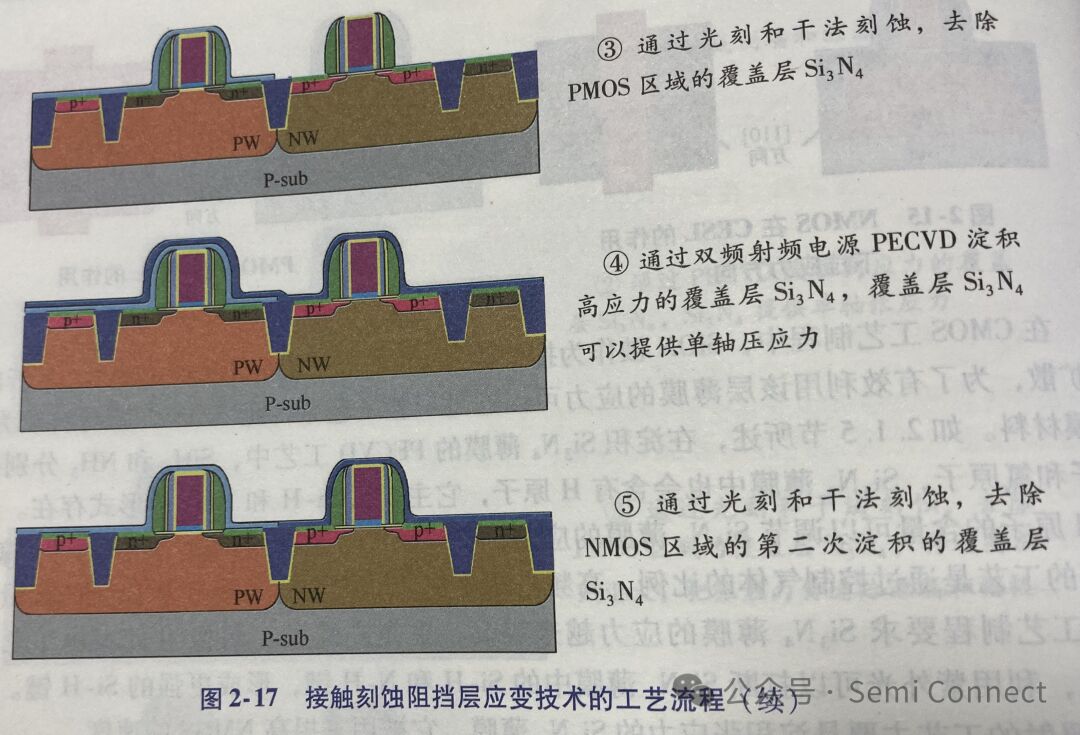

在CMOS 工艺制程中,SiON 被作为接触孔刻蚀阻挡层和防止 BPSG中的B、P析出向衬底扩散,为了有效利用该层薄膜的应力可以通过调整工艺条件把SiON 薄膜材料改为 Si3N4薄膜材料。如2.1.5节所述,在淀积 Si3N4薄膜的 PECVD工艺中,SiN4和NH3分别提供硅原子和氮原子, Si3N4薄膜中也会含有H 原子,它主要以Si-H和N-H的形式存在。通过改变H原子的含量可以调节Si3N4薄膜的应力,H原子的含量越高Si3N4薄膜的应力就越小,早期的工艺是通过控制气体的比例、高频电源功率和反应温度来调节H 原子的含量,但是随着工艺制程要求Si3N4薄膜的应力越来越高,更先进的工艺制程中引入紫外光照射条件,利用紫外光可以打断Si3N4薄膜中的Si-H和N-H 键,形成更强的Si-H键。利用紫外光照射的工艺主要是淀积张应力的Si3N4薄膜,它被用来提高 NMOS 的速度。

与淀积张应力的Si3N4薄膜不同,可以利用双频射频电源的PECVD淀积压应力的Si3N4薄膜,双频射频电源是指它包含高频射频电源和低频电源。淀积压应力的Si3N4薄膜的气体源除了包含SiN4和NH3外,还包含H2和Ar(或者N2)。利用高频射频电源可以电解重原子气体 Ar,形成Ar+等离子体(或者称为 Plasma),再利用低频电源加速 Ar+离子形成高能离子体,然后利用高能离子的体轰击效应,使得Si3N4薄膜更为致密,形成压应力。

图2-17所示为接触刻蚀阻挡层应变技术的工艺流程。

-

详解原子层沉积薄膜制备技术2025-05-14 1744

-

芯片制造中的阻挡层沉积技术介绍2025-05-03 3911

-

非接触式应变测量技巧2009-04-02 13345

-

13um应变补偿多量子阱SLD台面制作工艺的研究2009-10-06 3844

-

【转帖】干法刻蚀的优点和过程2018-12-21 5727

-

请教碳化硅刻蚀工艺2022-08-31 41987

-

ITO玻璃技术之SiO2阻挡膜层规格2008-10-25 2179

-

具有带有阻挡层的半导体衬底的集成电路2011-11-22 901

-

晶片清洗、阻挡层形成和光刻胶应用2022-03-15 1569

-

一文了解金属互连中阻挡层2024-12-05 4983

-

什么是原子层刻蚀2025-01-20 1732

-

半导体boe刻蚀技术介绍2025-04-28 7371

-

为什么LED芯片正电极要插入二氧化硅电流阻挡层,而负极没有?2025-07-14 1273

-

TSV制造技术里的通孔刻蚀与绝缘层2025-08-01 2605

全部0条评论

快来发表一下你的评论吧 !