缩小阻抗差距,解决PCB传输线之SI反射问题

PCB

描述

1. SI问题的成因

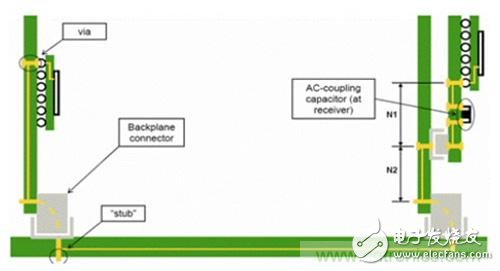

下图所示是一个典型的高速信号互连链路,信号传输路径包括:①发送端芯片(封装与PCB过孔)②子卡PCB走线③子卡连接器④背板PCB走线⑤对侧子卡连接器⑥对侧子卡PCB走线⑦AC耦合电容⑧接收端芯片(封装与PCB过孔)

图1.典型高速信号互连链路

可以看出,实际电子产品的高速信号互连链路是比较复杂的,而且通常在不同部件连接点处是会产生阻抗失配的问题、从而造成信号的发射。

高速互连链路常见的阻抗不连续点:

(1)芯片封装:通常芯片封装基板内的PCB走线线宽会比普通PCB板细很多,阻抗控制不容易;

(2)PCB过孔:PCB过孔通常为容性效应,特征阻抗偏低,PCB设计最应该关注与优化;

(3)连接器:连接器内铜互连链路的设计要同时受到机械可靠性与电气性能的双重影响,在两者之间寻求平衡;

PCB走线反而一般情况下阻抗控制比其他互连部件更容易,重点关注层叠设计、板材选择,但通常PCB加工板厂的阻抗控制公差为10%,要达到5~8%的阻抗公差控制往往需要花费更高的加工成本。

2. 传输线反射基础理论

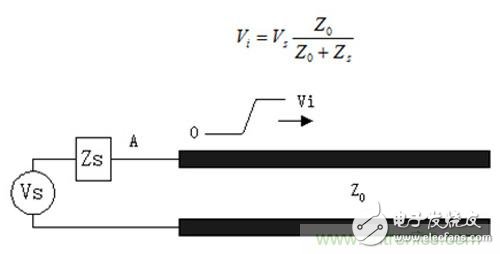

当驱动器加信号到传输线时,信号的幅度依赖于驱动器的电压与电阻和传输线阻抗。驱动器上的初始电压通过自身电阻和传输线阻抗的分压来控制。

下图描绘了加在长的传输线上的初始波形,初始的电压Vi传送到传输线上直到到达末端,Vi的幅度通过驱动器电阻和传输线阻抗的分压来决定:

图2.信号波形在长传输线的传播

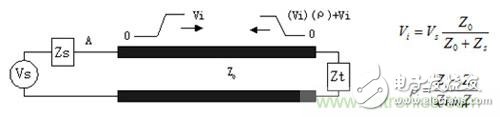

如果传输线的末端端接一个阻抗,而且这个阻抗与线的阻抗精确的匹配,那么幅度为Vi的信号将被端接到地,电压Vi将仍保持在线上直到信号源转换。在这种情况下Vi是dc稳态值。否则,如果传输线的末端的阻抗不是线的特征阻抗,信号的一部分端接到地,信号的其余部分将被反射到传输线回到源。反射回的信号的量通过反射系数决定,反射系数由确定的点的反射电压和输入电压的比决定。这个点定义为传输线上阻抗不连续。阻抗不连续可以是不同特征阻抗的传输线的一部分,也可以是端接电阻或者是到芯片缓冲器上的输入阻抗。

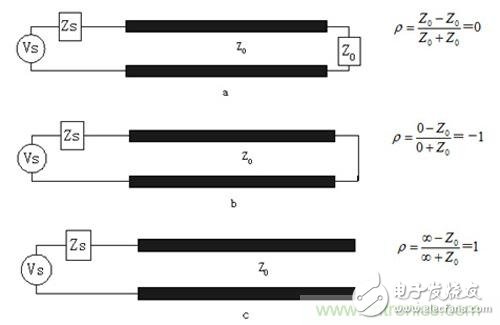

反射系数的计算:

其中Z0为传输线标准阻抗,Zt为传输线上某个不连续点的阻抗。

等式假设信号在特征阻抗为Z0的传输线上传送遇到了不连续的阻抗Zt。注意如果Z0=Zt,反射系数为0,意味着没有反射。Z0= Zt这种情况就称为匹配的端接。

如下图所示当输入波形遇到端接Zt,信号的一部分Viρ被反射回源端并且加在输入波形上,整个输入信号波形幅度为Viρ+Vi。反射的部分可能从源产生另一个反射,反射和逆反射一直持续直到传输线稳定。

图3.阻抗不匹配情况下的信号反射

当传输线完全匹配、短路、开路时的反射系数如下图所示:

图4.(a)端接(b)短路(c)开路 三种情况下的反射系数

在实际应用的互连链路中,理想的传输线是不存在的,也不可能存在完全匹配,因此信号的反射是必然存在的,设计的关键在于如何把互连链路中的各个部件阻抗差距尽量缩小,从而减小反射信号幅度、避免多级反射对信号质量造成致命影响。

-

信号完整性(SIPI)学习—传输线的阻抗2023-06-14 12226

-

什么是传输线阻抗?两种传输线结构的阻抗计算公式2021-04-12 28640

-

如何避免传输线出现反射2020-11-03 1325

-

高速PCB设计中传输线的概念及结构分析2019-12-16 8070

-

PCB传输线SI传输问题怎样解决2019-10-13 4521

-

PCB传输线之SI反射的问题怎样来解决2019-08-27 1609

-

请问为什么很多PCB传输线的阻抗都是50欧姆?2018-11-27 8551

-

PCB传输线之SI反射问题的解决2018-09-21 1925

-

信号传输线及其特性阻抗2018-02-08 4951

-

传输线的特性阻抗2017-12-29 2698

-

快点PCB原创∣SI问题之反射2016-09-28 2757

-

pcb layout培训基础之传输线的特性阻抗2011-11-21 6020

-

传输线的特性阻抗分析2009-09-28 9618

-

传输线效应2009-06-18 3649

全部0条评论

快来发表一下你的评论吧 !