MCXA153系列MCU正交解码模块的特点和应用示例

描述

全新的MCX A系列融合了恩智浦通用MCU的特点,适用更为广泛的通用应用,实现了低成本,低功耗,高安全性和高可靠性。

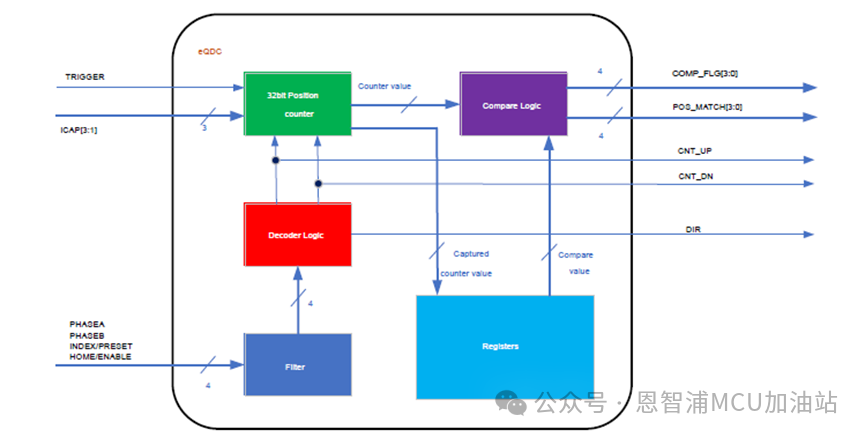

针对工业方面的应用需求,很多需要提供对编码器的支持,全新MCX A系列MCU集成了片上eQDC模块,新版的eQDC模块在以往强大功能的基础上又进行了升级。具体框图如下所示:

图1 eQDC模块框图

eQDC的功能概述

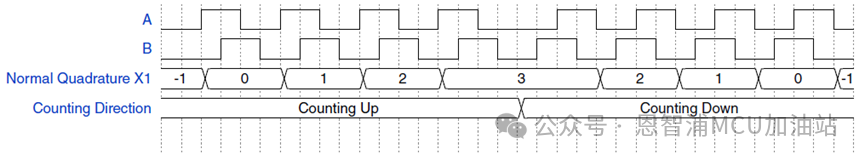

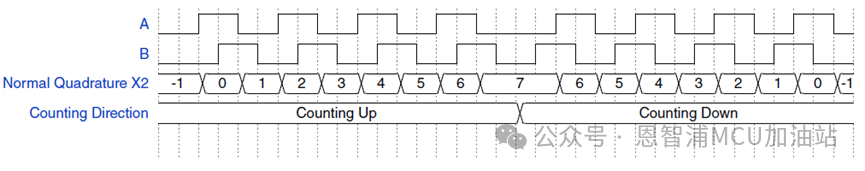

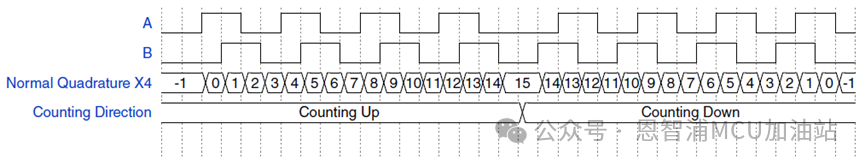

eQDC是专门针对于正交编码器进行正交解码的外设模块,其包含了一个用于正交解码的32位计数器,使其能够适用于超高线数编码器。具有专门用于转速检测的位置差计数器、位置差时间计数器与边沿时间计数器,因此能够很容易完成转速的关键信息测量。同时还具有可用于进行位置伺服控制的转数计数器。正交编码器目前支持X1,X2,X4工作模式。

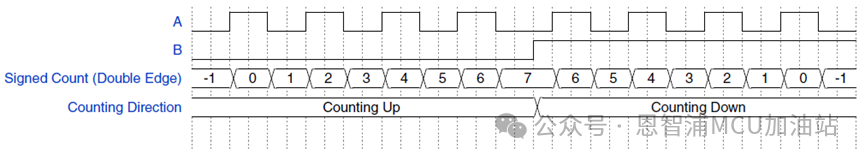

图2 正常正交编码X1 模式

图3 正常正交编码X2 模式

图4 正常正交编码X4 模式

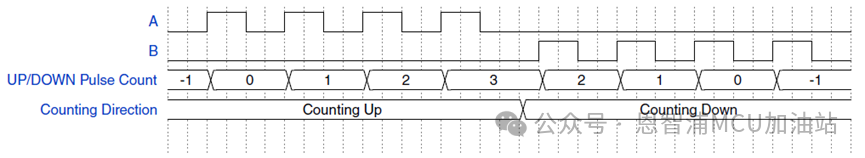

MCX A系列所集成的eQDC模块,计数模式非常灵活,除了支持传统的正交编码器信号输入,也支持常规伺服脉冲输入信号,例如方向/脉冲信号输入和CM/CCM信号输入。对于这类信号的处理,传统方式需要通过FPGA来实现,eQDC模块的增强功能能够有效支持这类计数模式,大大扩展了eQDC的应用范畴。

图5 方向/脉冲计数模式

图6 CM/CCM计数模式

MCX A系列所集成的eQDC模块,除了可以支持常规的正交编码器输入信号,如PHASHEA,PHASHEB,INDEX,HOME等信号,还支持多个外部输入信号,例如可以通过ICAP[3:1]对应的IO信号输入,有效捕获并锁存具体位置点的32位位置计数值(POS),并且对于外部输入信号,也可以通过配置所搭载的Glitch Filter,有效滤除输入信号中的干扰。

eQDC模块也支持多种事件信号输出,如用户内部预设计数值与当前位置计数寄存器(POS)值匹配的时候,POS_MATCH[3:0]信号输出有效。当用户设定比较值功能的时候,则在当前位置计数寄存器(POS)值符合相应的比较条件时,COMP_FLG[3:1]信号输出有效,此外还有DIR信号可配置为输出当前计数增减方向。

eQDC模块内部也集成了16位的旋转转数计数器,有效记录正反转的累积圈数。对伺服位置控制有较大用处。

eQDC的测速方法

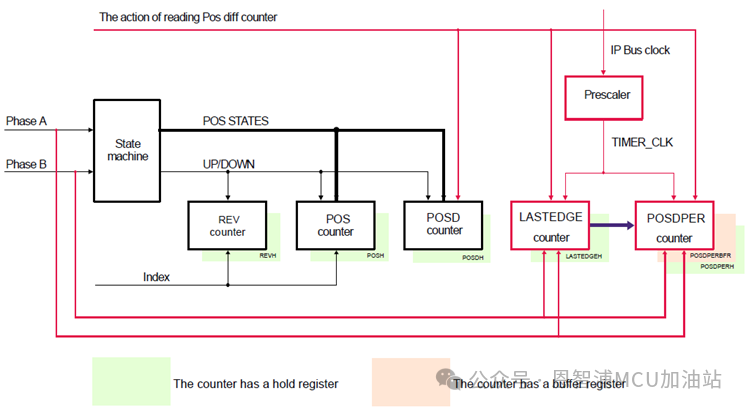

图7eQDC的计数框图

针对eQDC模块测量速度的方案可以使用M/T法为例,正交解码模块中有五种不同的计数器,其中POSDH、POSDPERH作为关键寄存器可直接用于提取软件测速周期间隔之间的脉冲边沿数,及与此对应的脉冲边沿间的高频时钟计数。

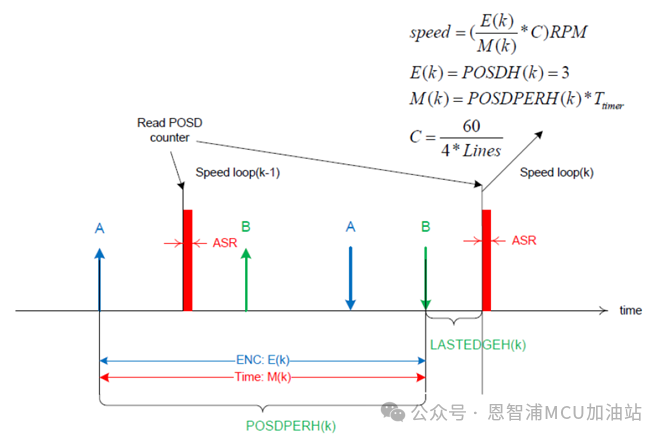

图8eQDC的M/T法测速原理

图中A,B为编码器正交脉冲边沿,下面给出了寄存器在进行测速时的计数方式,POSD寄存器能够准确读出在两个POSD读取指令间脉冲边沿计数,POSDH寄存器能够获得两次POSD读取之间的脉冲边沿计数(对应图中E(k),用于距离测量),而LASTEDGEH寄存器代表了上一编码器脉冲边沿至POSD读取时刻间的高频时钟计数,用于补偿高频脉冲计数时间。

在进行POSD读取的T1(图中speed loop(k-1))时刻,将此时LASTEDGEH值作为POSDPER重新开始计数的初值。而后每次出现脉冲边沿都将POSDPER当前值暂存到POSDPERBFR寄存器,直到下一次POSD读取的T2(图中speed loop(k))时刻,POSDPERBFR寄存器值存入POSDPERH保持寄存器,该值代表两次POSD读取前的脉冲边沿之间的高频时钟计数(对应图中M(k),用于时间测量)。由此获得的时间和距离可根据公式计算得到当前速度。

今天为大家带来MCXA153系列MCU正交解码模块的特点和应用示例,更多详细信息可访问恩智浦官网查看最新的MCXA微处理器数据手册。

-

NXP MCXA153、A152、A143、A142 MCU深度解析:工业与消费物联网的理想之选2025-12-24 806

-

恩智浦MCXA343和MCXA344通用MCU产品介绍2025-10-22 2843

-

恩智浦FRDM-MCXA153 RT-Thread开发实战(六):I2C总线开发与应用2024-11-21 2975

-

基于NXP MCXA153 MCU实现RT-Thread的MTD NOR Flash驱动2024-11-09 1961

-

NXP FRDM-MCXA153 RT-Thread实践指南之UART介绍2024-10-18 1710

-

MCXA153 MCU的系统启动2024-08-01 2320

-

基于MCXA153 MCU的电机控制方案2024-07-16 1767

-

恩智浦MCU解读 MCX A系列微处理器之时钟架构2024-06-20 1322

-

恩智浦MCX A系列微处理器之供电系统2024-06-13 2483

-

FRDM-MCXA153开发板的开箱体验2024-02-25 2509

-

如何使用QTIMER模块来实现正交解码2021-11-23 542

-

什么是正交解码如何使用STM32单片机实现正交解码2019-05-16 1624

-

stm32正交解码2016-05-12 4429

全部0条评论

快来发表一下你的评论吧 !