三态逻辑电路的工作原理及其四种三态缓冲器介绍

描述

文章概述

三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对三态逻辑感兴趣,相信这篇内容会让你对其有基础的认识。

三态逻辑输入/输出

在数字电子技术中,三态逻辑(TRIS)允许输入或输出假设为1、0或 高阻抗状态 (开路)。

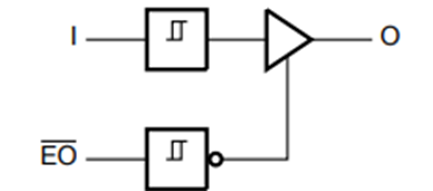

一个缓冲器三态图

三态输入

可以检测引脚是否为逻辑1、0或未连接(开路)。

三态输出

允许多个电路共享相同的输出线。如果有多个设备与另一个设备电连接,则通常会将输出置于Hi-Z态以防止短路,例如当一个设备输出高电平(逻辑1)而另一个设备输出低电平(逻辑0)时。

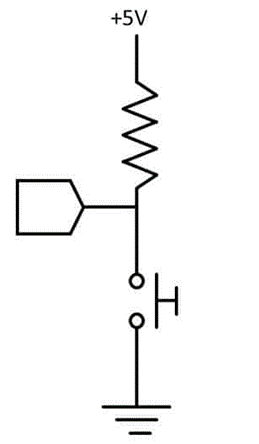

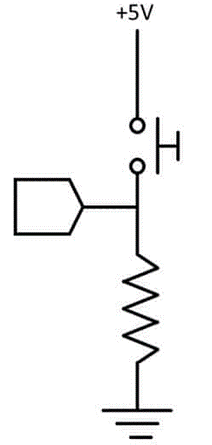

当输出为三态(处于Hi-Z状态)时,它们对电路其余部分的影响将被消除,如果没有其他电路元件能够决定其状态,则电路节点将为“浮动”状态。电路设计人员通常会使用上拉 或 下拉电阻 (通常在1-100kΩ范围内)来影响当输出为三态时的电路。

上拉电阻

下拉电阻

三态逻辑还可以减少驱动一组LED所需的电线数量(三态多路复用或查理复用)。

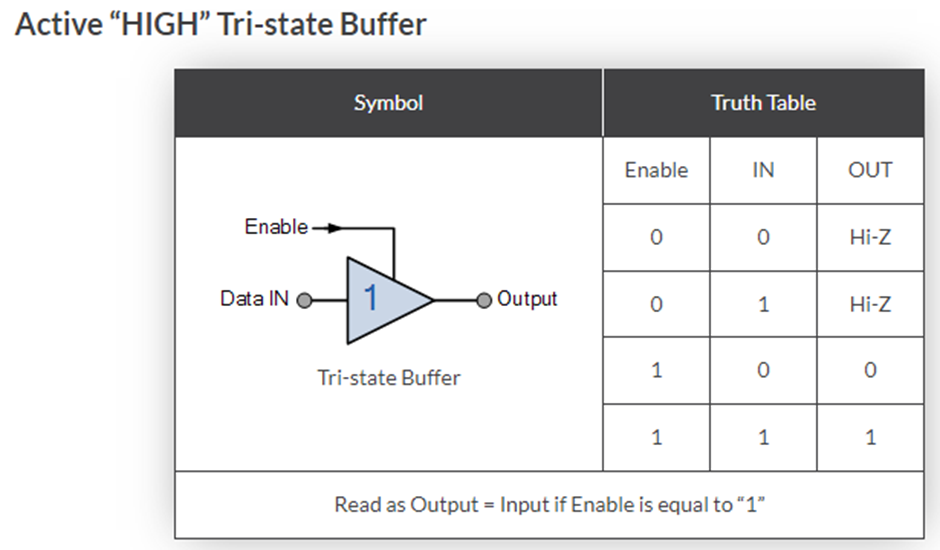

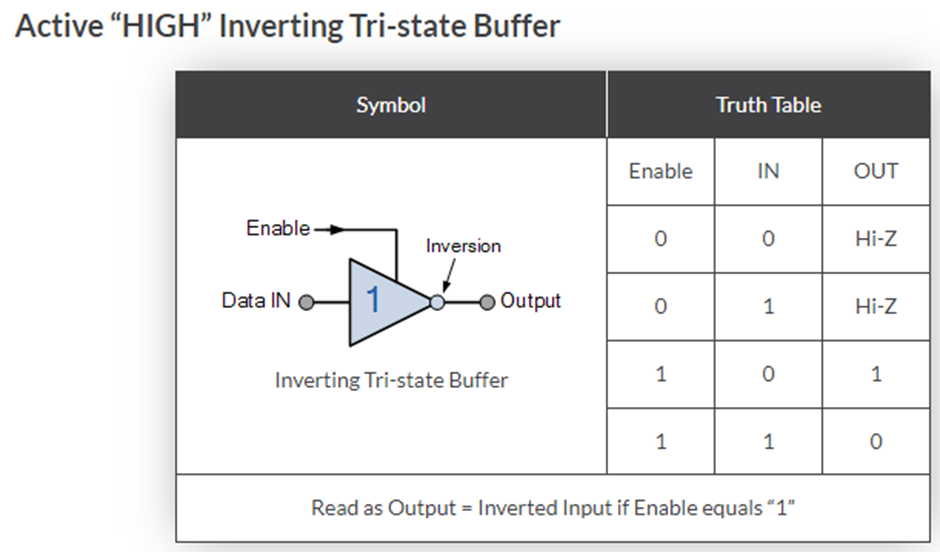

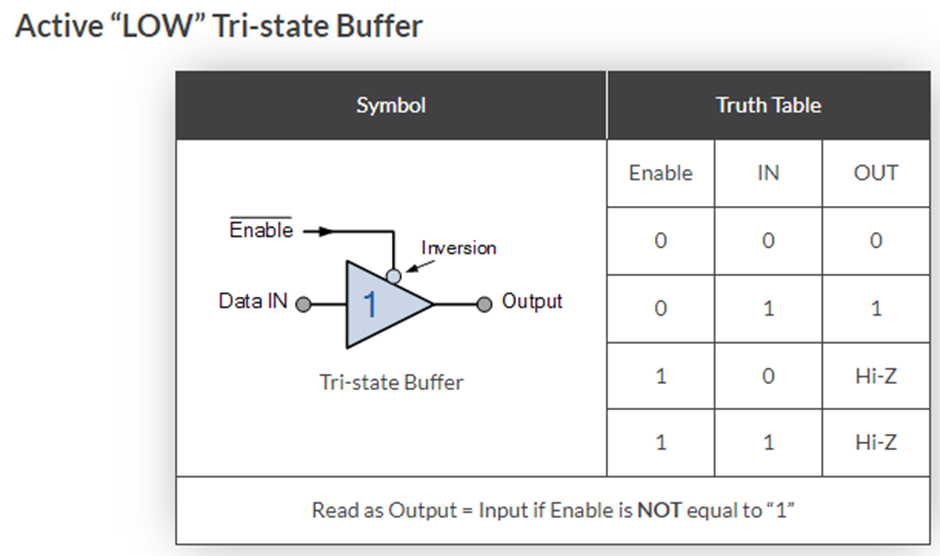

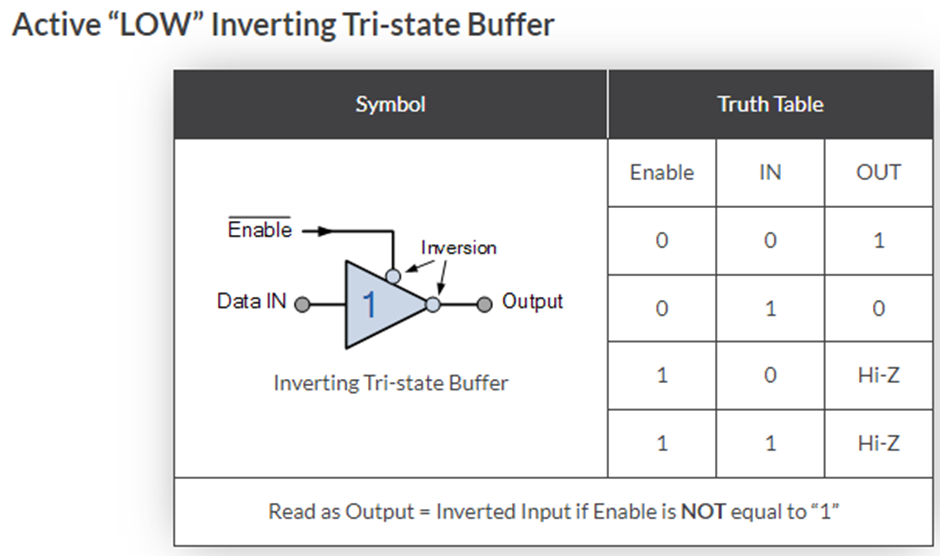

四种三态缓冲器

共四种不同类型的三态缓冲器,一组是通过“ 高电平有效 ”控制信号启用或禁用输出,从而产生逆向或非逆向输出,另一组是通过“ 低电平有效 ”控制信号来控制缓冲器输出,从而产生逆向或非逆向输出,如下所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三态缓冲器的工作原理和应用2024-08-02 9769

-

三态缓冲器的三种状态分别是什么2024-06-27 2478

-

三态输出的缓冲器有哪些用途?2023-09-21 4907

-

[6.3.1]--6.4三态缓冲器李开鸿 2022-11-13

-

怎样去设计一种CMOS三态缓冲器的电路呢2021-10-20 2968

-

三态缓冲器测试的Multisim仿真实验原理图免费下载2020-09-09 1519

-

三态缓冲器工作原理2018-10-24 35763

-

三态门逻辑电路图大全(三款三态门逻辑电路图)2018-03-01 81575

-

三态缓冲器介绍_三态缓冲器逻辑符号2018-01-11 16293

-

PSoC 4 三态缓冲器 Bufoe2017-10-10 847

-

三态缓冲器介绍2015-11-16 1474

-

PSoC 4 三态缓冲器 (Bufoe) 1.102013-07-03 4271

-

三态逻辑笔电路图2009-04-07 2397

全部0条评论

快来发表一下你的评论吧 !