思尔芯赛题正式发布,邀你共战EDA精英挑战赛!

描述

赛题发布

COMPETITION RELEASE

2024中国研究生创芯大赛·EDA精英挑战赛(原“集成电路EDA设计精英挑战赛”)现已正式拉开帷幕。作为核心出题企业之一思尔芯(S2C),已经为你们准备了全新的挑战。

今年的赛题,我们更加聚焦于数字集成电路设计的核心领域,直击当前超大规模设计下硬件仿真的技术难点:设计并优化一种高效的超图分割算法。该技术可以加速设计验证流程,提升整体设计效率与质量。这不仅是对你们算法设计的考验,也是对你们在EDA相关领域知识、程序编写与调试技巧的全面挑战。

并肩作战,共创辉煌!

在这场充满智慧与激情的竞技场上,你并不孤单。思尔芯的专家团队已整装待发,他们拥有丰富的行业经验和深厚的专业知识,将全程陪伴在每一位选择思尔芯赛题的参赛者身边,解答疑惑,提供指导,助力你们攀登技术高峰,迈向荣耀之巅。

时不我待,火速行动!

暑期时光匆匆流逝,正是我们挥洒汗水、追逐梦想的最佳时机。不要再犹豫,不要再等待,是时候将你的创意与才华投入到这场充满挑战与机遇的赛事中来。

我们相信,每一位参赛者都拥有无限的潜力与可能,期待你们的表现,挑战自我,突破极限,展现出令人瞩目的杰出表现!

01

赛题名称

考虑逻辑复制的超图分割算法设计

02

赛题背景

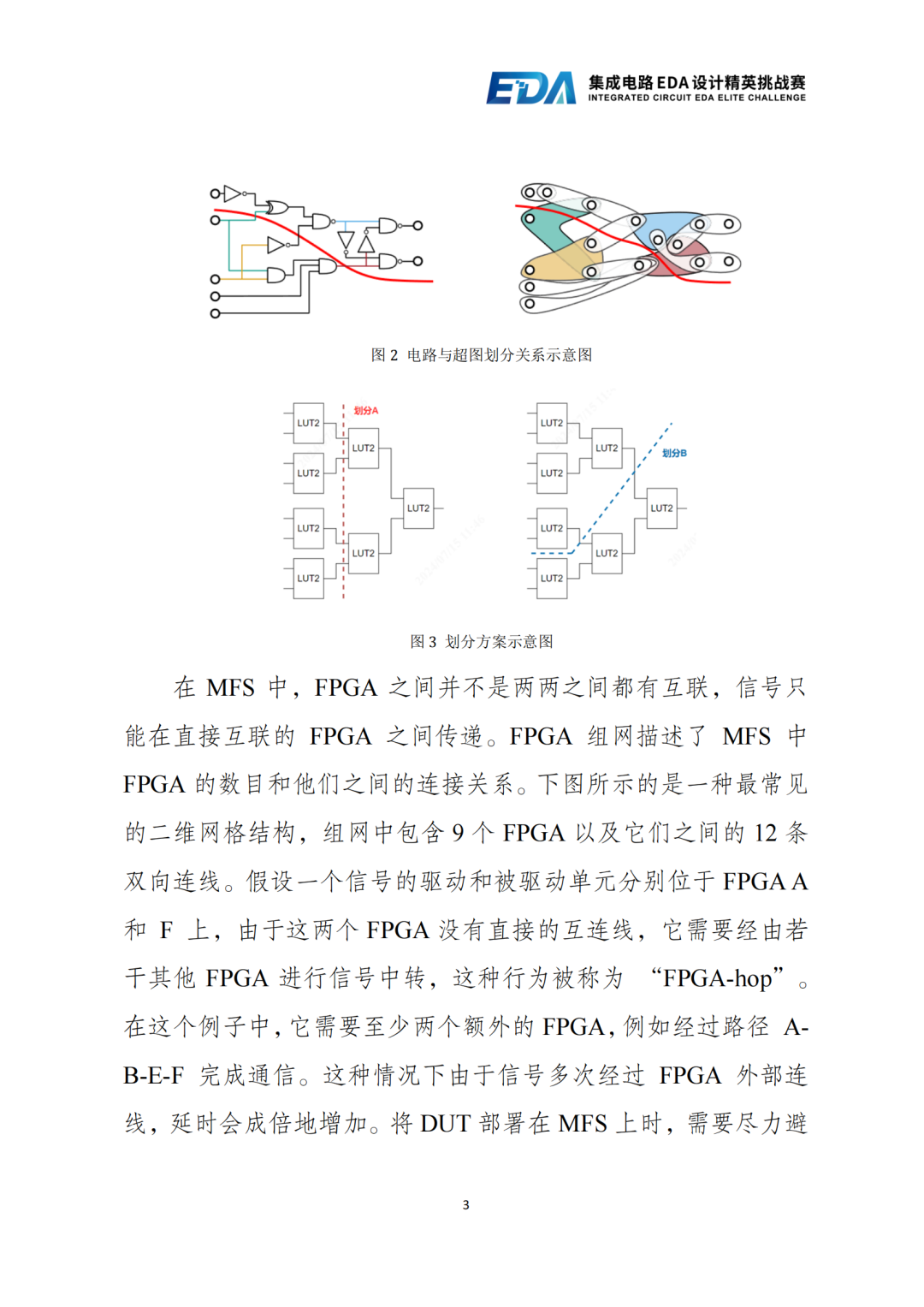

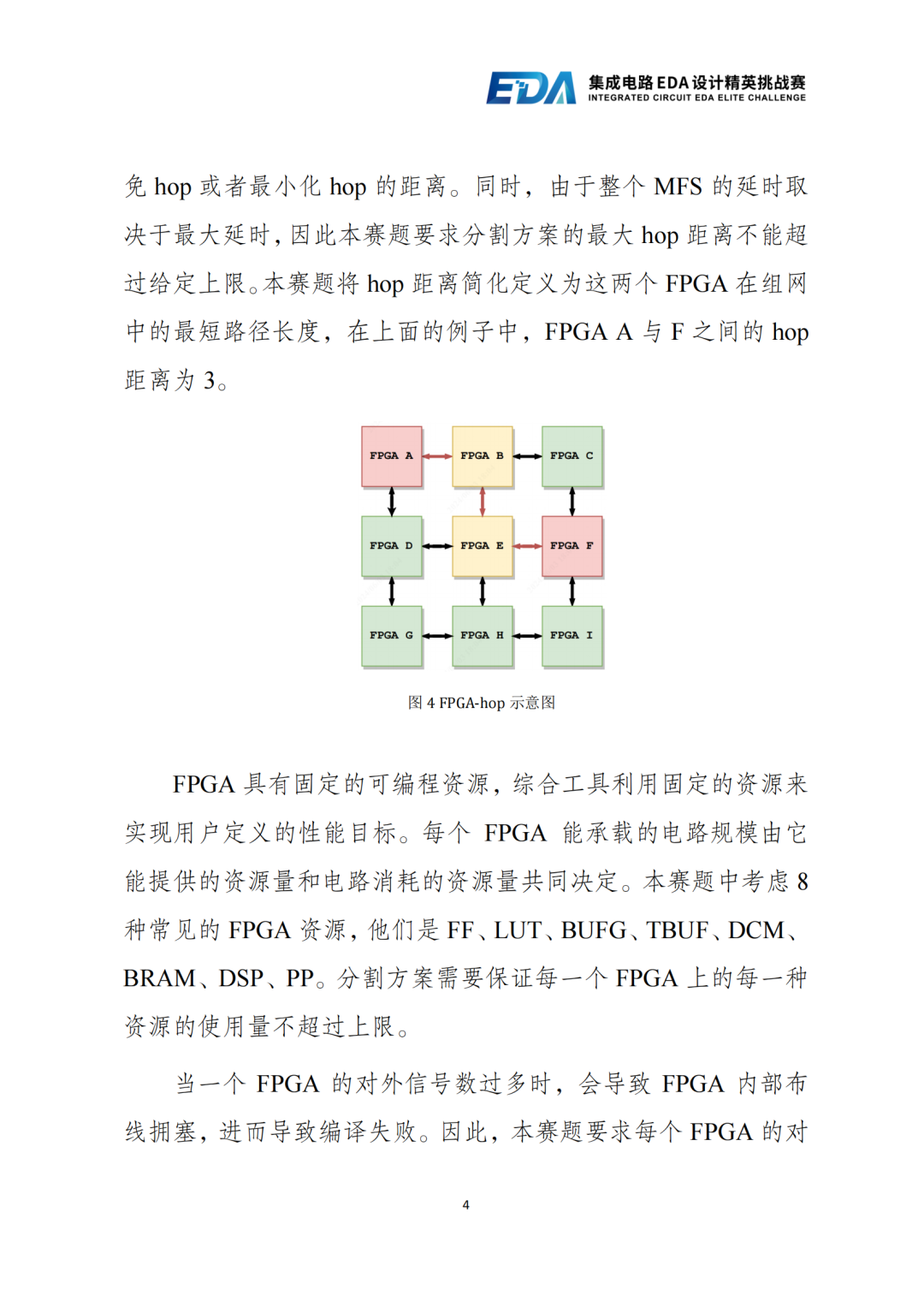

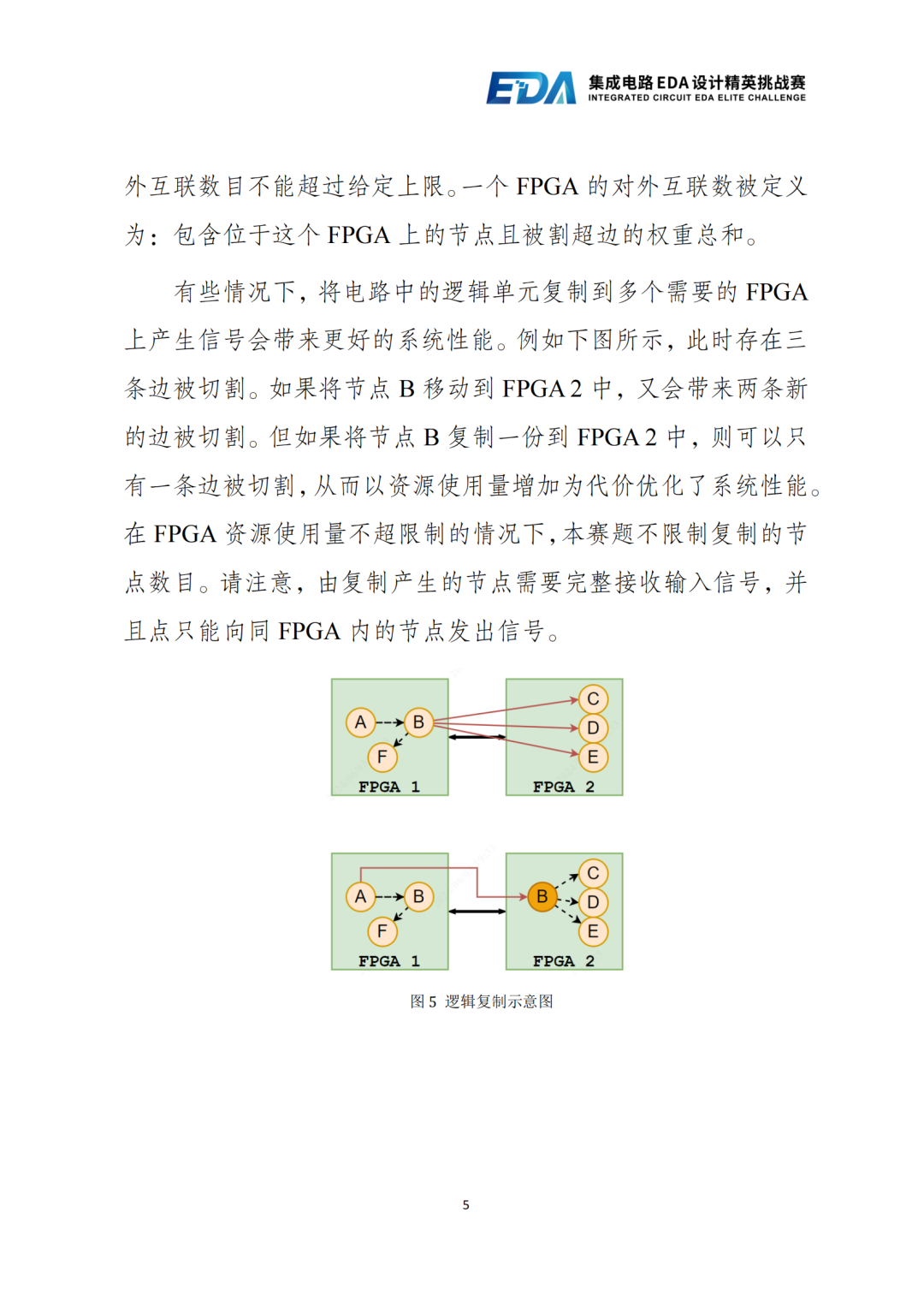

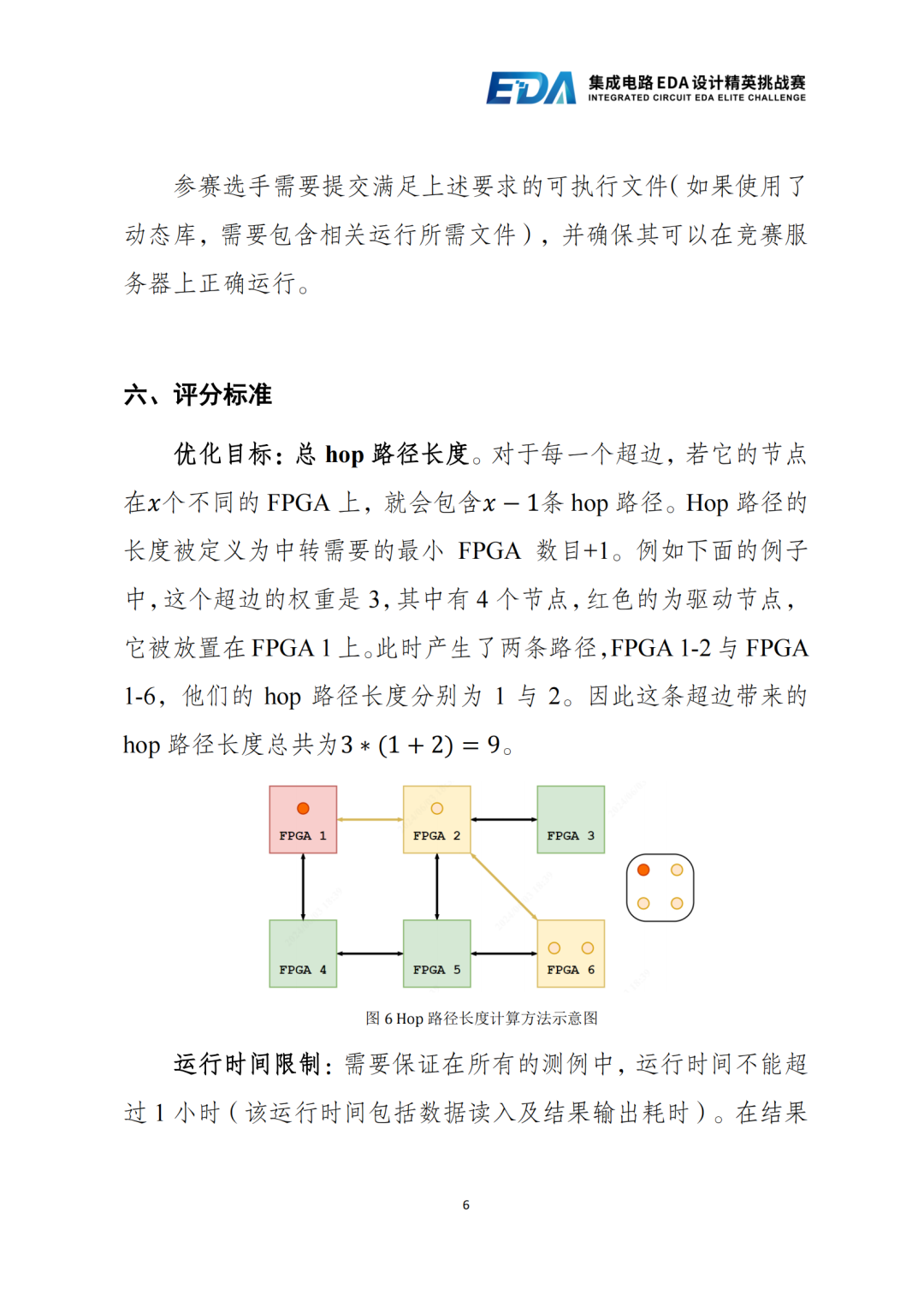

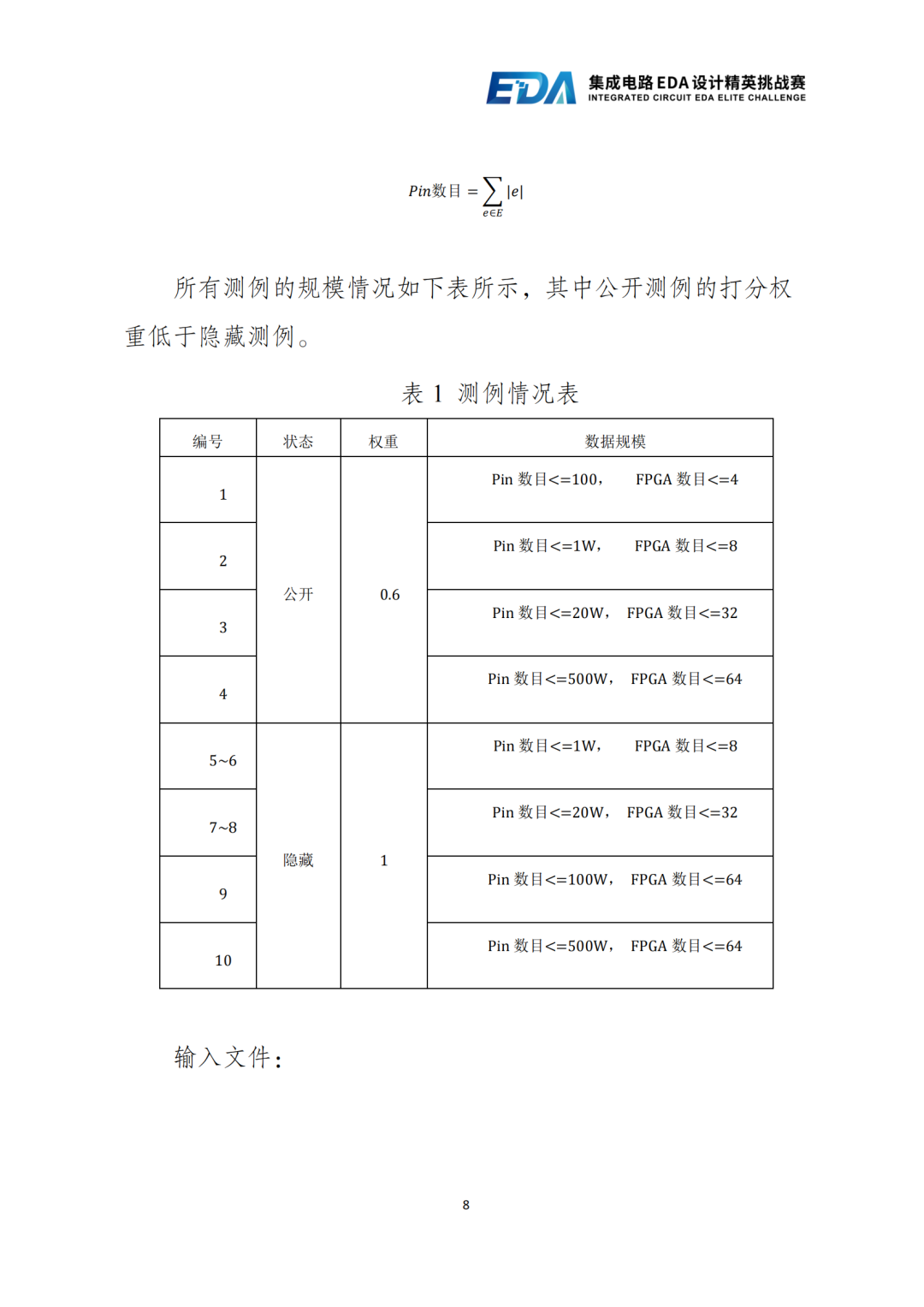

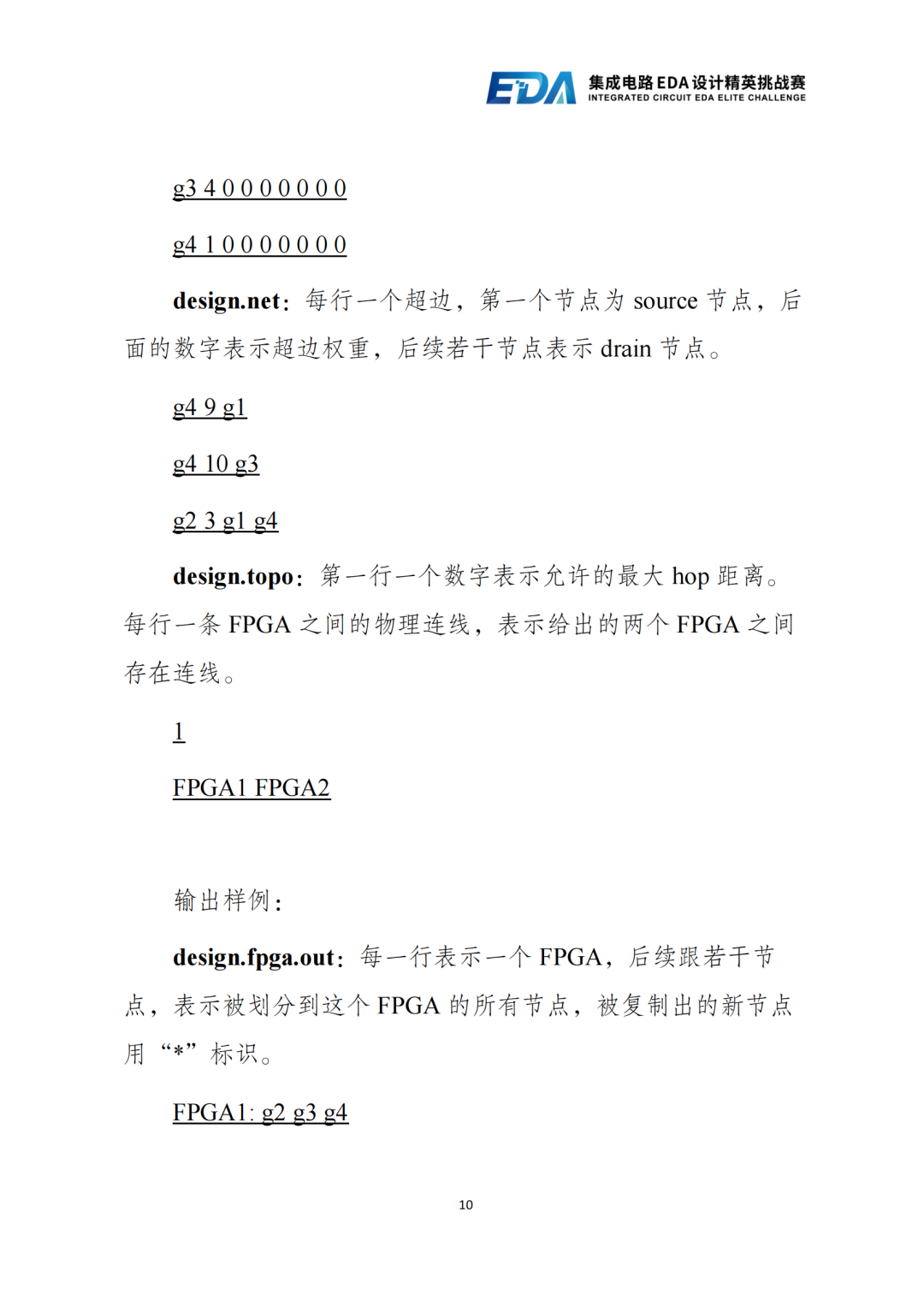

随着集成电路设计规模越来越大,硬件仿真平台难以用单个 FPGA (Field-Programmable Gate Array) 仿真高达数十亿门规模的设计。因此,我们需要应用多 FPGA 系统处理此类工程。图 1 中展示了一个由 4 颗 FPGA 组成的仿真系统。在实际应用中,大规模的设计可能会调用包含数十颗 FPGA 的系统,在这种情景下,分割算法的质量和速度成为了新的挑战。如果不能保证合理的分割结果,DUT (Design Under Test) 的运行频率会受到极大的影响。一个好的分割算法可以在可控的时间内给出一个对时序优化有利的且易于 FPGA 内部布局布线的分割结果。与此同时,对于部分特定电路逻辑的复制也可用来辅助优化分割结果。 图 1 Quad VU440 Prodigy 芯神瞳逻辑系统

图 1 Quad VU440 Prodigy 芯神瞳逻辑系统

03

赛题Chair

为了更好的提升赛题质量,促进产教融合,今年EDA大赛每道赛题聘请一位高校专家作为赛题Chair(赛题负责人),牵头教育学术界专家,与企业命题专家一起负责赛题的命制、实施、答辩评审等工作。

陶俊

复旦大学

陶俊,复旦大学微电子学院教授、博导,IEEE高级会员,长期从事集成电路EDA算法等研究。已在本领域的权威国际期刊和会议包括IEEE Trans. on CAD、IEEE Trans. on VLSI、JSSCC、DAC、ICCAD等上发表论文50余篇。多次担任国际学术会议DAC、ASPDAC、ICSICT等技术委员会成员。多次承担/参与国家自然科学基金、国家科技重大专项、国家重点研发计划项目等。

04

赛题指南

-

2025 EDA精英挑战赛华大九天赛题发布2025-08-26 2082

-

2025 EDA精英挑战赛概伦电子赛题发布2025-08-25 1589

-

创“芯”舞台!思尔芯邀您挑战2025 EDA精英赛2025-08-12 2332

-

探索具身智能边界,地瓜机器人邀你共战ICRA 2025 Sim2Real挑战赛2025-01-13 1282

-

芯华章持续助力EDA精英挑战赛2024-12-17 1730

-

EDA精英挑战赛赛果公布!思尔芯“战队”薪火相承斩获“麒麟杯”2024-12-11 1716

-

第五届EDA挑战赛赛果公布!思尔芯“战队”成绩斐然2023-12-27 1758

-

诚邀破题!集成电路EDA设计精英挑战赛芯华章赛题发布!2023-08-23 3060

-

火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布2023-08-22 3049

-

思尔芯EDA助力2022第四届集成电路EDA设计精英挑战赛2022-12-08 3906

-

集成电路 EDA 设计精英挑战赛最后一天,报名即将截止,错过再等一年2022-10-11 3593

-

芯华章科技持续助力EDA设计精英挑战赛2022-01-05 3157

-

芯华章助力集成电路EDA设计精英挑战赛2021-08-10 7433

全部0条评论

快来发表一下你的评论吧 !