ARM的异常有哪些?ARM的异常向量表基地址

描述

以下文章来源于Arm精选 ,作者baron

1、51单片机的中断响应模型

我们先回忆一下在单片机上的中断的使用。

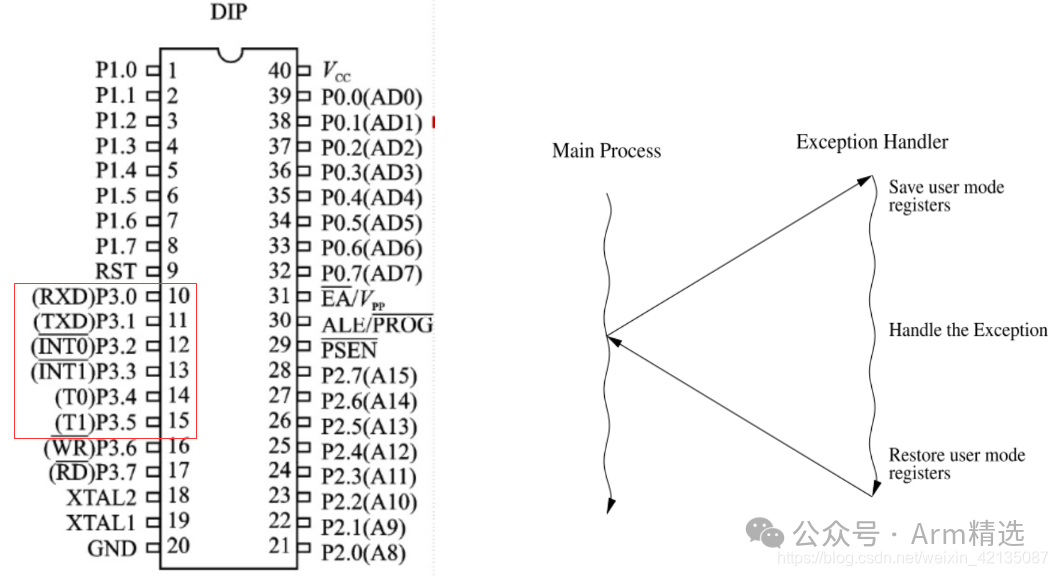

如下图所示,左边是51单片机的管脚图,P3.0-P3.5是单片机对应的中断管教,当该管教电平发生变化时,触发cpu异常。

当cpu来了一个异常时(中断),cpu跳转到异常向量地址处,执行handler函数,执行完毕后再回来

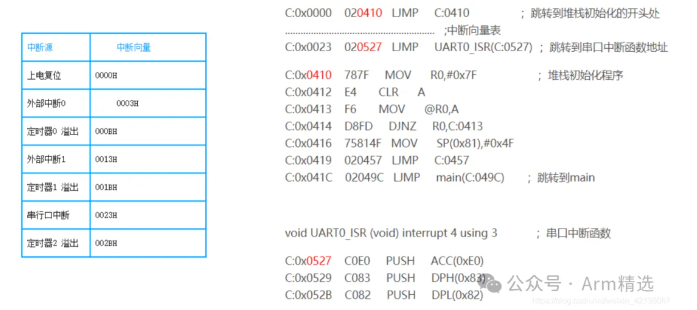

那么cpu异常时,跳转的是哪个地址呢,其实这都是cpu出厂时设计好的。如下图所示,左边是cpu设计好的异常向量表基地址。右边是软件对异常的处理。

当来了一个uart中断时,cpu触发异常跳转到0023地址处,而该地址处执行LJMP UART0_ISR指令,跳转UART0_IAR函数去处理中断…

2、ARM的异常有哪?

在ARMV7上,ARM异常有:RESET、swi、undef、prefetch、data abort、irq、fiq

其中RESET、swi是同步异常,其余是异步异常

在ARMV8上,ARM异常有serror、irq、fiq、Synchronous

其中Synchronous是同步异常,serror、irq、fiq是异步异常

解释一下什么是同步异常什么是异步异常?

同步异常:软件触发行为、知道什么时候发生 例如:svc、smc、hyc指令触发的都是同步异常

异步异常:软硬件行为,不知道什么时候发生,发生时间是随机的 例如:irq中断触发irq异常、fiq中断触发fiq异常…

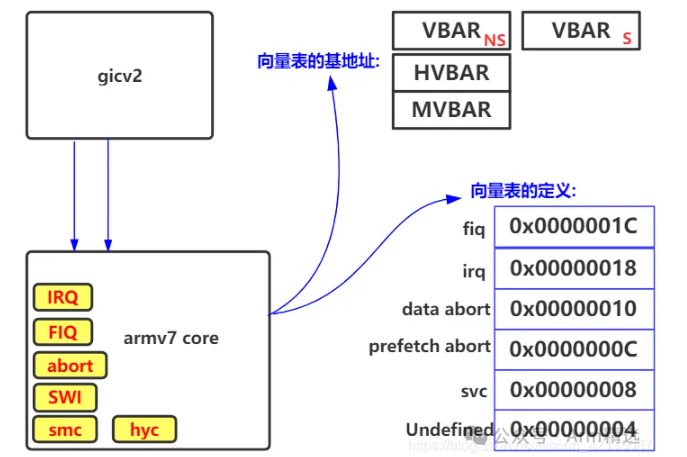

当异常发生了,ARM CORE就要跳转到异常向量表地址处了。其实是跳转到:异常基地址 + 异常向量表偏移处

3、ARM的异常向量表基地址

(1)、ARMV7的异常向量表基地址

主要为VBAR、HVBAR、MVBAR三个寄存器,其中VBAR是banked.

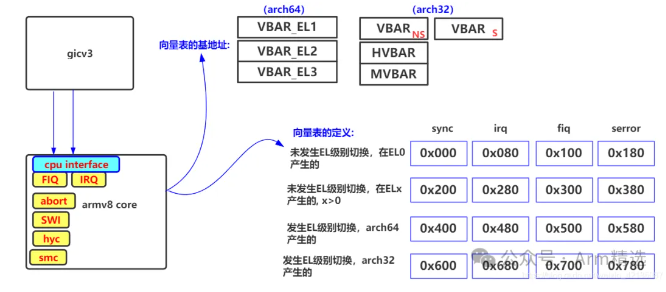

(2)、ARMV8的异常向量表基地址

主要为VBAR_EL1、VBAR_EL2、VBAR_EL3三个寄存器

4、ARM的向量表offset

(1)、armv7的异常向量表的定义

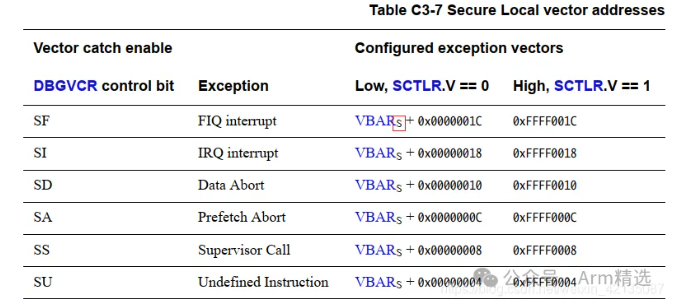

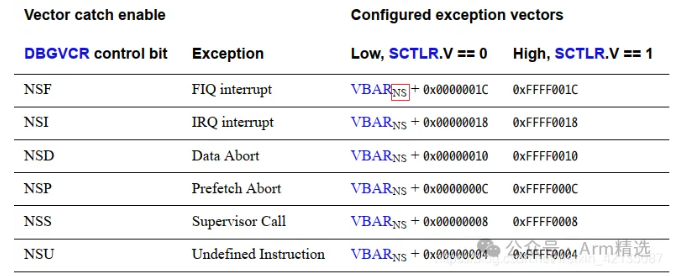

其实在armv7上有多张异常向量表,下图分别列举出在secure、non-secure侧的两张异常向量表

(2)、在armv8上异常向量表

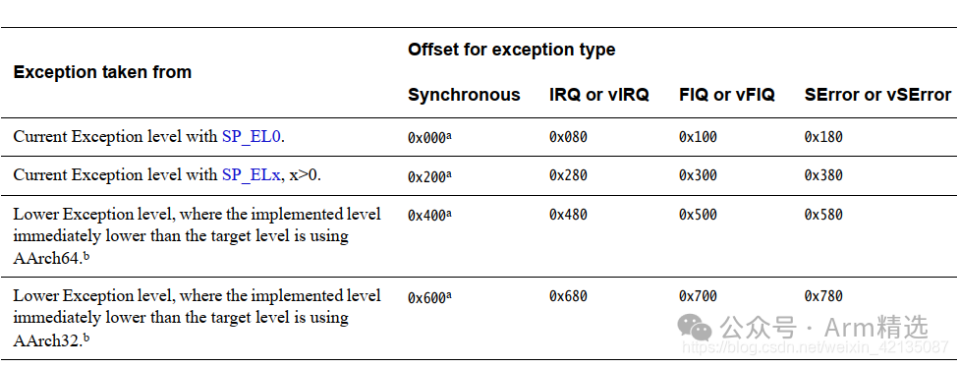

实际上有四组表,每组表有四个异常入口,分别对应同步异常,IRQ,FIQ和出错异常。

如果发生异常并不会导致exception level切换,并且使用的栈指针是SP_EL0,那么使用第一组异常向量表。

如果发生异常并不会导致exception level切换,并且使用的栈指针是SP_EL1/2/3,那么使用第二组异常向量表。

如果发生异常会导致exception level切换,并且比目的exception level低一级的exception

level运行在AARCH64模式,那么使用第三组异常向量表。

如果发生异常会导致exception level切换,并且比目的exception level低一级的exception

level运行在AARCH32模式,那么使用第四组异常向量表。

另外我们还可以看到的一点是,每一个异常入口不再仅仅占用4bytes的空间,而是占用0x80 bytes空间,也就是说,每一个异常入口可以放置多条指令,而不仅仅是一条跳转指令

-

ARM9的高端异常向量基址硬件如何配置?2019-04-25 1681

-

ARM寄存器分析以及异常处理方法2019-09-10 3699

-

arm异常的处理方法2020-04-20 2078

-

资料下载:[architecture]-ARM Core如何响应中断的2021-07-01 687

-

浅析ARM的异常分类与异常处理2022-04-26 4470

-

ARM中断向量表异常处理过程解析2022-05-05 3307

-

一文弄懂ARM芯片的地址重映射2022-05-23 4291

-

ARM未定义指令异常和SVC异常是什么意思2022-05-26 4645

-

教你一种ARM处理异常中断的方法2022-08-18 3513

-

异常向量表重映射2010-03-26 774

-

如何理解ARM异常、中断和向量表2018-06-14 4779

-

ARM体系结构所支持的异常有哪些含义和所支持的异常类型概述2019-02-26 4681

-

嵌入式系统原理及应用教程之ARM异常中断处理及编程的资料说明2019-03-20 959

-

ARM体系结构所支持的异常和具体含义2019-10-24 4806

-

ARM interrupt-42021-12-04 589

全部0条评论

快来发表一下你的评论吧 !