使用SDNet开发创新型可编程网络

FPGA/ASIC技术

描述

Lagopus FPGA 可最大化电信和云服务的SDN/NFV 功能。

日本电报电话公司 (NTT) 是一家全球电信集团控股公司,负责制定管理策略和推动研发工作发展。 我们是 NTT 研发部的研究人员,正领导两个针对软件定义网络 (SDN) 和网络功能虚拟化 (NFV) 的创新型项目。针对其中的一个项目,我们已经开发出一个名为 Lagopus 的高性能软件 SDN/OpenFlow交换机[1],我们认为这是迄今为止作为开源软件发布的 OpenFlow 1.3 兼容交换机中的佼佼者。针对第二个项目,我们开发出一个具有软件包处理感知功能的 40 Gbps FPGA 网络接口卡 (NIC) ——Lagopus FPGA。

早期阶段采用赛灵思面向网络的 SDNet 软件定义规范环境,是我们能够成功开发这些技术的关键所在。在本文中我们将介绍如何使用SDNet满足我们的项目目标。

实现 SDN/NFV 卓越性能的 LAGOPUS FPGA

云服务供应商和网络服务运营商正在转向采用SDN,将其作为自动配置系统的关键支持技术。NFV 通过将网络系统从专有硬件设备转变为商用硬件系统,充分运用 PC 服务器、基于商用芯片的交换机和软件工具,在帮助电信运营商降低资本支出和运营支出方面起着至关重要的作用。许多云服务提供商和电信运营商将为其新一代商用网络部署 SDN 和 NFV。

NTT 集团是商业服务和研发领域的 SDN 和NFV 领跑者。在日本总务省的自助下,NTT 已经启动一项与先进 SDN/NFV 相关的研究工作——O3 项目。Lagopus 是 O3 项目的主要可交付成果,其结合使用开放网络基金会 (Open Networking Foundation)的 OpenFlow 1.3 协议、商用英特尔 x86 服务器和商用 NIC, 可实现高性能软件包处理和灵活的流程控制。 Lagopus 的主要优势有: 能在商用服务器上实现超过 10Gbps 的高性能软件包处理、高达百万流量输入的弹性网络流控制、针对虚拟提供商边缘 (vPE)/ 虚拟客户端设备 (vCPE) / 虚拟演进分组核心网 (vEPC) 框架的可扩展流程分配器。

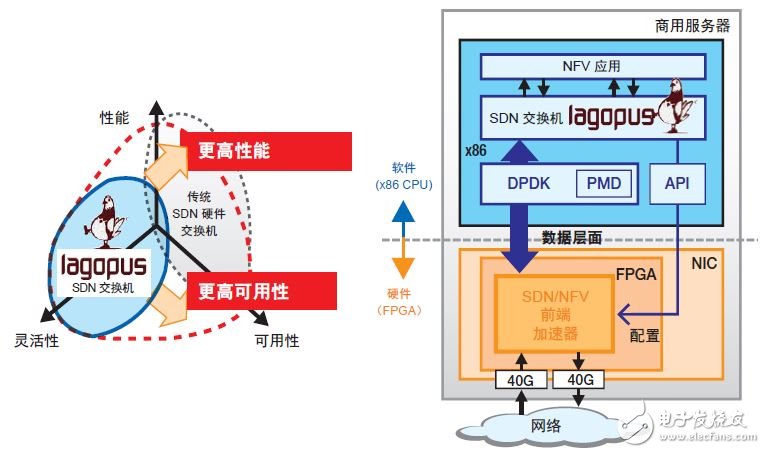

Lagopus FPGA 项目旨在通过在运行于商用服务器上的 FPGA 上灵活地对软件加速和硬件加速功能进行分区,实现 40/100Gbps 的高性能包处理。图 1显示了 Lagopus FPGA 的概念和架构。这种灵活的架构能借助 FPGA 加速并以纯软件实现方式将 Lagopus交换机的 10Gpbs 线速提高到 40Gbps 线速。这一性能提升的代价仅仅是 x86 CPU 的功耗增大不到 10%。该架构还能极大地增强我们的网络故障排除能力,这对真正虚拟化的网络有实质性意义。

图 1 — Lagopus FPGA 的概念和架构

目前, 我们正在使用先进的 FPGA 和设计工具联合为 Lagopus 和网络运营商的原始硬件知识产权(IP) 设计一种先进的软件可编程数据层面,其目的不仅是获得更高的系统性能,也是为降低功耗和成本。通过与赛灵思团队合作,我们已经在基于赛灵思 Virtex?-7 All Programmable FPGA 的 80Gbps NIC演示板上成功集成了 Lagopus 和我们的 IP。2015 年2 月,我们在东京举办的 NTT2015 年研发论坛上首次演示了 Lagopus FPGA。同年 8 月,我们还在加州库比蒂诺举办的 Hot Chips 27 大会上展示了我们的卓越成功。

我们使用 SDNet 开发环境创建 Lagopus FPGA系统。这种新颖的动态可重编程数据层面包处理工具链让我们能够在不影响性能的情况下,把数据包分类、编辑、搜索、负载均衡和统计测量等高强度数据层面运算转交给 FPGA NIC 处理(均在10/40/100GbE 千兆位级以太网线速下实现),为 Lagopus和 NFV 应用提速。我们认为这是我们项目的最佳解决方案,可增强 SDN/NFV 技术的关键组成部分—— 分类 IP 的功能。该环境的快速可重配置包流水线功能让我们能够迅速方便地更新网络协议和功能。

SDNet 环境涵盖云计算数据中心和广域网中丰富多样的用例,从而扩大了 Lagopus FPGA 的使用潜力。对 NTT 而言,这种灵活、软件定义硬件设计技术能实现差异化网络业务的灵活部署。

SDNet 扩大了 Lagopus FPGA 的使用潜力:这种灵活的软件定义硬件设计技术能实现差异化网络业务的灵活部署。

SDNet 环境奠定设计基础

随着新兴市场上 SDN/NFV 技术竞争日趋激烈,Lagopus FPGA 项目的一大设计挑战是在紧凑的开发期内完成开发,以如期进行部署和推广。我们从 2014 年 10 月开始设计 Lagopus FPGA 系统,三个月后,即在 2015 年 1 月完成首次集成。

鉴于该系统设计的复杂性,这是一项了不起的成就。图 1 所示是 Lagopus FPGA 系统的顶层架构,它由包含软件 FPGA IP 包在内的四个技术软件层组成:(1) NFV 应用;(2) Lagopus 软件交换机;(3)硬件抽象层,例如应用编程接口 (API)、英特尔数据面开发套件 (DPDK)、一组用于x86 快速包处理的库和驱动程序;以及 (4) FPGA NIC IP 内核套件。该多重技术软件层会增大追踪问题根源的难度,如丢包和性能降低,削弱调试和立即隔离故障的能力。实际上这也是所有 SDN/NFV 架构的重大难题。为克服这些难题,我们采用了 SDNet 环境和赛灵思Vivado? Design Suite。

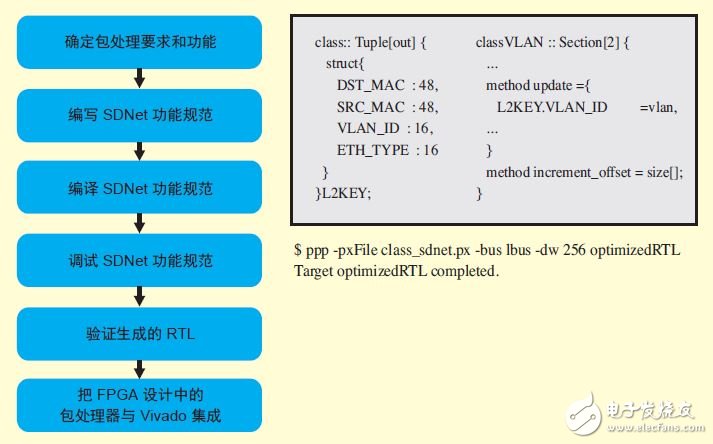

我们在启动 Lagopus FPGA 的设计工作时,先确定我们对包处理功能的要求,并且制定出一个开发流程。图 2 是这一开发流程的一般性介绍和SDNet规范的示例代码段。我们决定创建一个完美匹配的滤波器。该过滤器采用来自虚拟 LAN 的关键信息。借助这个过滤器,我们可以把硬件分类功能卸载到FPGA NIC,在 x86 上为 Lagopus 的软件数据层面提速。我们可使用 Lagopus 和 SDN 控制器之间的OpenFlow 协议注入流程项,进而通过 DPDK 流程指示器 API 配置滤波器项。

图 2 — SDNet 环境的设计流程

为实现这一策略,我们创建了相应的 SDNet 功能描述,如图 2 的代码段所示。我们随后把该代码输入 SDNet 编译器,设定总线类型、总线宽度和生成的 RTL 类型等选项。编译在数秒钟内完成。SDNet功能描述的实际代码规模大约为 250 行代码。相比之下,等效的 RTL 需要由数万行代码构成。考虑到我们的工作日程紧张,我们十分欣赏 SDNet 规范的简洁性。受我们开发时间的约束,要在 RTL 中重新设计并验证这一复杂模块是无法做到的。

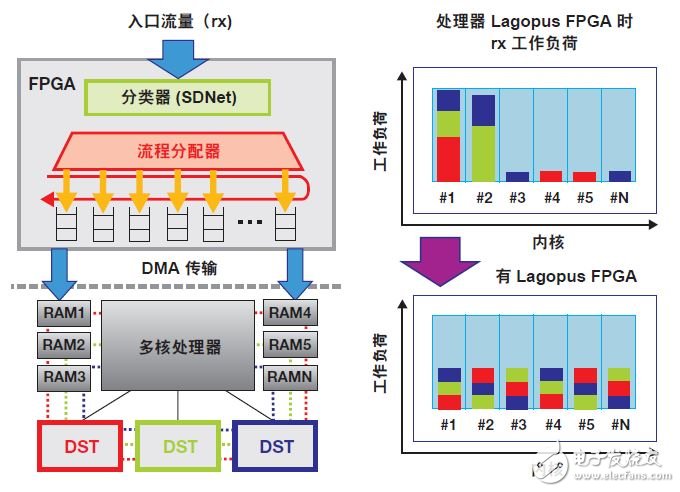

下一步我们使用工具命令语言 (Tcl) 外壳程序,将生成的 RTL 与 Vivado Design Suite 上的其他外设IP 集成在一起。图 3 所示为集成式 SDNet 分类器和我们定制的流程分配器。我们的目标编程器件是赛灵思 Virtex-7 XC7VX690T FPGA。

图 3 — FPGA 流程分类与分配

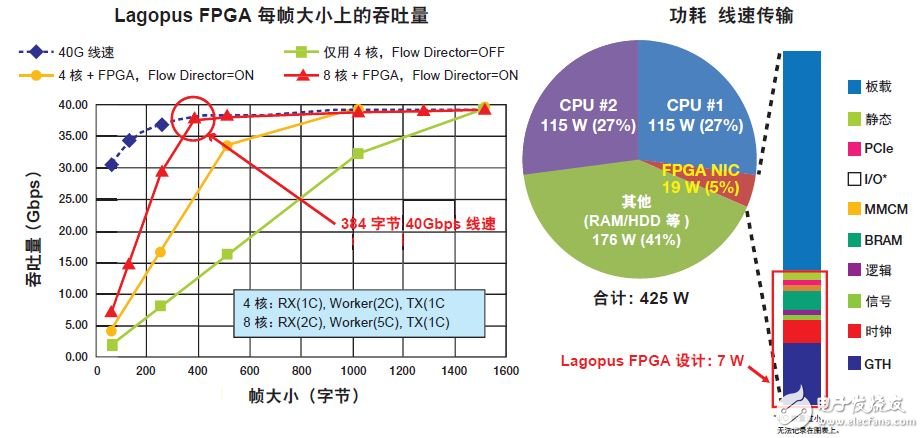

借助 Lagopus FPGA,我们仅以 x86 功耗上升不足10% 为代价,便实现了 40Gbps 线速软件包处理能力。

由于分类后的包流(指向 32 个接收 [rx]DMA队列)通过在 x86 多核 CPU 上工作的 Lagopus 的软件数据层面能够得到有效分配,这种集成 FPGA 设计让系统不仅能减少 Lagopus 的 OpenFlow 工作线程占用的 CPU 周期,而且还可平衡每个内核的工作负荷(图 3)。因此,, 我们使用 Lagopus FPGA 实现了更高性能—— 达到 40Gpbs 线速软件包处理能力,而且付出的代价仅仅是 x86 CPU 的功耗增大不到 10%(如图 4 所示)。

图 4 — 性能与功耗关系图

SDNet 环境与 Vivado Design Suite 结合运用,有助于我们项目的启动,让我们能够最大程度地丰富Lagopus FPGA 系统的特性集,优化性能并降低功耗。NTT 研发部在 SDN/NFV 领域的领先地位,加上我们对赛灵思 SDNet 开发环境的运用,让我们为电信和云基础架构将带来革命性变化。为此,我们将继续运用软定义、可重编程的 SDNet 负载模块来优化我们的设计方法。包括 API 在内的 SDNet 规范的不断快速修改在我们设计未来平台时能为我们提供更多益处。

-

可编程电源如何编程2024-06-10 3181

-

爱立信吴日平:高性能可编程网络赋能新型工业化2024-05-20 19217

-

可编程网络的发展将走向何方?2022-10-26 1437

-

基于国产可编程逻辑芯片的工业网络解决方案2022-02-08 1901

-

求一种新型系统级可编程芯片的设计方案2021-05-06 1699

-

分享一款不错的基于新型规则的可编程交通控制系统设计2021-04-28 1245

-

现场可编程门阵列简介2021-04-07 1434

-

在100Gbps每秒可编程包处理系统中实现无中断升级2018-11-23 2836

-

基于WP276 -可编程的开发和测试2017-10-31 711

-

可编程逻辑器件原理、开发与应用2017-09-19 870

-

现代可编程序控制器网络通信技术_部分22016-04-19 1027

-

开源可编程手环2015-10-17 3065

-

可编程SoC(SoPC),什么是可编程SoC(SoPC)2010-03-26 2700

-

可编程模拟器件原理与开发2009-06-20 1577

全部0条评论

快来发表一下你的评论吧 !