LVDS的GCLK接收方案

描述

在易灵思的器件上接收LVDS一般采用PLL接收,通过PLL产生两个时钟,一个是fast_clk,一个是slow_clk,分别用于处理串行数据和并行数据。

但是如果LVDS的速率比较低时,另外想通过去掉PLL来节省功耗时,也可以直接用lvds_rx_clk直接走GCLK的方式来处理。下面我们来说明一下:

硬件环境如下:

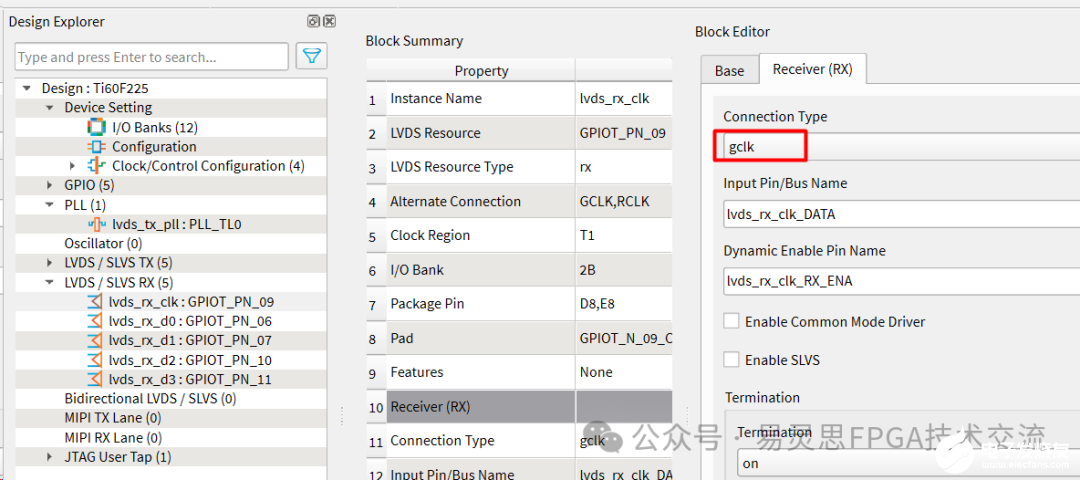

打开interface在里面设置LVDS

LVDS的时钟接收Connection Type选择gclk。

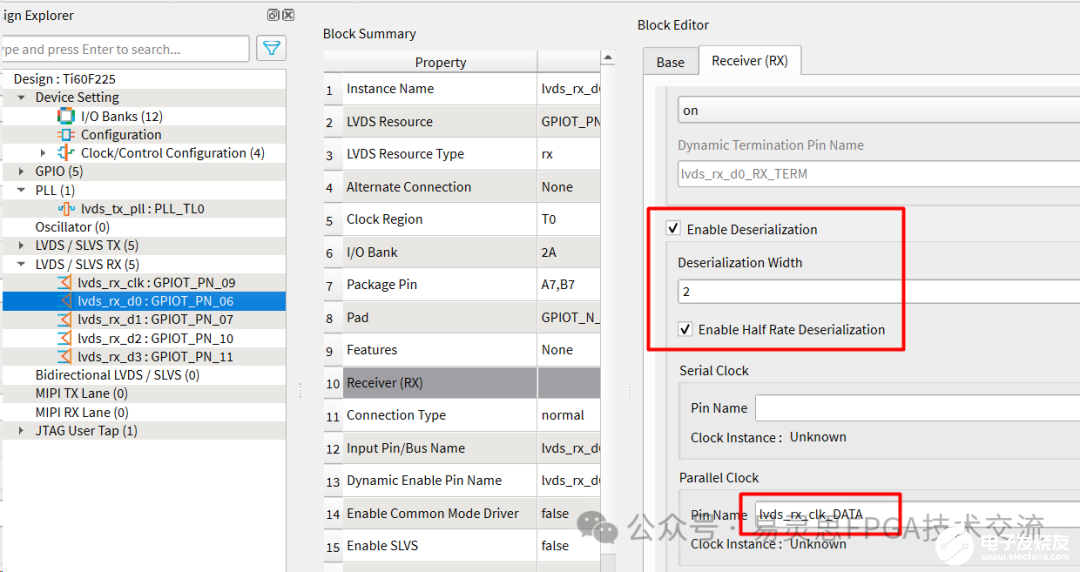

对于数据设置串化因子为2,并输入Parallel Clock名字为上面定义的时钟。

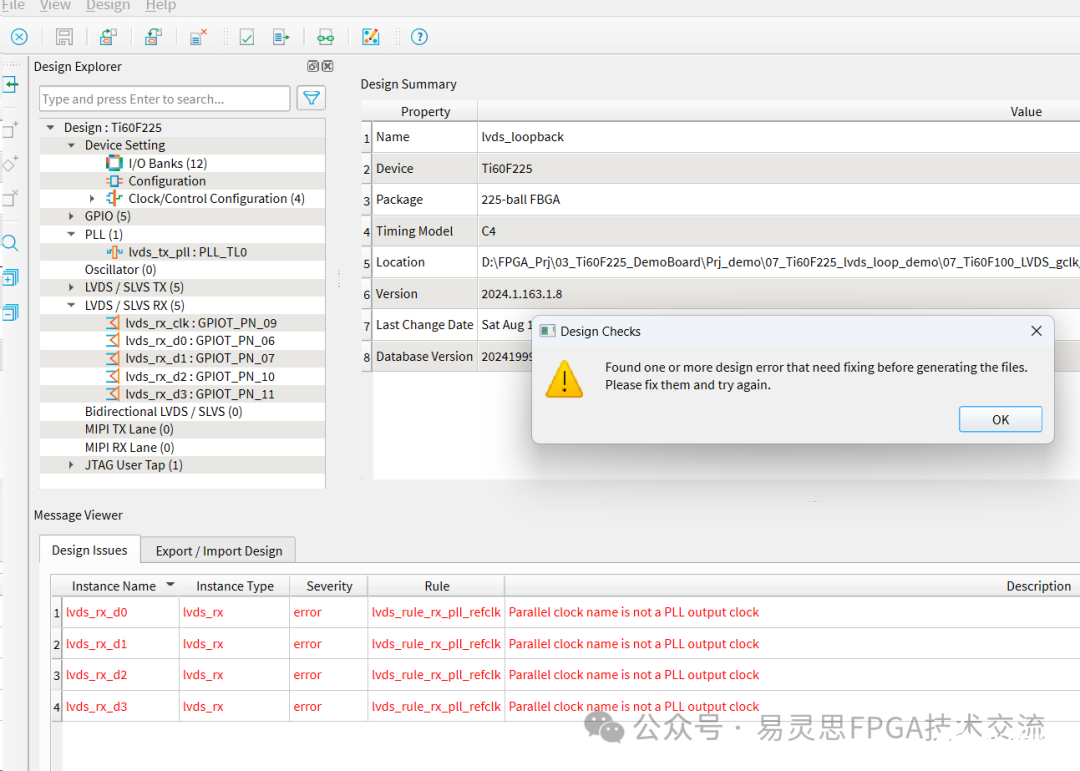

在一切都设置好之后需要生成约束。但是会报以下错误。

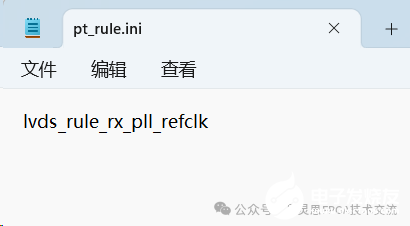

但是解决办法是有的。在工程目录下新建pt_rule.ini文件,输入lvds_rule_rx_pll_refclk,再次生成结束可以正常。

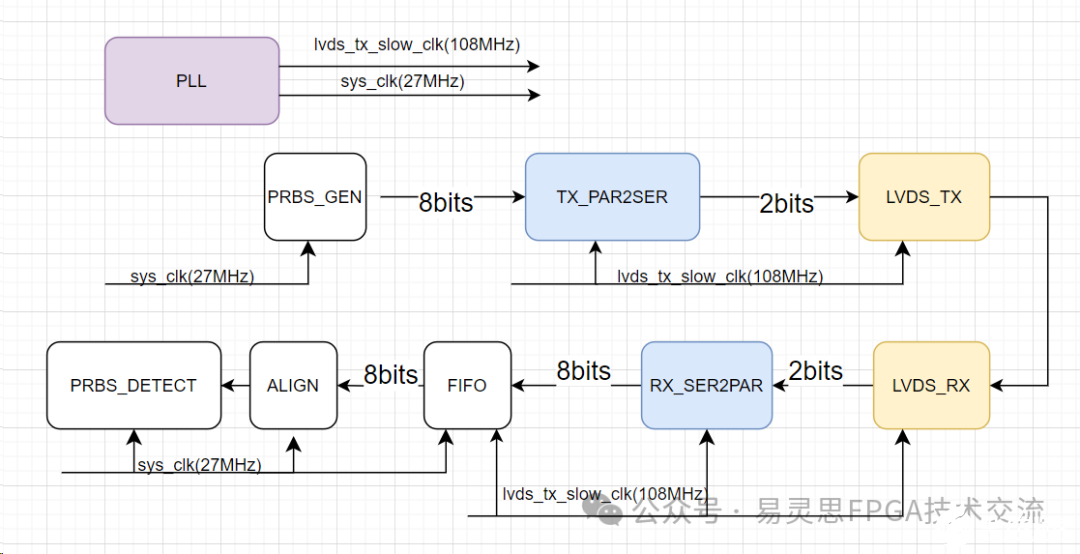

程序框图如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【代码分享】基于乐鑫ESP32的串口不定长数据接收方法2024-11-15 2363

-

LVDS Serdes接收器SN65LVDS96LVDS数据表2024-06-26 423

-

有没有用杰理的蓝牙芯片设计的音频接收方案?2023-12-04 1992

-

基于多相滤波的宽带中频正交采样数字零中频接收方案2022-12-12 711

-

鸿蒙分享的接收方有什么接口可以响应的?2022-04-25 3212

-

stm32常见的串口接收方式是什么?2021-12-09 390

-

分享一个不错的xSO16-RX无线充电接收方案2021-09-26 2624

-

为TWS充电盒设计的无线充电接收方案XS016-RX2021-07-26 1879

-

请问有办法将LVDS时钟信号应用于GCLK时钟输入吗?2019-06-25 1202

-

XS016-RX无线充电接收方案TWS充电盒方案的电路原理图免费下载2019-06-04 2378

-

HAPS通信中基于MIMO的信号协作接收方案性能分析2013-01-10 1042

-

采用LVDS接收器解决非LVDS应用问题2011-07-18 1418

-

基于串口通讯的打包数据的接收方案2009-09-17 643

全部0条评论

快来发表一下你的评论吧 !