Zybo board 开发经验分享第一季: 详解硬件构架

FPGA/ASIC技术

描述

为了学习 RISC-V 以及体验看看 Xilinx 的开发平台,最近我入手了 Zybo Board ,这是一块具有 FPGA 同时又包含了 ARM Cortex-A9 双核心的开发板。

在我们开始这一切之前,我们需要稍微了解一下这片开发板以及他的外围等信息。

要了解 Zybo Board 的外围,首先要看的就是开发商 DIGILENT 所提供的 ZYBO FPGA Board Reference Manual。让我们来看看一些比较重要的地方吧!

基本硬件认识

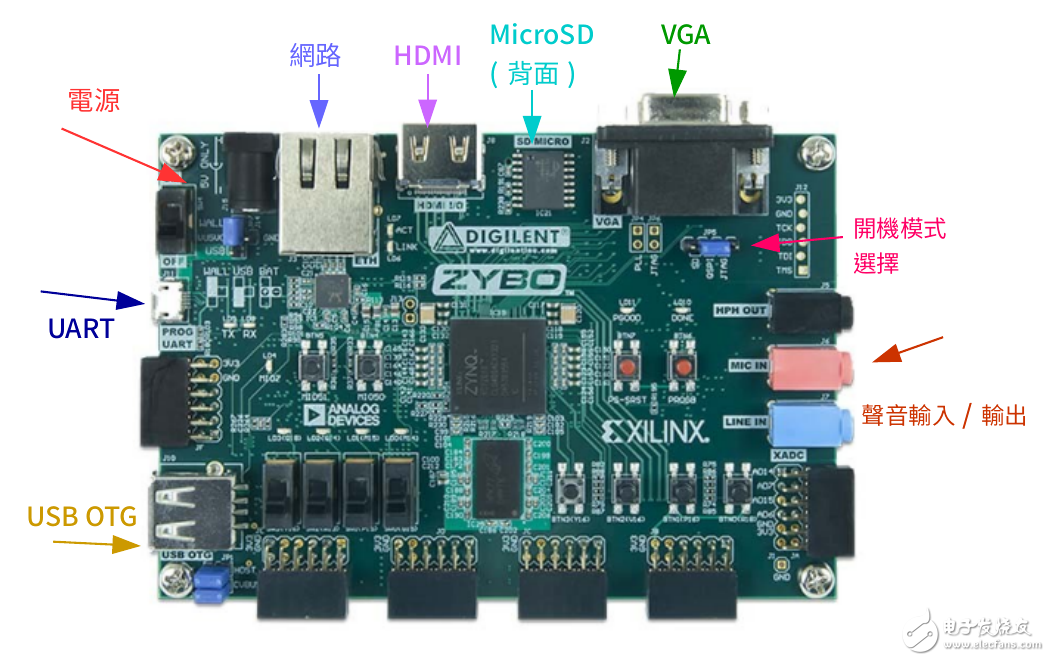

拿到手的 Zybo Board 会像下面这个样子,我们有这些基本的输入/输出模块,以及未标示的部份(Pmod),可以做延伸的功能

让我们来看看这些外围模块吧

电源输入(5V)

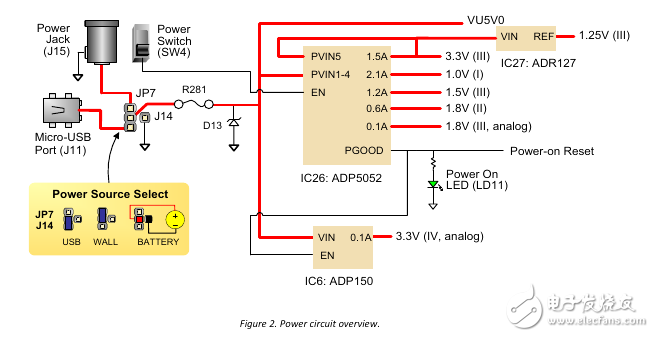

Zybo Board 允许三种不同类型的电源输入模式,分别是 USB、外接电源(J15)、外接电池。我们可以从Reference Manual 得到电源模块的大致信息。

控制电源输入的位置在 JP7 的排针座上,我们可以透过切换跳线(Jumper)来选择我们需要的电源输入,在外围使用不多的情况下,我会直接使用 USB (5V) 来作为电流的输入。

要注意到的是,Zybo Board 仅吃 5V 电源,因此不论你是用外接电源(J15)或是外接电池,你最好都先确认你的电压是否为 5V (或是低于) ,否则你的开发板可能因此烧坏。

插上电源后,透过电源开关 (Power Switch, SW4) 的切换即可完成给电/断电的动作。

Zynq SOC

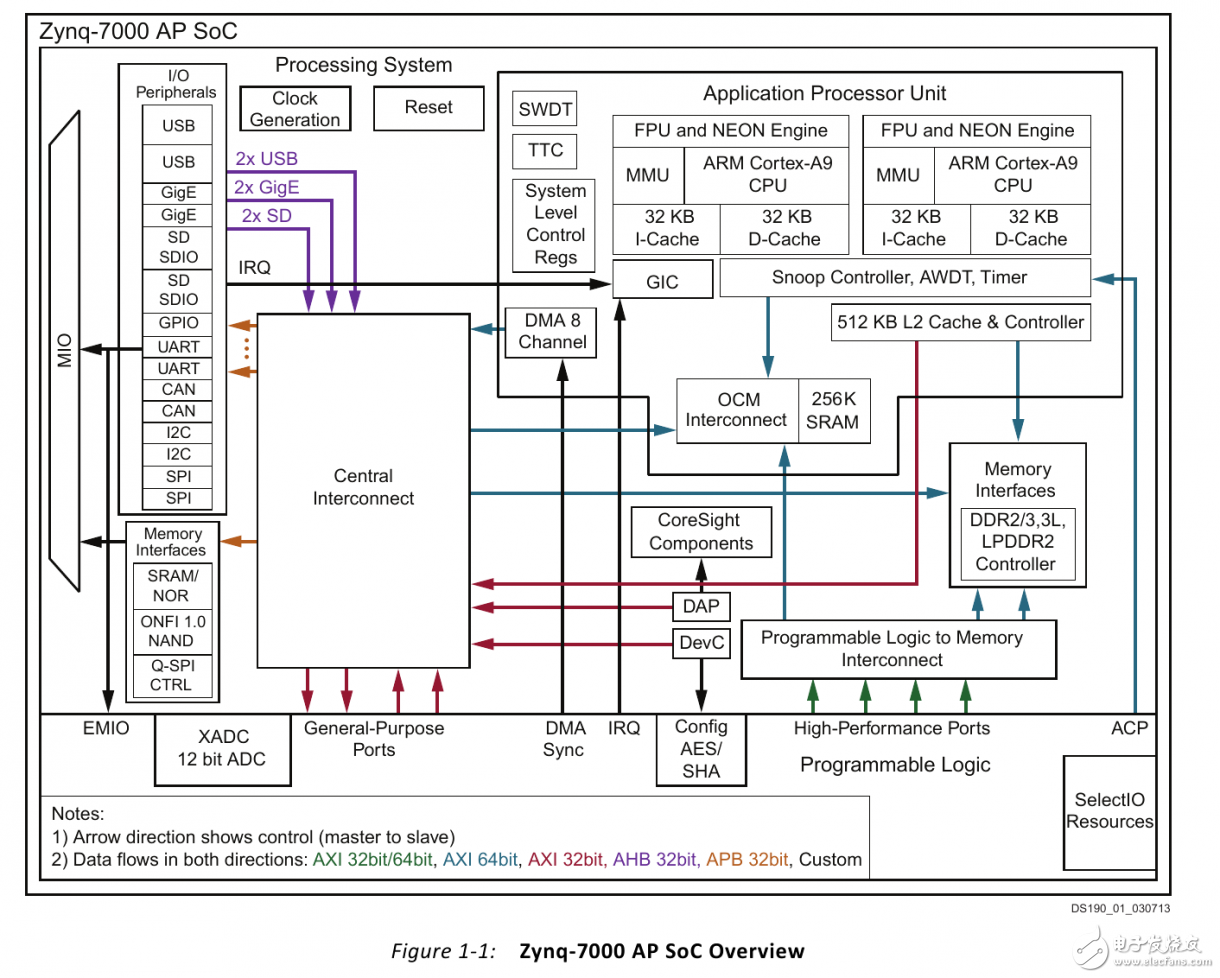

Zybo Board 核心是 Xilinx Zynq-7000 系列的 Z-7010 ARM/FPGA SoC 处理器,这是一种混和了 FPGA 以及 ARM Cortex-A9 处理器的 FPGA 核心。以往的 FPGA 开发板需要用到 CPU 的时候只能够刻录用 HDL 语言撰写的软核心到开发板上,这种混搭 FPGA/ARM 的开发板则是让你可以针对通用需求使用 ARM CPU 进行程序的开发,特殊需求则透过 FPGA 进行处理/加速来运作,是一种蛮有趣的架构。

我们可以把 Zynq SoC 分为两个区块, 处理系统 (Processing System, PS) 以及 可程序逻辑区块(Programmable Logic, PL),像这样处理系统(Processing Syste, PS) 也就是有 ARM Cortex-A9 处理器的部份,可程序逻辑区块(Programmable Logic, PL) 则是 FPGA 所包含的部份。

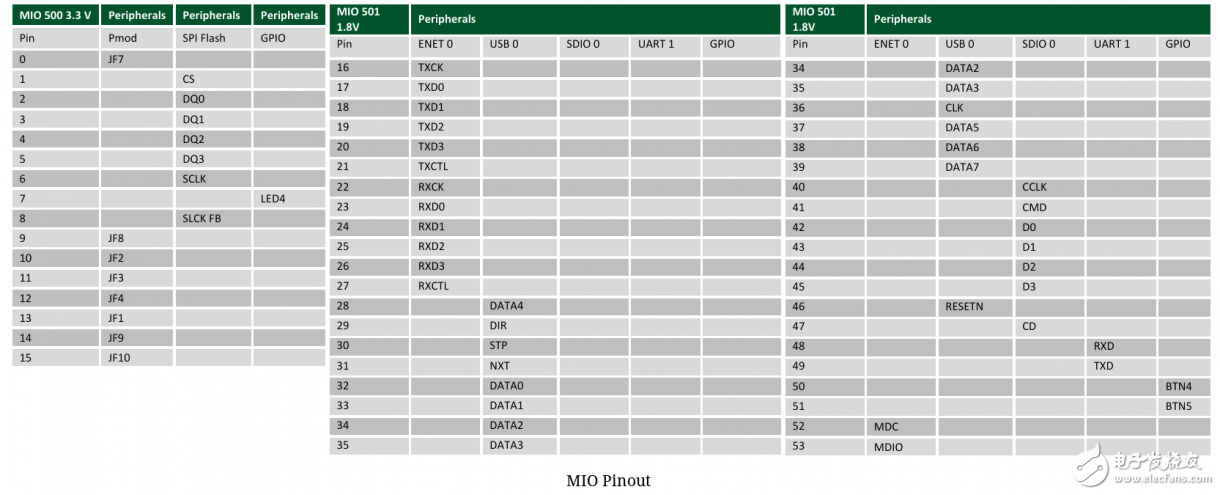

在上面的区块图中,我们要另外注意到 MIO (Multiplexed I/O) 以及 EMIO (Extended multiplexed I/O),在 Zynq 7000 系列 SoC 中,我们共有 54 个 MIO 可用,而这些 MIO 所连接的地址是无法在 可程序逻辑区块 (Programmable Logic, PL) 中看到。

在 Zybo Board 我们有这几个地方是连接到 MIO (Multiplexed I/O) 上的

系统启动流程

由于 Zynq 7000 系列内建了 ARM CPU,也因此和传统的 FPGA 开发板相比,系统启动流程也会不同,整体开机流程可以分为三个阶段:

o 阶段 0

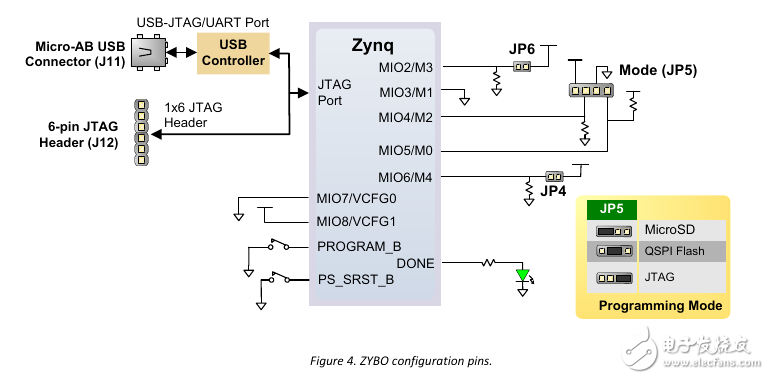

当 Zybo board 电源启动后,CPU0 会执行内部已经预刻录的程序 BootROM,这个程序会根据 JP5 所设定的信息来更新状态缓存器(mode register),接着 BootROM 会透过状态赞存器(mode register)的信息从 MicroSD、NOR Flash、JTAG 等位置抓取 Zynq Boot Image,并将包在 Zynq Boot Image 里面的 第一级启动开机程序 (First Stage Bootloader, FSBL) 复制到内部 256KB 的内存 (On-Chip Memory, OCM) 去,最后执行 FSBL,进入下一个阶段。

如果 BootROM 是因为按下了 RESET 按钮等状况而被执行,Zybo board 会选用之前已经存放在状态缓存器(mode register)的开机状态,而不是当下的 JP5 状态。

o 阶段 1

在这阶段中, 第一级启动开机程序 (First Stage Bootloader, FSBL) 初始化了 DDR 内存、GPIO 等外围设定,接下来会加载存放在 Boot Image 内的比特流 (bitstream),用他来对可程序逻辑区块 (Programmable Logic, PL) 进行设定。

当可程序逻辑区块(Programmable Logic, PL)设定完成后,FSBL 会去加载程序(ex: u-boot)并执行它。

o 阶段 2

最后的接段即是执行 FSBL 所加载的程序,这些程序可以从简单的 "Hello World",到像 u-boot 这样的第二阶段开机程序,用来加载 Linux 或是其他的操作系统。

更改开机模式

我们可以透过切换 JP5 的跳线(Jumper)来决定我们要透过哪种方式去加载第一级启动开机程序 (First Stage Bootloader, FSBL)

MicroSD 启动

当使用者将 MicroSD 插入到 J4 的 SD 卡槽,并设定好 JP5 的跳线的话,我们可以透过 MicroSD 来进行开机的动作。

若你希望透过 MicroSD 进行开机,你需要先设定好你的 SD 卡:

1. 透过计算机格式化 MicroSD 卡成 FAT32 文件格式

2. 复制从 Xilinx SDK 制作出来的 Zynq Boot Image 到 MicroSD 卡上

3. 将 Zynq Boot Image 命名为 BOOT.bin

4. 将 MicroSD 卡从计算机移除,并插入到 Zybo Board 的 J4 SD 卡槽上

5. 接上电源,并设定好 JP7 (Power Source Select)

6. 将 JP5 的跳线 (Jumper) 调整到 MicroSD 模式 (板上标示为 SD 的那个)

7. 启动电源。接下来 Zybo Board 就会从 MicroSD 卡启动。

QSPI 启动

在 Zybo board 上有一颗 128-Mbit Quad-SPI (QSPI) 的 NOR Flash,我们可以透过 Xilinx ISE 和 Vivado 等工具去将 Zynq Boot Image 下载到 QSPI Flash 上。

当下载完成后,照这样的步骤即可透过 QSPI 启动:

1. 接上电源,并设定好 JP7 (Power Source Select)

2. 将 JP5 的跳线 (Jumper) 调整到 QSPI 模式 (板上标示为 QSPI 的那个)

3. 启动电源。接下来 Zybo Board 就会从 QSPI 卡启动。

JTAG 启动

当你将 JP5 设定为 JTAG 启动模式,Zynq 内的 Cortex-A9 处理器会等到计算机端的 Xilinx 工具加载了要执行的程序之后,再执行预执行的程序,或是启用一步一步(step-by-step)的执行模式来方便我们除错。

除此之外,我们也可以透过 iMPACT 或是 Vivado Hardware Server 透过 JTAG 来设定可程序逻辑区块 (Programmable Logic, PL)。

Zybo Board 默认是开机启动 Cascaded JTAG 模式,在这种模式下 处理器系统 (Processing System, PS) 和 可程序逻辑区块 (Programmable Logic, PL) 可以透过同一个 JTAG 去进行控制。如果你将 JP6 短路,则可以让 JTAG 仅看得到 可程序逻辑区块 (Programmable Logic, PL),在这种状况下,使用者可以透过 EMIO (Extended multiplexed I/O) 将 PJTAG 拉出,让外部的设备可以和 处理器系统 (Processing System, PS) 进行沟通。

SPI Flash

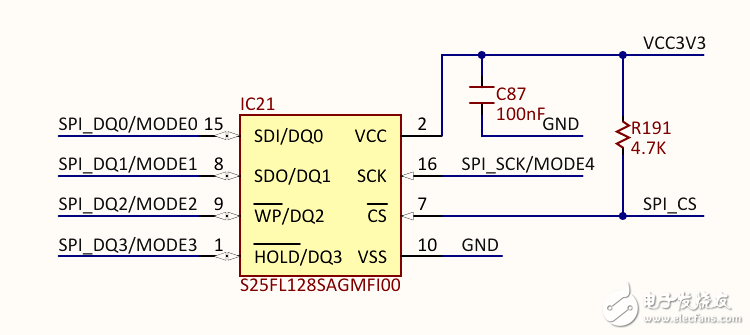

Zybo Board 内建了 4-bit SPI (QSPI) NOR Flash,硬件型号为 Spansion S25FL128S。

假设 JP5 设定为 NOR Flash 开机,则我们可以透过这颗 NOR Flash 来初始化处理器系统(Processing System, PS)以及可程序逻辑区块(Programmable Logic, PL)。除此之外,当开机完成后,我们可以使用 Spansion 文件系统(Spansion Flash File System, FFS) 来对档案进行读写的处理。

从电路图我们可以看到 SPI Flash 是直接连到 Zynq 处理器上的 Quad-I/O SPI interface。

DDR 内存

Zybo Board 使用的是 Micron MT41J128M16JT-125 或是 MT41K128M16JT-125 这两种 DDR3 内存组件,在 Zybo Board 上我们共有 512MB 的内存空间可以使用。

根据 Zynq-7000 All Programmable SoC Technical Reference Manual,DDR3 内存是直接连接到处理器系统 (Processing System, PS)。

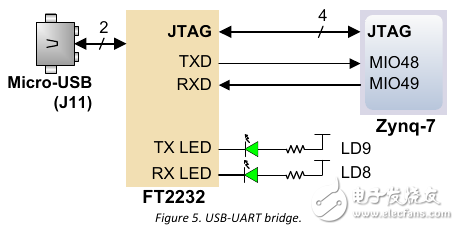

USB UART 接口

Zybo Board 并未将 UART 串行端口拉出,取而代之的它采用了 FTDI FT2232HQ 这款 USB 转 UART 的 IC 让你的计算机可以和 Zybo Board 进行沟通。

如果你是 Linux 使用者,在安装完 Vivado 后,你会需要手动安装 udev 设定好让 Linux 可以侦测到这个 USB 转 UART 设备(共两组,/dev/ttyUSB0, /dev/ttyUSB1),假设你的 vivado 安装在 /opt/Xilinx/Vivado/2016.1的话,我们可以透过以下程序来安装 udev 设定。

MicroSD 插槽

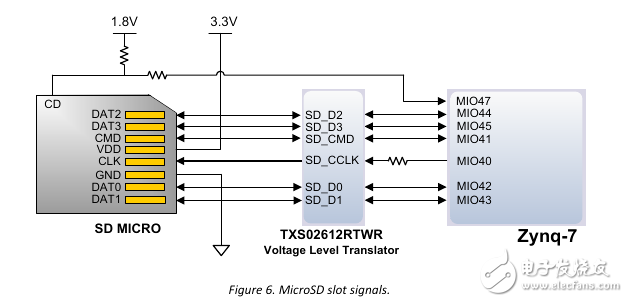

在 Zybo Board 的背面,我们可以看到 Micro SD 插槽(J4),根据 Zynq-7000 All Programmable SoC Technical Reference Manual ,Zynq 的 SDIO 控制器仅支持 1-bit 或是 4-bit 传输模式 (Host Modes),不支持 SPI 模式。

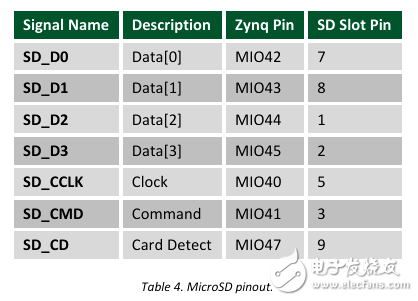

而 Micro SD 使用到的 MIO (Multiplexed I/O) 信息如下:

USB OTG

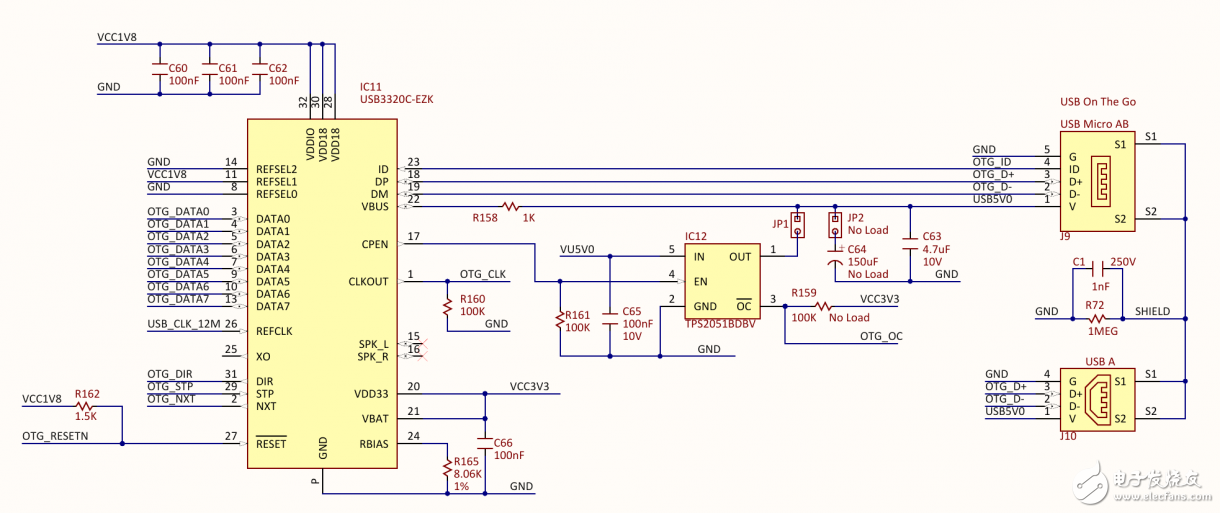

Zybo Board 提供了一组 USB OTG 支持,在这个界面中使用了 Microchip 的 USB3320 这颗 IC 来作为端口物理层 (Port Physical Layer, PHY),要注意到的是,你不可以 同时 将 USB 主机 (HOST) 以及 USB 设备 (Device) 接到 USB OTG 端口上。

(也就是不要同时接上设备到 J9 以及 J10)

而在 USB OTG 的功能上,我们则是用掉了 MIO 28 ~ 39 的位置。

另外,由于 USB 2.0 的规格是 USB 主机最多可以提供 500mA 的电流,当你设定为 USB 主机的模式时,在 J11的电源端 必须 改用外接电源或是电池输入,避免电流不够的情况发生。

Ethernet PHY

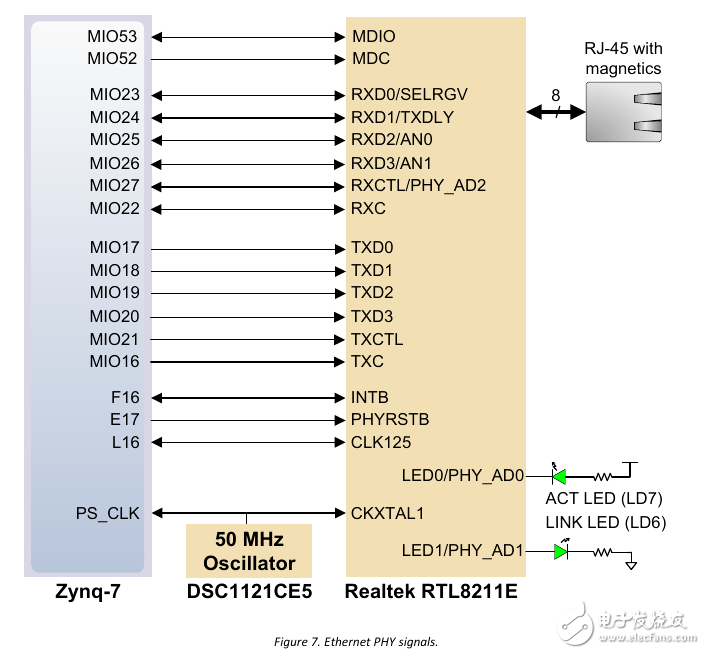

Zybo Board 使用 Realtek RTL8211E-VL PHY 来实现 10/100/1000 网络传输的功能。具体使用到的 MIO 以及 EMIO 接脚信息如下:

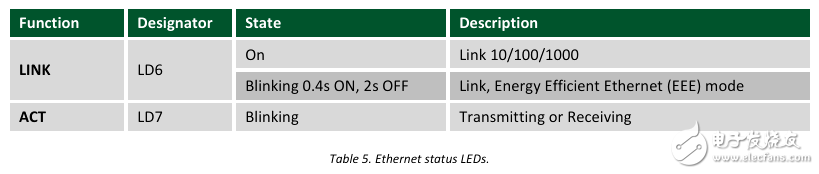

我们可以透过在 RJ45 附近的 LED 来观察流量 (LD7) 以及联机状态 (LD6) 的信息

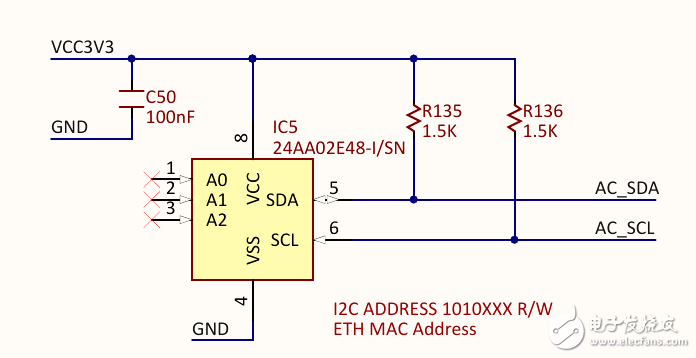

网卡的 MAC 地址则是存放在 Micrichip 24AA02E48 这颗 EEPROM 上面,Zynq 处理器透过 EMIO 上的 I?C 接口来和 EEPROM 进行沟通。

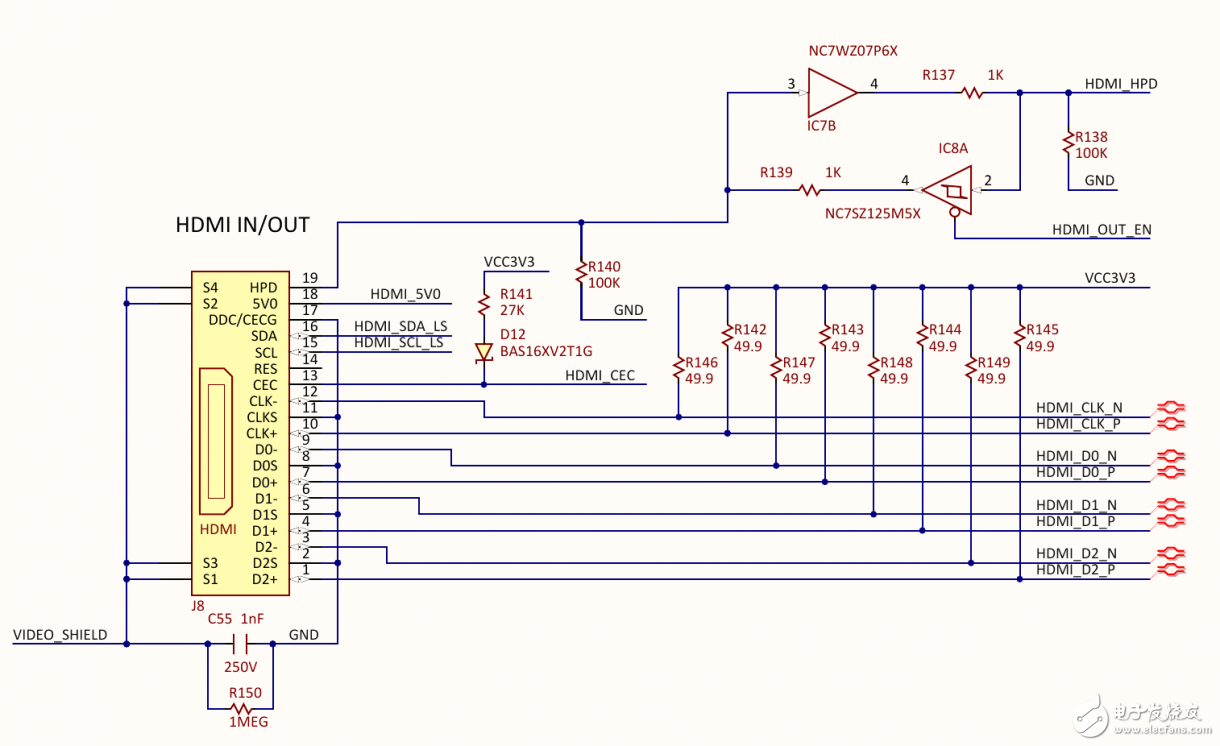

HDMI Source/Sink

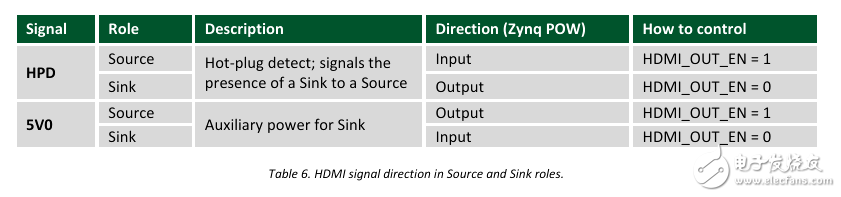

Zybo Board 的 HDMI 接口并未透过外部 IC 去驱动,因此我们必须透过可程序逻辑(Programmable Logic, PL) 去实现影片编码 (Encoding)与译码(Decoding)的功能。

由于 Zybo Board 的 HDMI 接口支持 HDMI 来源装置(HDMI Source) 以及 HDMI 目标装置 (HDMI Sink) 的功能,我们也须注意讯号的方向变化。

根据 ZYBO FPGA Board Reference Manual 可知 Zyboard Board 的 HDMI 至少支持到 720p (1280x720) 的分辨率。

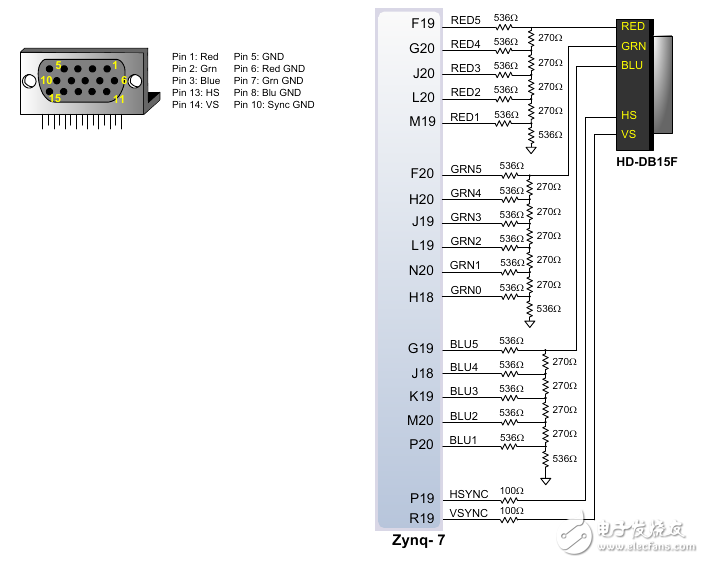

VGA

Zybo Board 的 VGA 输出也是没有透过外部 IC 将数字讯号转换为模拟讯号,取而代之的,它采用了 R–2R resistor ladder 这种分压的方式将数字讯号变成了 VGA 用的模拟讯号。

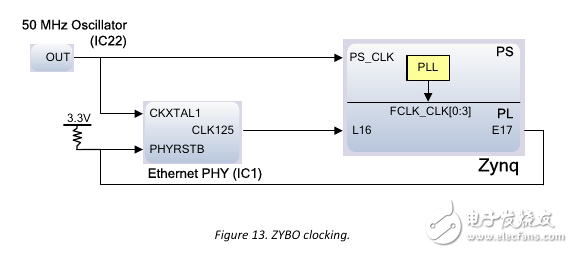

频率源 (Clock Sources)

ZYBO board 提供了 50MHZ 的频率到 Zynq 处理器的 PS_CLK 接脚,基本连接信息如下:

要注意到的一点是,由于 Ethernet PHY 会接收 50HMZ 频率输入,并输出 125HMZ 到 Zyna 处理器上,当 Ethernet PHY 重置(reset)的时候,CLK125 的输出会被取消。

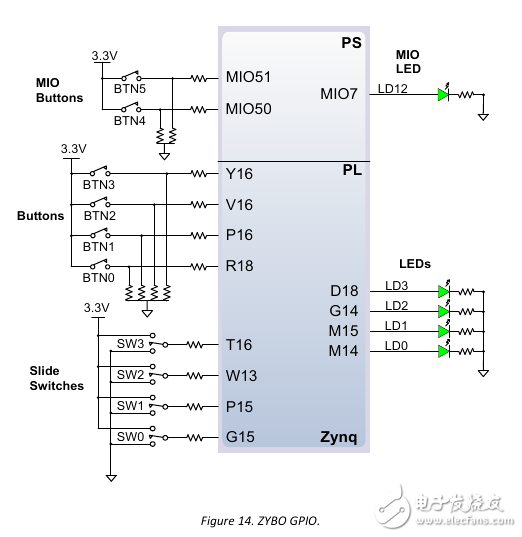

基本输入/输出 (I/O)

Zybo board 板上有一些预先定义好的 IO, 比如指拨开关 (Switch)、LED 灯、无段按钮等。

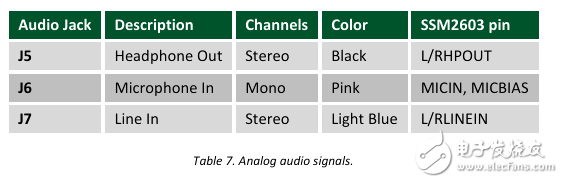

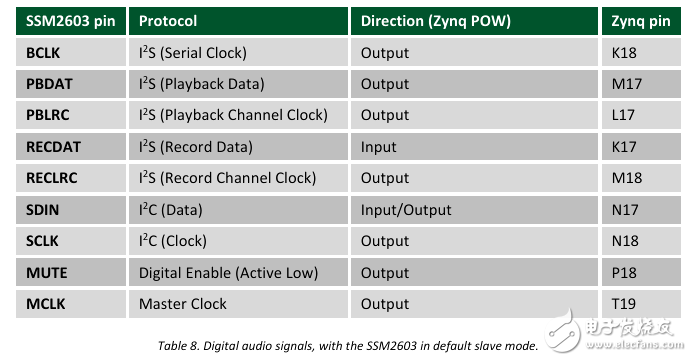

声音 (Audio)

Zybo Board 上有三组声音相关的 IO,分别是耳机孔输出(Headphone Out)、麦克风输入(Microphone In)、音源转录功能(Line In),这些 IO 会连接到 Ananlog Device 的 SSM2603 音频译码器上。

SSM2603 则是透过 I?C 接口来将数据传送给 Zynq 处理器去。

Pmod 接脚

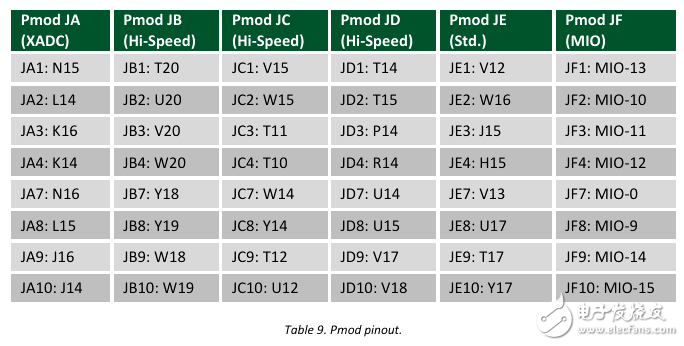

在 Zybo Board 的周遭,共有 6 个 2x6 母排座,用来将多余的 GPIO 拉出。每个 Pmod 提供了两个 3.3 VCC 电源、两个 GND 讯号以及 8 个 IO 可以用。在 Pmod 上的 VCC 以及 GND 最多可以提供到 1A 的电流(但要记得外接电源)。

不同的 Pmod 用途则可能不同,详情请参见下表:

延伸阅读

[1] ZYBO FPGA Board Reference Manual

[2] The Principles of FPGAs | FPGAs content from Electronic Design

[3] Zynq-7000 All Programmable SoC Technical Reference Manual

[4] Xilinx - Zynq Architecture

-

2008年第一季度全球手机出货量同比增17%2008-06-02 5417

-

SouVR 2009'3D/VR产品展示季[第一季]隆重开幕2009-03-09 4601

-

争做电子发烧友技术高手第一季第一周积分排名2012-12-10 6771

-

争做电子发烧友技术高手第一季第四周积分排名2013-01-04 8174

-

嵌入式开发从入门到精通视频教程(第一季):从零开始2013-05-02 216840

-

E计划第一季活动——直通黑马已全面启动,欢迎报名2014-08-22 3178

-

华秋开发者设计大赛第一季 - 电源设计大赛正式启动!!!2019-05-06 6554

-

【电源大赛】华秋开发者设计大赛第一季 - 电源设计大赛来了!!!2019-05-14 3427

-

2010年第一季10大智能3G手机排行(下)2010-01-19 1497

-

Zybo Board开发记录: 让 Vivado有Zybo Board的配置文件2017-02-08 854

-

第一季大尺寸面板出货相比去年同期成长6% 产值衰退10%2018-05-17 894

-

笔电面板全球供货紧张,预计第一季出货年减5.4%2020-03-02 3091

-

2020年第一季NAND Flash(闪存)位元出货量较前一季大致持平2020-06-19 2724

-

Chromebook出货顺,广达创下史上最佳第一季营收表现2021-04-13 2233

-

开放原子训练营第一季——铜锁探“密”圆满落幕!2023-05-23 1438

全部0条评论

快来发表一下你的评论吧 !