如何利用Vivado HLS处理许多位准确或任意精度数据类型

FPGA/ASIC技术

描述

我们在设计硬件时,它往往是要求更精确的位宽。例如,一个filter的输入是12位和一个累加器的结果只需要一个最大范围为27位。然而对于硬件设计来说,使用标准的C数据类型会造成硬件成本的浪费。这就会造成我们要使用更多的LUT和寄存器,延迟甚至可能超过时钟周期和需要更多的周期来计算结果。这往往不是我们需要的结果。因此下面我将介绍如何利用Vivado HLS处理许多位准确或任意精度数据类型,以及允许使用任何(任意)宽度的模型变量。

C-base 数据类型

我们从硬件的角度来看数据类型,采用C/C++的数据类型都是以8bit为边界,即:

? char (8-bit)

? short (16-bit)

? int (32-bit)

? long long (64-bit)

? float (32-bit)

? double (64-bit)

? 确切的宽度的整数类型如int16_t (16-bit) 和 int32_t (32-bit)

注意:char16_t和char32_t在Vivado Hls 中是不支持的

从上面发现,C的数据位宽是比较死板的,然而描述RTL里面的位宽是任意的。

例如,采用C语言去描述一个18*18 bits的乘法器,那么就需要将输入数据都声明为32 bits(int),结果声明为64 bits(long long),这将会在FPGA中消耗4个DSP48E1,显然这是很浪费资源的。

任意精度数据类型 Language Integer Data Type Required Header

C [u]int< W>(1024 bits) .#include< ap_cint.h>

C++ ap_[u]int< W>(1024 bits) .#include< ap_int.h>

C++ ap_[u]fixed< W,I,Q,O,N> .#include< ap_fixed.h>

其优点有:1.更高的时钟频率 2.更好的数据吞吐率 3.消耗资源更少

因此,使用任意精度数据类型能以更少的资源,获得相同的精度,同时可以运行在更高的时钟频率下。

注意:在声明任意数据类型的时候,我们往往在头文件里面声明,这会使得我们在做debug的时候会非常有用。

C-base 数据类型project

Step1 创建和打开project

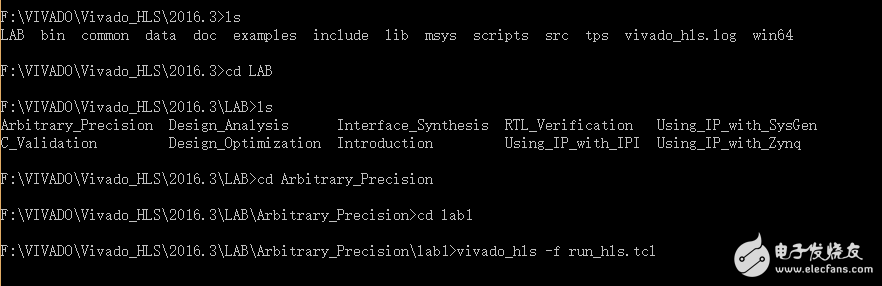

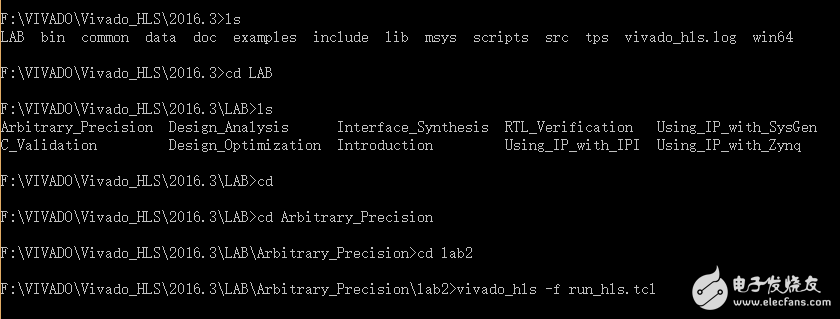

I.打开Vivado HLS Command Prompt,按照下图输入命令

II.输入vivado_hls -p window_fn_prj

Step2 Review Test Bench 和run C Simulation

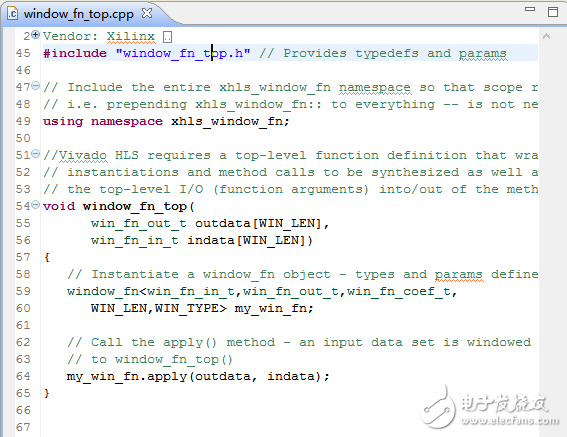

I.在Source打开window_fn_top.cpp

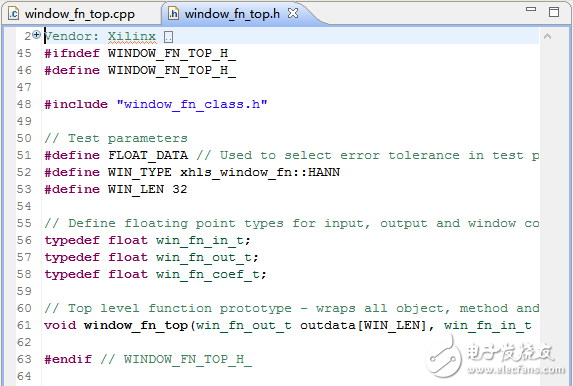

II.找到window_fn_top.h,按住Control键,并右击,打开window_fn_top.h(头文件)

在这里,我们可以看到,本设计所有数据类型的操作都是标准C/C++的浮点型。

III点击Run C Simulation

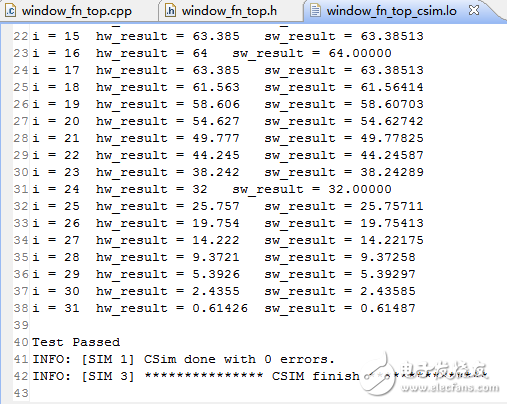

Step3 Run C Simulation 和 Review Results

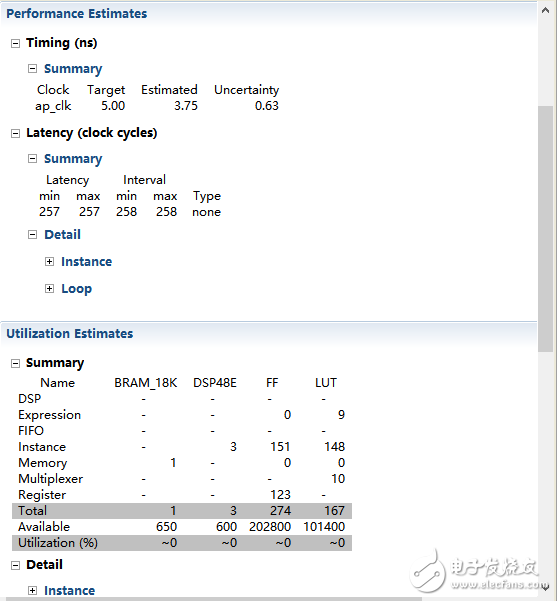

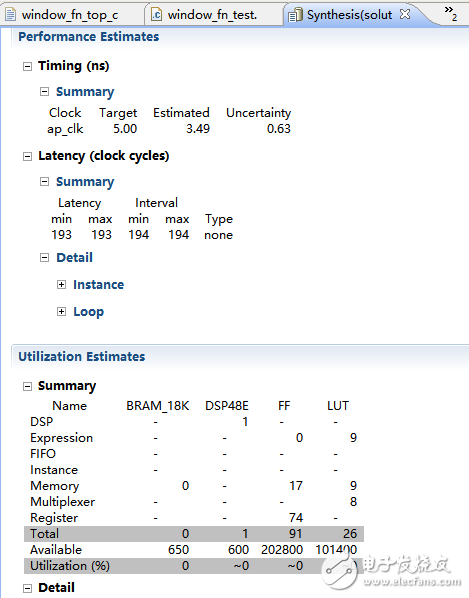

I.点击Run C Synthesis

图中我们发现,顶层中的instances占用了大部分资源。

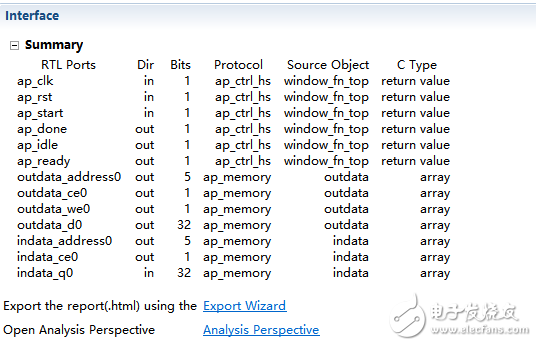

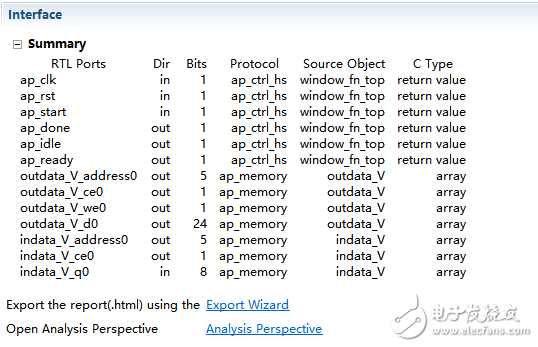

II.打开Interface Summary

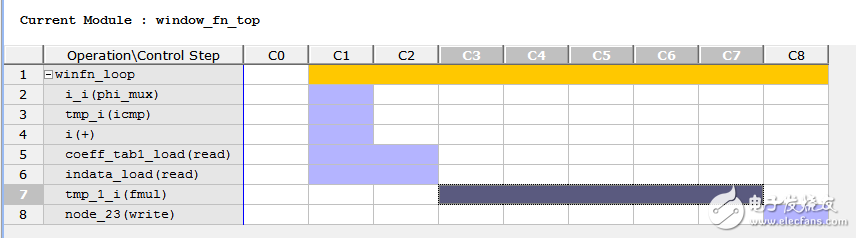

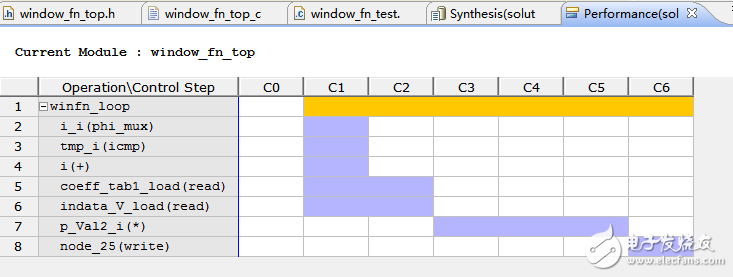

III.点击Analysis,打开winfn_loop

这是浮点型乘法器(fmul),图中可以看出,第一个状态是读取内存操作(两个周期),然后是fmul操作(五个周期),最后的操作状态是一个写内存操作(一个周期)

III.退出Vivado Hls,并返回到command prompt

任意数据类型project

Step1 创建和仿真project

I.打开Vivado HLS Command Prompt,按照下图输入命令

II.输入vivado_hls -p window_fn_prj

III.在Source打开window_fn_top.cpp

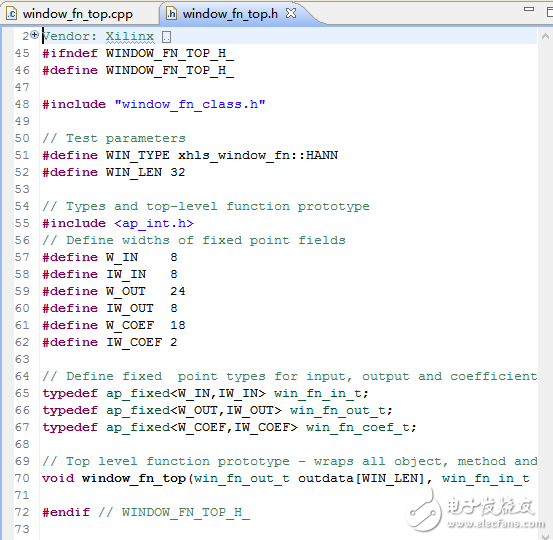

IV.找到window_fn_top.h,按住Control键,并右击,打开window_fn_top.h(头文件)

这里的数据类型的操作是ap_fixed点类型,它类似于float和double(因为它们支持整数和分数位表示的类型),window_fn_top.h是唯一不同于上一个project的头文件。这些数据类型是在头文件中定义的ap_fixed。

注意:你可以通过修改C代码,将任意精度类型代替标准C类型,在这里必须做的更改是减少数据类型的大小。在这例子中,我们使用8位,24位,和18位,而不是32位浮点类型。通过较少的操作,减少面积,和更少的时钟周期就可以完成project。我们也可以改变更常见的C类型(如int,short,和char),例如,更改数据类型(18位int(32位))可以确保只要一个dsp48就可以执行任何乘法,但是你必须确认设计仍然执行正确的操作和它这样做所需的精度。由VIvado Hls提供的任意精度类型的好处是,可以仿真更新的C代码来确认其功能和准确性。

V.点击Run C Simulation

控制台面板显示了C仿真的结果。随着数据类型的更新,结果不再跟预期结果相同,然而他们是在误差范围内。

Step2 Run C Synthesize和 Review Results

I.点击Run C Synthesis

注意:通过使用任意精度类型,已经减少了延迟和面积(50%和80%),并简化了RTL硬件的操作。由于memory中的总位小于1024 bit,所以现在是自动执行LUTs和FFS而不是模块RAM。

II.打开Interface Summary

注意:现在的数据端口是8 bits和24 bits

III.点击Analysis,打开winfn_loop

总结

本文介绍任意精度数据类型的处理方法。通过Vivado HLs中两个project的比较,得到结论,跟C-base 数据类型相比,使用任意精度数据类型能以更少的资源,获得相同的精度,同时可以运行在更高的时钟频率下。

- 相关推荐

- 热点推荐

- Vivado

-

oracle的数据类型有哪些2023-12-05 3968

-

基本数据类型分享2023-06-13 13506

-

PLC数据类型2023-04-17 999

-

Vivado HLS实现OpenCV图像处理的设计流程与分析2021-07-08 5333

-

Vivado HLS中常见的接口类型2020-12-26 9044

-

探索Vivado HLS设计流,Vivado HLS高层次综合设计2020-12-21 4643

-

关于Vivado HLS错误理解2019-07-29 6321

-

一篇文章看懂HLS中的数据类型2018-12-12 17818

-

如何使用Tcl命令语言让Vivado HLS运作2018-11-20 3834

-

利用Vivado HLS加速运行慢的软件2017-02-09 532

-

HLS系列– HLS中的数据类型12017-02-08 1307

-

C++中常用的复合数据类型在Vivado Hls中的应用方法2017-02-07 2447

全部0条评论

快来发表一下你的评论吧 !